最近介绍的 60V/0.5A~5A 非同步高压 Buck 转换器 RT(Q)636x 系列(供工业和商业系统使用)和 RTQ296x-QA 系列(供车用系统使用)都具有时钟信号外同步的功能,当时的文章是这样来提及此问题的:

“ 使用外部时钟对 RTQ6363 进行同步控制

前文已经说过可用一只电阻对 RTQ6363 的工作频率进行设定,这只电阻需要连接在 RT/SYNC 和 GND 之间。如果需要让 RTQ6363 的开关动作和外部时钟信号同步,可以将该时钟信号输入 RT/SYNC 端,但是要求该时钟信号的频率必须高于连接在 RT/SYNC 和 GND 之间的电阻所设定的工作频率且介于 300kHz~2.2MHz 之间,而且该时钟信号的正脉冲宽度必须大于 20ns,其低电平部分的电压必须低于 0.5V 、高电平部分的电压必须高于 2V 而低于 6V。在接入外部时钟信号后,上桥开关导通的触发信号将来源于该时钟信号的下降沿,但是否导通及其导通时间将取决于回路控制本身的需要。”

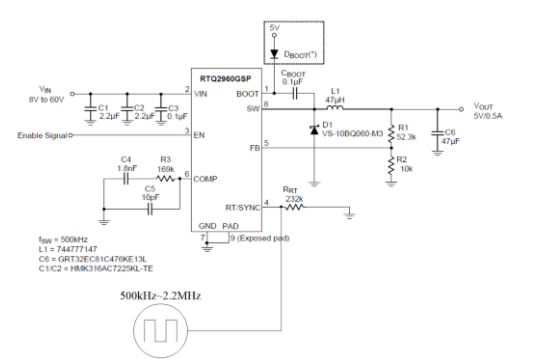

假如我们要同步控制的对象是 RTQ2960-QA(其功能从本质上和 RTQ6363 是一样的),提供外部时钟的系统和它的连接关系可以如下图所示:

由于图中由 RRT 设定的 RTQ2960 的工作频率为 500kHz,外部接入的时钟信号的频率便必须高于 500kHz,所以我给这个时钟源设定的频率范围便是 500kHz~2.2MHz,总之其数据必须高于 RTQ2960 本身的工作频率,否则想实现同步的目的便不能实现。

有读者留言询问在什么情形下需要使用外同步,对这个问题的答案我是没有什么实际经验的,因为从未经历过,有过的仅仅是思考,即完全是从理论的角度出发进行的推理,下面就把这些思考后的几个答案提供给读者参考。

第一种,你需要在系统工作的过程中改变 RTQ2960 的工作频率,其意义可能是要避免 DC/DC 的工作频率对其他系统的工作发生影响。例如,当你把 RTQ2960 和一个广播接收机放在一起工作的时候,虽然 RTQ2960 已经有扩频工作模式可以降低其开关工作频率对广播频段带来的影响,这种扩频模式可以像一个经过严格训练的枪手一样让射出的子弹均匀分布在一片目标区域,绝对不像电视剧里的狙击高手一样能让所有的子弹都穿过同一个位置,却以另外一种规律体现其作为高手的能力,从而能将电磁辐射功率均匀分布在一段频带上而不是在一个频点上无限累加,但是你在实用中还是发现存在相同频段的干扰问题,这时候就可以使用一个由 CPU 控制的时钟信号发生器来控制 RTQ2960 的工作频率,使这个频率及其倍频都远离你的广播接收系统的接收频率,甚至可以使它远高于你使用的广播频段,因为中波调幅广播的频段都在低于或等于 1710kHz 的地方,而 RTQ2960 的外同步工作频率最高可达 2.2MHz。如果你使用的是调频广播接收系统,这种系统的最低工作频率也有 64MHz(俄罗斯的数据,我国的是 87MHz),这时就可以将 RTQ2960 的工作频率设定到尽可能低的地方如 300kHz 以减轻其高次倍频对调频频段的影响。

第二种情形,你可能在使用 RTQ2960 的时候既想利用其低频工作开关损耗低的特性,又想利用其高频工作输出电压纹波低的特性,这时候就可以根据不同的情况灵活调整外部同步时钟的信号频率,从而在适当的时候得到自己想要的特性。

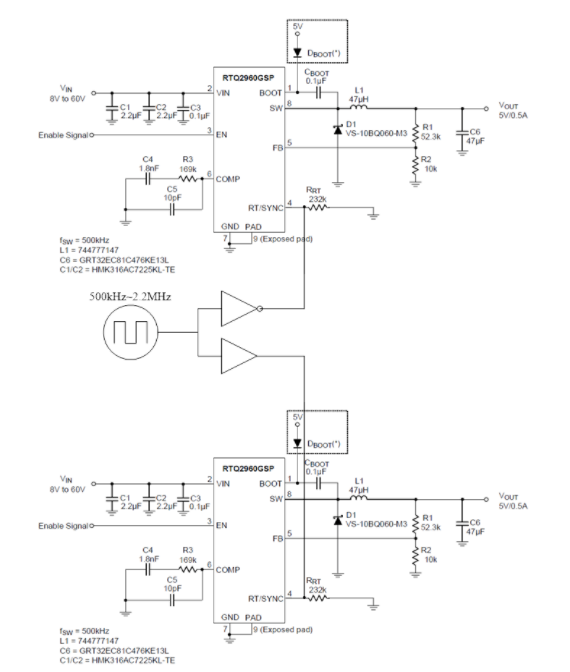

第三种情形,你使用多颗 RTQ296x 系列的器件来为你的系统供电,但是你发现为它们供电的电源上存在较大的低频纹波,而这种纹波居然与各个 RTQ296x 的工作频率之间的差拍有关,因为不同的 RTQ296x 因为以各自不同的节奏工作,这时候便在一些时段出现了电流输入脉冲的相互叠加,又有一些时段里的电流脉冲是分时出现的,前者便形成较大的输入电流尖峰,后者的输入电流则比较平坦,当供电源内阻低的时候其影响还比较小,当供电源内阻比较大时,输入电压的纹波也比较大了,这时候就可以考虑使用统一的时钟来同步各个 RTQ296x 的工作节奏,使它们能够分别在不同的时隙从供电电源取电,就像我们曾经介绍过的多相 Buck 转换器那样工作,这样便可以取得最均衡的效果,使对供电电源的要求最低化,而各个 RTQ296x 的工作效果以及它们之间的相互影响也最小化了。

在上图所示的电路中,我将同一个时钟信号分别通过一个反相器和一个缓冲器以后引入两个 RTQ2960 的 SYNC 端,假如原始的时钟信号正好是占空比为 50% 的方波,反相器和缓冲器导致的时延也都相同,则这两颗 RTQ2960 所得到的时钟信号便是刚好相差 180 度,这将导致这两颗 RTQ2960 的上桥开关的导通开始时间也刚好相差 180 度。经过这样的处理,这两颗 RTQ2960 因为工作而带来的输入电流就被均匀地分散开了,与它们各自的负载特性一点关系都没有,由此导致的输入电压纹波也是最小的,成功达成了最初想要达成的目标。

如果上述的两相工作还不能满足你的需求,你自然可以设计出其他的分频系统来构成更多的分相工作机制,直至满足你的需求为止。由于实际的应用总是千差万别的,你的实际系统可能会有不同的需求,你完全可以在这些需求的基础上去设计自己想要的东西,只要不违背基本的物理原理便好。当有了全新的设计以后,各个单元电路的元件参数通常需要重新考虑,你需要从最坏的情况入手去进行计算,以便最后得到的东西能满足所有条件下的要求。

编辑:hfy

-

缓冲器

+关注

关注

6文章

1566浏览量

44876 -

反相器

+关注

关注

6文章

240浏览量

42704 -

时钟信号

+关注

关注

4文章

372浏览量

28060

发布评论请先 登录

相关推荐

请问下位机与上位机如何保持时钟同步呢?

网络时钟同步有哪些要求?如何在5G网络中测试时间与时钟同步?

什么是网络时钟同步?为什么它对5G网络至关重要?

ADIS16488在使用外部同步时钟时,可以使用FIR吗?

ADE7913_1将CLKOUT输出到ADE7913_2的XTAL1,如何进行同步?

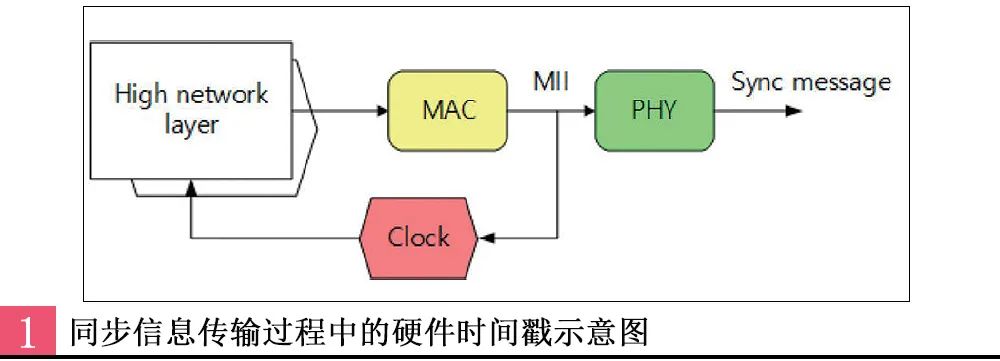

一种实现多通道无压缩IP流PTP时钟精准校时分析的方法

多线程不进行同步会造成什么问题

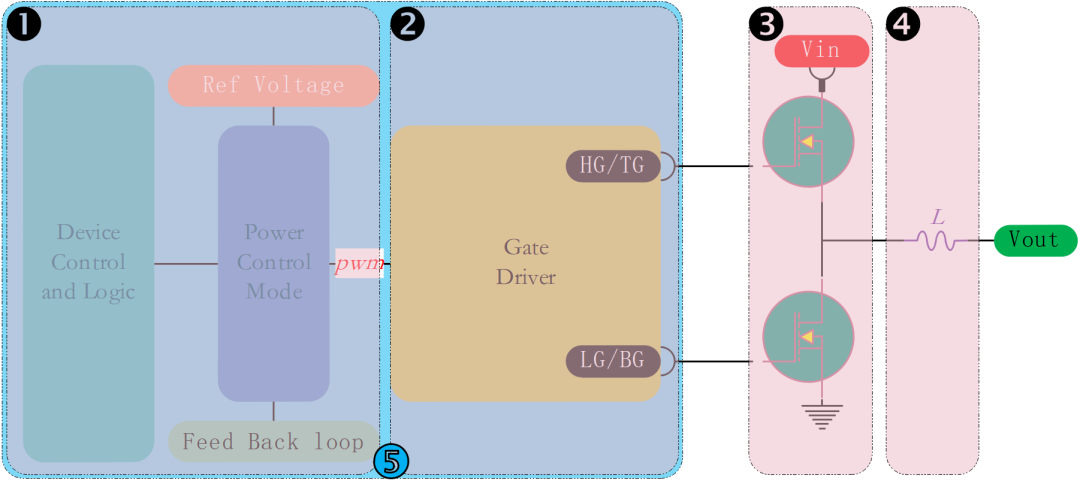

外部电源开关同步降压控制器的拓扑结构

对于多位的异步信号如何进行同步呢?

基于RTQ7860的USB PD车载快充方案

使用外部时钟对 RTQ6363 进行同步控制

使用外部时钟对 RTQ6363 进行同步控制

评论