埋容设计仿真案例

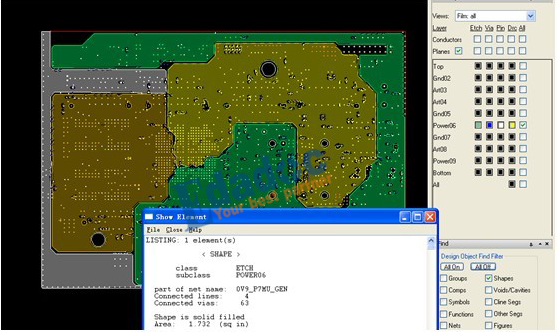

下面介绍一个埋容的PCB设计仿真的案例:主芯片是一个专有芯片,带来的特点就是模型和资料没有大厂芯片(如Intel,Broadcom等)那么完善,既没有直接完整可用的Ibis模型,也没有明确提示板级电源供电网络(PDN)设计所需要考虑的频率范围。这样就给后续的设计和仿真评估带来很大的困难。原始设计如图六所示,十层板,5、6层之间电源地耦合,形成平板间电容。

图六 原始设计

板间电容计算

首先估算一下平板间的电容量,平板面积如图六所示,这时候忽略打孔对平面面积的影响。把这个面积代入图一的公式,普通材料介电常数4.2,层间距离4mil左右,这时候平板间电容量为0.409nF。如果使用3M的C ply材料,介电常数为16,层间距离为0.56mil,这时候平板间电容量为11.13nF。以上计算可知,专用埋容材料增加平板间电容量的效果是很明显的。

但是如之前说的,这个计算是忽略打孔对平面面积的影响,实际情况比较复杂,单纯用这个数据来指导埋容设计是不全面的。

板间电容作用仿真

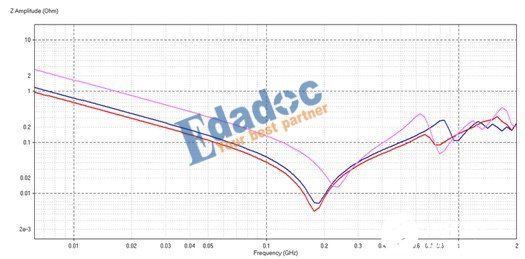

不加电容,看埋容平面大小对谐振频率的影响,仿真3种不同的平面大小。

图七 埋容平面大小对谐振频率的影响

仿真结果如图,粉红色的是埋容面积最小的,蓝色的是埋容面积稍大的,红色的是埋容面积最大的。可以看出埋容面积变大之后,平面谐振向低频偏移,同时也可以看到高频的共振点也降低了。

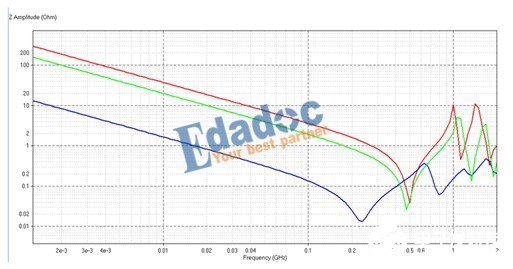

看平面谐振点的变化,同时考量低频段(《100M),有埋容和没有埋容的区别

A 电源地间距28.31mil,电源地不耦合时,波形为红色

B 电源地间距4.2mil,电源地耦合时,波形为绿色

C 使用埋容材料3M_C Ply,间距0.56mil,波形为蓝色

从仿真结果可以看到,随着电源地之间的间距减小,加入埋容材料,平面谐振点向低频偏移,同时低频的阻抗也大幅降低,这个频段埋容材料的作用也非常明显。

图八 平面谐振点

只加0.1u的电容12个,观察电容与埋容形成的谐振,同时观察埋容之后,减小了安装电感对电容性能的影响,考察同样数量电容,阻抗曲线带来的改善,考察同样的阻抗性能,可以减少多少电容……

下图中蓝色的是使用了埋容材料后的阻抗曲线,红色的是没有使用埋容材料的阻抗曲线。可以看到埋容的谐振点在266M,与0.1u电容形成的反谐振在177M。同时注意到在10M附近有两个谐振点,这是因为0.1u的电容有6个在芯片附近,而有10个在VRM端,距离芯片较远,说明电容布局位置也有影响。

图九 电容与埋容形成的谐

PDN综合仿真

目前的埋容仿真项目总结,正常设计全系列电容,同样考察电容与埋容形成的谐振,主要考量以下几个目标:

● FR4板材使用正常的电容组合达到的效果

● 使用埋容后效果怎么样

● 电容可以减少到多少使与FR4的效果是一样的

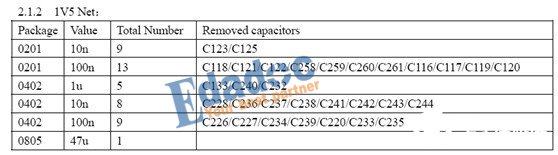

以1V5为例

● 0201的10n电容9个

● 0201的100n电容13个

● 0402的1u电容5个

● 0402的10n电容8个

● 0402的100n电容9个

● 0805的47u电容1个

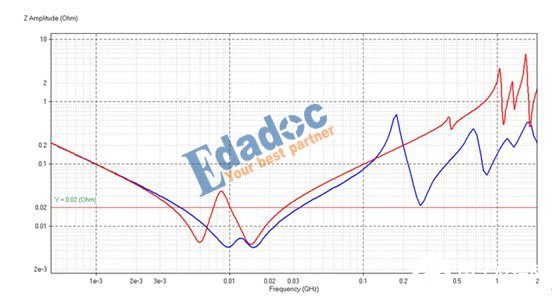

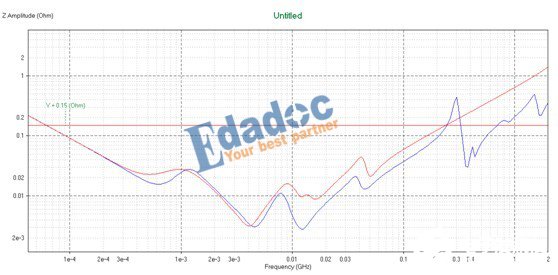

下图中红色的曲线是使用普通板材FR4的阻抗曲线,而蓝色的曲线是使用3M-Cply埋容材料后的阻抗曲线

图十 使用埋容,没有删除电容的PDN曲线

可以看到埋容对PDN从低频开始到高频都产生效果,这时候去除70%电容,如下表所示:

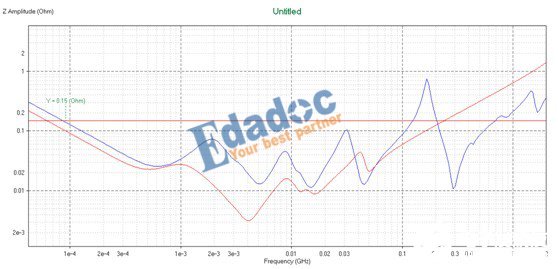

可以看出其中红色是使用了3M-Cply埋容材料并且去掉31个电容后的阻抗曲线。蓝色的是使用普通FR4的阻抗曲线。也就是去掉31个电容后使用埋容材料的阻抗曲线,在高频段比使用FR4的阻抗曲线好,在低频段稍高一点,也能满足目标阻抗的要求,不过在100多兆有一个共振点。

图十一使用埋容,删除70%电容的PDN曲线

也就是说,埋容的PCB设计不是加入埋容材料就万事大吉(欠设计),也不是即用了埋容,同时原来该怎么放电容还怎么放电容(过设计),一个完善准确的PDN仿真有助于准确达到设计要求。

编辑:hfy

-

阻抗

+关注

关注

17文章

893浏览量

45371 -

PCB设计

+关注

关注

392文章

4572浏览量

83232 -

PDN

+关注

关注

0文章

71浏览量

22575

发布评论请先 登录

相关推荐

埋容的PCB设计与PI仿真 一

[原创]Allegro高速PCB设计技巧视频--PCB设计必备免费分享

PCB设计的ESD抑止准则解析

Cadence PCB设计仿真技术

减少谐波失真的PCB设计方法

埋容的PCB设计仿真的案例解析

埋容的PCB设计仿真的案例解析

评论