布局布线

1

布局

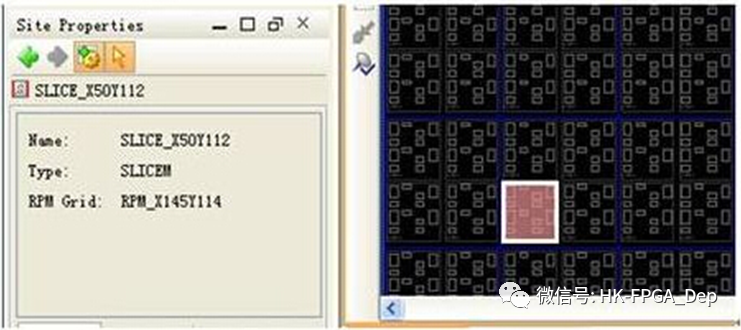

我们前面做的那些设计流程得到的LUT门级网表就好比一个购物清单,即LUT门级网表。网表里提供的仅仅是从逻辑关系上一些LUT结构的连接。我们需要将这些LUT结构配置到FPGA具体的哪个位置。需要说明的是,FPGA里任何硬件结构都是按照横纵坐标进行标定的,图中选中的是一个SLICE,SLICE里面存放着表和其他结构,它的位置在X50Y112上。不同的资源的坐标不一样,但是坐标的零点是公用的。

在FPGA里布局需要考虑的问题是,如何将这些已有的逻辑上连接的LUT及其它元素合理的放到现有的FPGA里,达到功能要求的时候保证质量。具体点就比如,乘法器这样的电路适合放在RAM附近,当然,硬件乘法器的硬件布局一般也是在存储器附近,有利于缩短乘法的延时时间,什么样的电路需要配置高速等等。 十万公顷的地布局规划好了,农产品就会有很好的丰收,同样FPGA开发布局布好了,由FPGA搭建起来的电路就会更加稳定和扩展性。

2

布线

我们在FPGA内通过布局,知道那些LUT具体分布到哪个SLICE,但是一方面如何让这些SLICE连接起来,二方面如何让输入的信号到达相应的开始处理点和如何让输出到达输出IO上,并且连接的电路整体性能好,这就是布线这个环节需要完成的内容。要达到布线最优话,当然这里面设计到布线算法和很多细节问题,比如涉及到布线资源、PLL资源分布。但是这些对我们理解布线这个概念没有很多益处,暂且不深入,本质上就是一个线路求最优的问题。

约束

constraint

约束,在综合和布局布线这两个流程环节里都出现了,我们暂且规定其为约束一和约束二,或者说综合约束和布局布线约束,布局布线约束又可以分为位置约束、时序约束。 约束,就是对这些环节操作定制规则。一般开发环境会对这些约束有个默认,这些默认的设置对大部分情况下还是适用的,但是通常布局布线约束中的I/O约束是我们每一个工程都必须给定的。同时开发工具开放其他约束接口,允许我们设置这些规则,具体的有哪些约束怎么去做在后面介绍工具使用的时候进行讨论,这里先明白这些约束的基本概念。

01

综合约束

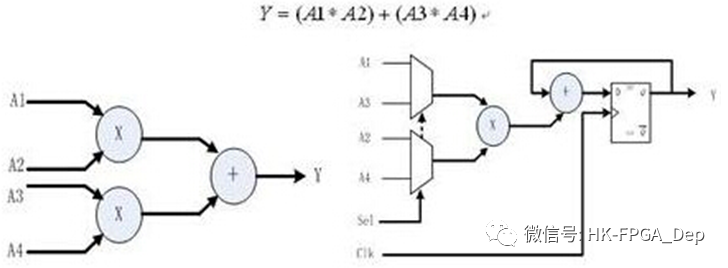

相信大家已经下意识的将综合约束和综合过程挂在一起了,没错,综合约束确实是在综合过程中做的,用来指导综合过程,包括编译和映射。我们已经知道综合过程是将RTL级电路描述转换到FPGA上的硬件单元(LUT)中,形成以FPGA存在的硬件单元构成的电路。 我们还是拿前面有过的例子来说明,不同的约束将导致生成性能不同的电路。综合这么一个电路,没有加资源共享得到的电路如下图左边所示的电路,而加了资源共享的约束后,得到的电路结构如下图右边的电路。

通过之前的分析,得到左边的电路结构资源消耗多但是速度快,而右边的结构消耗资源少,但是速度慢,乘法器需要分时复用。 当然这只是一个例子,但是足以说明,不同的综合指导原则也就是综合约束,将会产生不同的电路。当得到的电路性能不能满足需求的时候,适当考虑综合约束,来达到一个速度和面积的转换的效果,实现性能的提升。电路实现的速度和消耗的面积是贯穿在FPGA开发过程中两个 矛盾的问题,综合约束是其中一种小范围内实现速度和面见平衡点移动的方式。

02

位置约束

位置约束和布局有关系,它就是指布局的策略。根据所选择的FPGA平台现有硬件资源分布来决定我们布局。 其中最典型的位置约束就是I/O约束。一个典型的系统是既有输入也有输出的,而不管是输入还是输出,都是从I/O上为端点的。输入从哪个端点进来,输出从哪个端点出去,输入是需要支持什么样的电气特性的端点,输出又是需要支持什么样的电气特定的端点。这些都是I/O约束做的事情。任何一个工程,都必须有这么一个约束。 还有一种典型的位置约束是在增量编译里涉及的物理界定。增量编译的出现就是因为在FPGA开发过程中综合和布局布线的长耗时性而提出的。思想就是把FPGA切成很多个小块的FPGA,然后约定具体哪块小FPGA放置什么模块,实现什么样的功能,从物理上进行界定。当修改工程后,开发平台就会检测哪些小FPGA内没有进行修改,哪些进行了修改,然后将修改过的部分重新进行综合布局布线步骤。这样一来,相比原来修改一点,全工程重新经过那些过程来讲,时间节省下来了。

03

时序约束

估计没有多少悬念了,时序约束很大程度上和布线有关。为什么要做这个约束? 由于一方面信号在芯片内传递是需要消耗时间的,另一方面大量存在的寄存器有反应时间,而我们开发的最开始的时候这些时间都是理想化的。但是考虑到真实情况下,如果跑的速度比较高,达到了200M这么个速度,当然这个高速和具体的芯片有关,高性能的芯片本身跑的速度可以达到很高,200M相对来说就不是高速,对一些低性能芯片还可能达不到200M。这个时候,这些时间达到了同样一个系统时间数量级的时候,很可能影响电路的性能了。某一刻,该来的信号没有来,默认的话就会采集错误信号了。 为了让这些硬件本身带来的延时时间更理想化,我们就要对这些决定时间延时的因素优化来减少时间延时。

对于寄存器本身的反应时间这个因素我们开发者是无能为力的,我们要做的优化就是布线了。是走直线还是走其他,不仅仅决定于自身这条路径,还和整个系统布线有关,好比水桶原理,系统性能决定于最差路径延时。 时序约束做的就是这些事情,但是时序约束并不是指具体去连接每一条线,这个工作就像前面那些流程一样都是由软件去实现的,先用软件自己默认原则布线,然后对其结果分析,不满足时序要求的,我们再对具体的问题路径做一些指导约束。时序约束的添加,主要包括周期约束、输入偏移约束和输出偏移约束。具体的过程在后面章节介绍工具使用时会有具体动手的指导。

原文标题:详解FPGA开发设计之布局布线&约束

文章出处:【微信公众号:FPGA技术支持】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

FPGA

+关注

关注

1602文章

21320浏览量

593158 -

电路

+关注

关注

170文章

5482浏览量

169543 -

布线

+关注

关注

9文章

730浏览量

84020 -

LUT

+关注

关注

0文章

49浏览量

12396

原文标题:详解FPGA开发设计之布局布线&约束

文章出处:【微信号:HK-FPGA_Dep,微信公众号:FPGA技术支持】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA布局布线优化技术

如何解决FPGA布局布线的拥塞问题呢?有哪些方法?

FPGA布局布线的可行性 FPGA布局布线失败怎么办

FPGA的布局布线

FPGA的布局布线

评论