虽然不少人对高速可能有了一点概念性的认识,但往往难以想象在所谓的“高速”情况下,会真正给实际的电路系统带来什么样的后果,这里我举几个实际的案例来剖析一下高速给PCB设计带来的一系列问题。

A.某公司早期开发的一个产品,一直工作良好,可是最近生产出来的一批却总是毛病不断,受到许多客户的抱怨。可是根本没有对设计进行任何变动,连使用的芯片也是同一型号的,原因是什么呢?

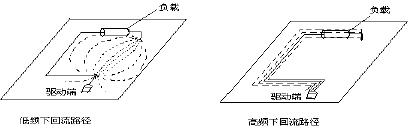

B.某个PCB工程师Layout经验非常丰富,设计的产品很少出过问题,但最近设计了一块PCB板,却发现了EMC检测不合格的问题,改变布线也毫无效果,但以前类似的板子却没有这样的问题。C.一个专业的内存模块设计工程师,从EDO内存到SDRAM的PC66,PC100,设计过很多项目,很少出现问题,可是自从内存时钟频率上到133MHz以上时,几乎很少有设计能一次性通过的。简单分析一下上面的几个案例,A的情况是由于芯片的工艺改进造成的,虽然所使用的芯片基本电路功能一样,但随着的IC制造工艺水平的提高,信号的上升沿变快了,于是出现了反射、串扰等信号不完整的问题,从而导致突然失效;B例子中,通过细致地检测,最终发现是PCB板上有两个并排平行放置的电感元件,所以产生了较为严重的EMI;

C中的内存设计师则是因为忽视了严格的拓补结构要求,在频率提高、时序要求更严格的情况下,非单调性和时钟偏移等问题造成了设计的内存模块无法启动。除了以上提到的三个实例,还有很多其他的问题,比如因为电容设计不当导致电源电压不稳而无法工作,数模接地不正确产生的干扰太严重使得系统不稳定等等。

随着电子技术的不断发展,类似于以上的各种问题层出不穷,而且可以预见,今后还会出现更多的这样或那样的问题。所以,了解信号完整性理论,进而指导和验证高速PCB的设计是一件刻不容缓的事情。

传统的PCB设计一般经过原理图设计、布局、布线、优化等四个主要步骤,由于缺乏高速分析和仿真指导,信号的质量无法得到保证,而且大部分问题必须等到制板测试后才能发现,这大大降低了设计的效率,提高了成本,显然在激烈的市场竞争下,这种设计方法是很不利的。于是,针对高速PCB设计,业界提出了一种新的设计思路,称为“自上而下”的设计方法,这是一种建立在实时仿真基础上优化的高效设计流程,见图1-1-1:从上面的流程图可以看到,高速的PCB设计在完成之前,经过多方面的仿真、分析和优化,避免了绝大部分可能产生的问题,如果依托强大的EDA仿真工具,基本上能实现“设计即正确”目的。

在整个高速设计过程中,信号完整性工程师必须贯穿于设计的始终,Cadence公司的首席顾问DonaldTelian曾给信号完整性工程师归纳了七点作用:

研究和定义(pioneeringanddefining)

分类和总结(Partitioning和Approximating)

建模和测量(ModelingandMeasuring)

设计和优化(Designingandoptimizing)

量化和验证(Quantifyingandverifying)

减少和简化(Reducingandsimplifying)

联系和调试(CorrelatingandDebugging)

对于以上这七大作用的详细阐述,可以参见1997high-performancesystemDesignConference上DonaldTelian的原稿。

-

内存

+关注

关注

8文章

2767浏览量

72756 -

PCB设计

+关注

关注

392文章

4572浏览量

83222 -

信号完整性

+关注

关注

65文章

1337浏览量

94916 -

emc

+关注

关注

165文章

3644浏览量

181158 -

华秋DFM

+关注

关注

20文章

3483浏览量

3907

发布评论请先 登录

相关推荐

高速PCB设计经验与体会

高速PCB设计之Allegro实战解答,教你如何玩转PCB设计!

Cadence高速PCB设计

高速PCB设计误区与对策

高速给PCB设计会带来什么影响

高速给PCB设计会带来什么影响

评论