SD存储卡接口定义了两种通信模式,SD模式和SPI模式。分析了SD传输协议后,给出了一种SD模式设备接口的设计方案。该设计能够自动解析主机发送的命令并响应,与Flash控制器相连后可以对Flash进行读写操作。为了解决数据存取的时序问题,使用了数据缓存技术。FPGA验证表明,该接口能够被电脑识别为SD卡,达到了设计目标。

1、引言

SD卡(Secure Digital Card)是“安全数码存储卡”的简称,于1999年8月由美国SanDisk公司、日本东芝和松下公司共同开发研制成功。随着数码产品的广泛使用,目前SD卡已经成为消费数码产品设备中最广泛的一种存储卡。在手机中,大量的安全增值业务设计就是通过SD接口实现的。SD物理层规范定义了两种可选择的通信协议:SD模式和SPI模式。

本文在研究了SD物理层规范的基础上,实现SD设备接口SD模式的前端设计,并进行了FPGA原型验证。

2、SD存储卡接口SD模式介绍的书写规则

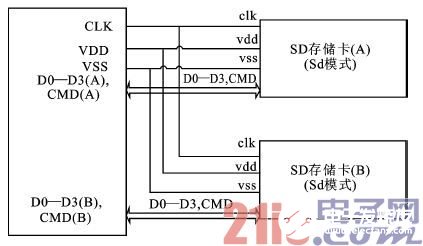

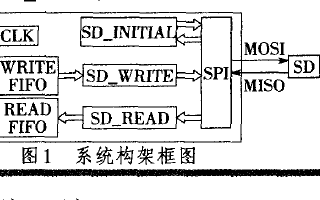

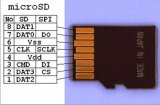

SD卡与控制器之间通过以下9线连接:时钟CLK、命令CMD、数据D0~D3、电源VDD和两根地线VSS。其总线拓扑结构如图1所示。命令和响应在CMD线上传输,数据在D0(标准总线模式)或D0~D3(宽总线模式)线上传输。

SD卡的所有命令都是6字节长度。一个命令总是以起始位(0)开始,后跟传输方向位(1),接下是6位命令索引,然后是32位命令参数,CRC7校验位,结束位(1)。SD的响应分为R1、R1b、R2、R3、R6、R7六种,其中R1、R1b、R3、R6、R7为6字节长度。R2为17字节长度,用于读取SD卡的CID/CSD寄存器内容。一个响应总是以起始位(0)开始,后跟一个传输方向位(0)。除了R3响应类型,所有的响应都有CRC保护。以一个结束位(1)结束。SD数据传输以块为单位,每个块总是由数据起始位(0)、数据位、CRC16校验位和数据结束位(1)组成。

图1 SD卡SD模式的总线拓扑结构

3、整体设计架构

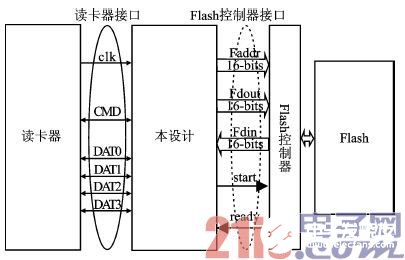

本设计的一端为SD存储卡标准接口,与读卡器连接。为了使接口有通用性,另一端与Flash控制器连接,从而达到与不同型号Flash连接的目的。本设计是连接读卡器和Flash控制器的一个中间模块。能够对读卡器发送的命令进行解析并响应,通过Flash控制器对Flash进行读写操作。整体设计方案如图2所示。

图2 设计方案

4、 结构设计

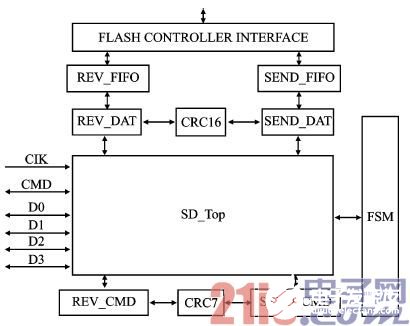

根据SD接口功能,将其进行详细的划分,由以下几个部分组成:命令收发模块,数据收发模块,状态控制模块和校验模块。SD模块结构如图3所示。

4.1 命令收发模块

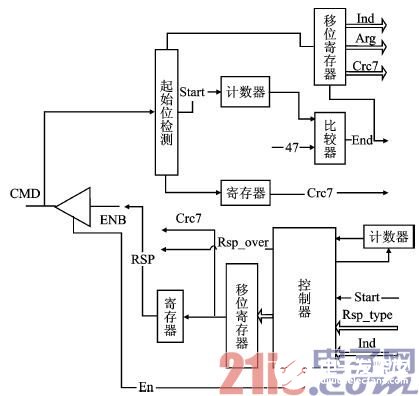

该模块的结构如图4所示。命令接收与响应发送都是在命令线CMD上传输的,所以该端口为一个三态门,由输出使能信号En控制是否输出。命令接收时,首先检测命令起始位,检测到起始位后计数器开始工作。当接收完一个完整命令,发出接收完成信号End,分别得到移位寄存器中对应的命令索引,命令参数,命令校验。命令接收过程中,同时将数据传给CRC7校验模块,用于生成校验数据。响应发送时,模块根据状态控制模块给出的响应类型产生对应的响应内容,当接收到发送使能信号Start后,给出发送使能信号En,并将响应的内容通过移位寄存器发送出去。响应内容发送完成后给出响应完成信号Rsp_over。

图3 模块结构

图4 命令接收与响应模块

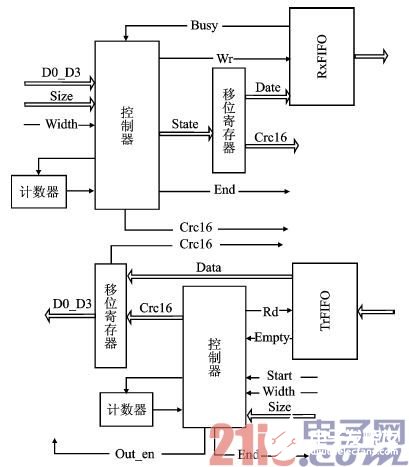

4.2 数据收发模块

该模块的结构如图5所示。数据线也是双向的。Width信号指明当前数据传输模式为标准总线模式或宽总线模式。Size信号指示每个数据块包含的字节数。该模块包含两个数据缓冲,接收缓冲RxFIFO和发送缓冲TrFIFO,数据缓冲位宽16比特,深度为256,这是因为数据块最大为512字节。数据接收状态时,首先检测数据起始位,检测到起始位后计数器开始工作。接收Size个字节的数据后,接收CRC16校验位,最后完成数据块接收,发出接收完成信号End。数据接收过程中,每接收16位数据给出写入信号Wr,将数据写入RxFIFO。如果RxFIFO满,给出Busy信号,主机进入数据发送等待。数据发送状态时,接收控制器收到Start信号后,开始发出Rd信号读取TrFIFO数据,并将数据传给移位寄存器,使能数据输出控制信号Out_en,移位寄存器根据数据传输模式将数据输出。

图5 数据收发模块

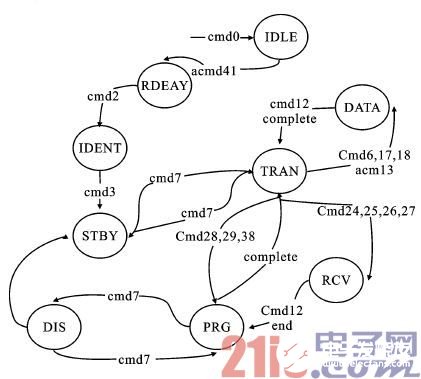

4.3 状态控制模块

根据接收模块传送的命令编号产生与之对应的命令响应类型,进一步解析接收模块传送的命令参数。工作过程共有9个状态,状态间的转移关系如图6所示。接收到CMD0命令后都会从其它状态进入到空闲状态。

图6 状态转移

4.4 校验模块

CRC7负责校验命令收发模块中的命令和响应;CRC16负责校验数据收发模块中的数据。

5、 验证与测试

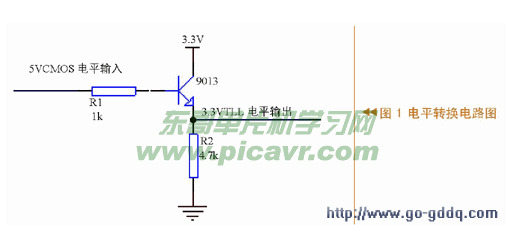

开发测试平台使用的是Altera的CycloneII系列FPGA开发板。开发板上有一个SD接口。测试平台的实物如图7所示。开发板可以通过一个PCB板SD接口与电脑SD接口连接,利用电脑对设计进行验证。

图7 测试平台

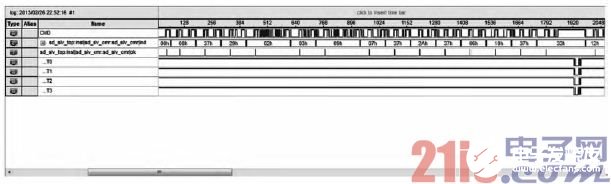

在硬件调试过程中,采用内嵌式逻辑分析仪(SignalTapII)来采集相应的数据波形。图8是采集到的识别SD卡命令与响应波形图。从图中可以看出,该设计可以正确响应主机命令,完成识别过程。

图9中虚线所圈是将设计下载到FPGA开发板,与电脑相连接后被识别为SD存储卡标记,可以看出该设计可以被电脑正确识别。

6、结束语

本文实现了一种SD存储卡接口SD模式IP核的设计与实现。该设计能够对主机命令进行自动解析和回复,与Flash控制器连接后可以直接对Flash进行读写操作。对该设计进行FPGA功能验证,能够被电脑识别为SD接口,从而说明的设计的正确性和实用性。利用SYNOPSYS公司的EDA工具对该模块进行综合,并进行时序和面积的优化,在SMIC0。18μm工艺下最大工作频率为100MHz,整个设计综合后为0.6万门。

图8 通信过程

图9 电脑识别

责任编辑:gt

-

FPGA

+关注

关注

1602文章

21320浏览量

593173 -

控制器

+关注

关注

112文章

15223浏览量

171172 -

读卡器

+关注

关注

1文章

396浏览量

38961

发布评论请先 登录

相关推荐

基于FPGA的I2C SLAVE模式总线的设计方案

WIFI无线技术各种热门设计方案~

基于ARM和FPGA的环形缓冲区接口设计方案

基于FPGA的数据采集控制器IP核的设计方案和实现方法研究

求一款在PCI总线上利用FPGA技术设计PCI总线接口的设计方案

SPI模式下SD卡驱动的设计与实现

AT89C52单片机与SD卡实现通讯的设计方案

如何使用FPGA实现SD卡控制器的设计

求一种FPGA实现图像去雾的实现设计方案

基于FPGA技术实现SD模式设备接口的设计方案

基于FPGA技术实现SD模式设备接口的设计方案

评论