10 月 24 日,RTC 2019 第五届实时互联网大会在北京悠唐皇冠假日酒店如期举行。在下午的编解码技术专场上,声网Agora技术VP高泽华正式宣布,开源声网自研抗丢包音频编解码器Agora SOLO。

目前,编解码器的源代码已经开源在 Github

为什么做一款抗丢包音频编解码器?

在近些年比较火的应用场景有这么几类:游戏,比如多人在线对战游戏、狼人杀等,多人组队,还需要实时语音;互动直播,比如主播与观众连麦、主播与其他主播进行跨直播间连麦,需要实时的互动;在线教育,其中有很多细分的场景,1 对 1、1 对多、双师等,在当前互动网络教育中最难解决的问题还是实时性,就是老师跟学生怎么能够更好的互动。 以上这些实时互动场景,在当前网络环境下,给技术提出了更高的要求,既要低延时,又要实现高质量的音视频互动。但是,如果承载信息的包没有按时到达,即出现丢包,就会产生声音断断续续、音质低等情况,直接影响实时互动的质量。然而,传统的抗丢包策略不是会浪费带宽,就是会影响音频质量,所以我们结合信源和信道编码的特点,利用充分包交换网络的特性,基于此,研发出了声网新的编解码器——Agora SOLO。

Agora SOLO 是什么?

Agora SOLO(以下简称“SOLO”)是由声网Agora自主研发的一款面向不稳定网络的音频编解码器,它以 Silk 为基础,融合了带宽扩展(BWE)和多描述编码(MDC)等技术,使其能在较低复杂度下拥有弱网对抗能力。SOLO 编解码器兼容WebRTC,可集成到基于 WebRTC 自主研发的产品中。

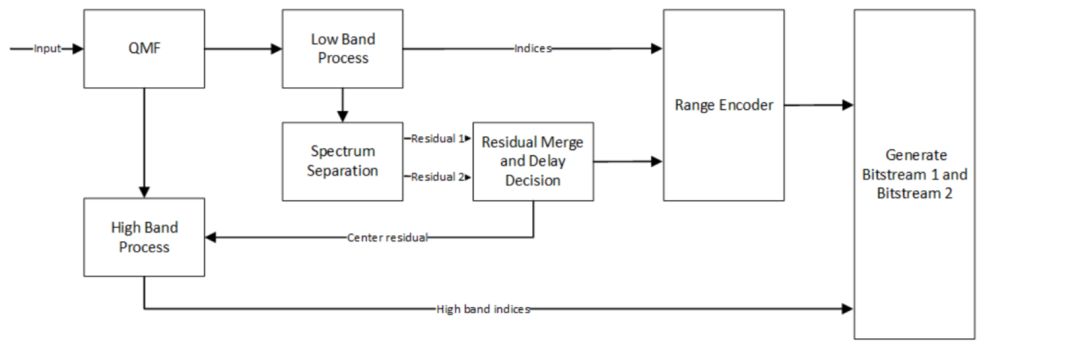

图 1. SOLO编码器架构

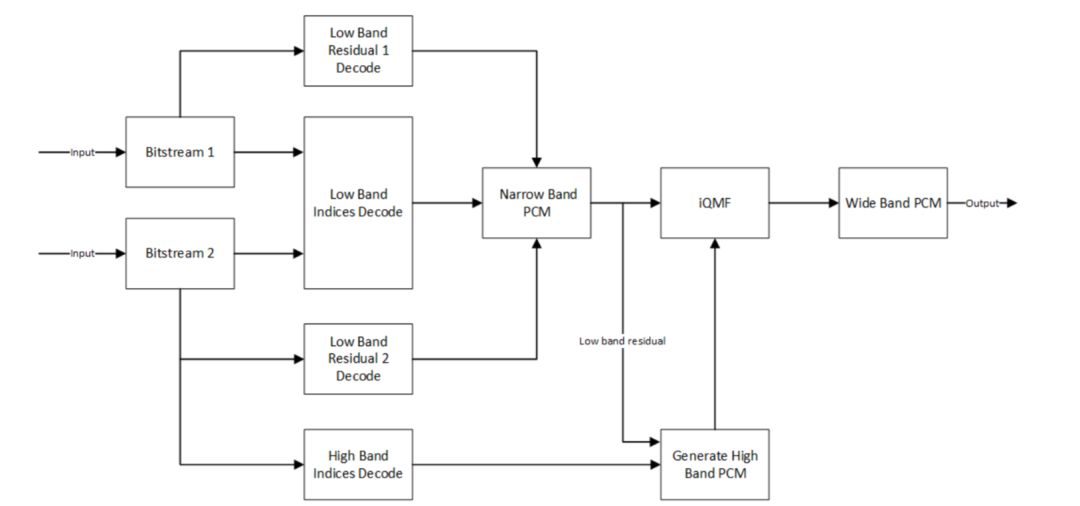

图2. SOLO解码器架构

SOLO的抗丢包策略与传统方法不同。从通信原理来说,信源编码是尽可能去追求高压缩比,去冗余。而信道编码是追求强纠错,靠加冗余来实现纠错。Agora SOLO就是把加冗余和减冗余结合起来,不重要的地方减冗余,重要的地方加冗余。 在传输过程中,它会将一个包拆分为两个进行传输,如果对端收到其中一个,则解码恢复出一个有限失真的信号;如果对端收到两个包,则可解码恢复出一个高质量的信号。即 SOLO不需要等待对当前网络丢包状态的统计,只需要直接把抗丢包做到编解码内部。好处有三点:1.可实现更低延时;2.可实现更高质量,当收到一个包时质量达到的普通编解码器水平,收到两个包达到高质量编解码水平;3. 可面向多人环境。

SOLO 关键技术

01 带宽扩展

SOLO 使用带宽扩展的主要原因是希望减少计算复杂度,在 Silk WB 模式中,16khz 的信号都会进入后续处理模块,而对于语音来说,8khz 以上的信息是非常少的,这部分信息进入到后续处理模块,会带来一定的计算资源浪费。MDC 因为要引入额外分析模块处理多条码流,又会引入额外的复杂度,这是 MDC 在近些年来落地不顺畅的重要原因之一。为了减少复杂度,我们在编码宽带信号前,将其分为 0-8k 的窄带信息和 8-16k 的高频信息。只有窄带信息会进入到后续正常分析、编码流程中,这样后续的计算量就减少了一半,同时得益于带宽扩展算法,整体质量不会有明显下降。高频信息部分,SOLO 使用独立的分析与编码模块,默认将高频信息压缩成 1.6kbps 的码流。这部分高频信息可以在解码器内结合低频信号恢复出高频信号。

02 结合 delay-decision 的 MDC

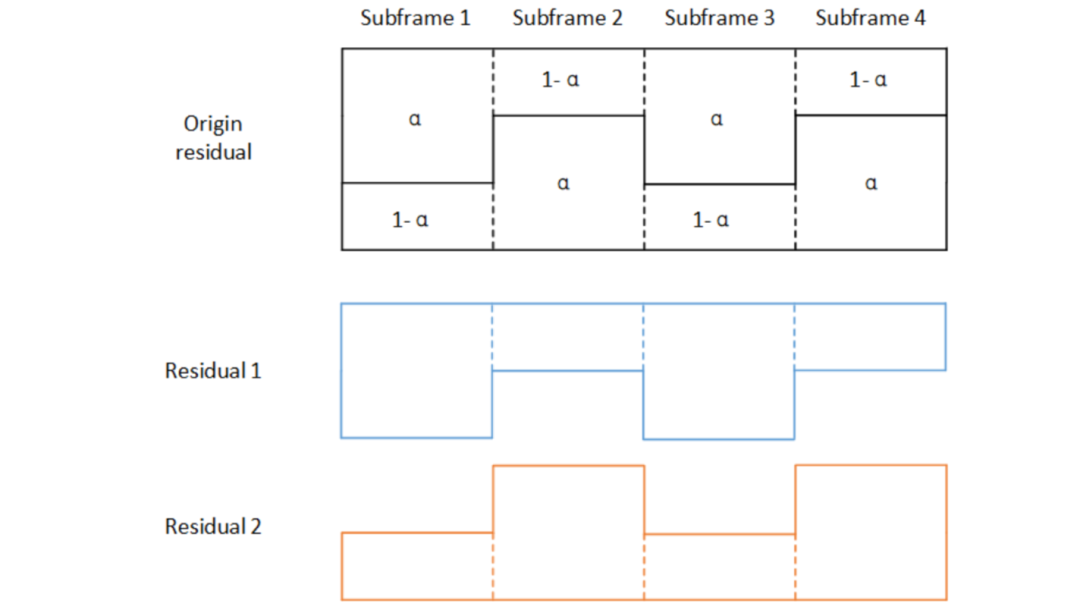

在 Silk 中,delay-decision 模块是一个滞后计算编码误差的模块,它可以从多个候选码流中选择误差最小的码流作为编码输出,一定程度上来说,它使得标量量化拥有了矢量量化的性能。SOLO 利用 delay-decision 模块,实现了多描述码流的分析与构建。SOLO 的MDC主要作用于滤波器输出的残差信号, SOLO 会根据当前信号状态,对残差信号做多增益控制:计算出 MD 增益 a(0

图 3. 多描述残差信号产生

随后,这两段残差信号会进入到新的 delay-decision 模块中,每个残差信号使用不同的抖动和量化方法,一共可以产生 8 种不同的备选状态,两两组合起来共有 64 种备选合成状态,新的 delay-decision 模块会对每个残差信号的独立误差和两个残差信号的合成误差进行加权求和,决定出最佳的两个残差信号进入到编码模块。

03 输出码流组包

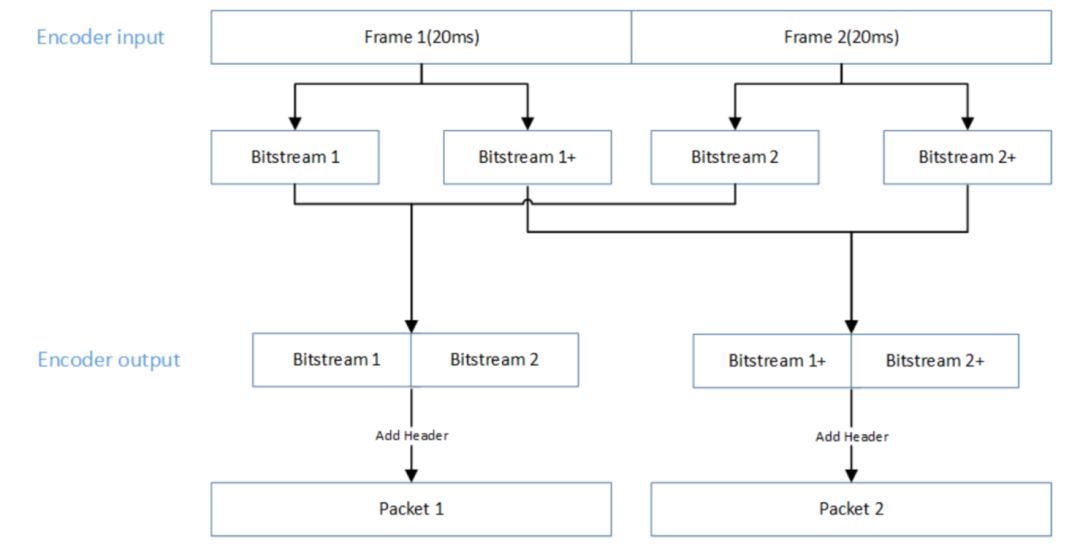

图 4. 编码器码流整合及组包

SOLO 默认配置为每次输入 40ms(2 帧),输出两段互补的多描述码流,解码器接收到任一段码流,即可解码出 40ms 的信号。为了方便接收端区分码流的顺序,码流第一个字节的右数第 4 个 bit 是码流顺序标志位,第一段码流标志位的值是 0,第二段码流标志位的值是 1。接收端在进行码流处理时,可依据此标志位进行码流顺序判断。

-

解码器

+关注

关注

9文章

1073浏览量

40156 -

音频

+关注

关注

28文章

2599浏览量

79968

原文标题:声网Agora开源抗丢包音频编解码器Agora SOLO

文章出处:【微信号:shengwang-agora,微信公众号:声网Agora】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

TPS65920和TPS65930集成电源管理/音频编解码器数据表

使用具备SigmaDSP内核的编解码器是否必须载入SigmaDSP程序才能使用?

如何在嵌入式系统中使用音频编解码器更轻松地优化音频性能?

使用STM32L1xx微控制器与外部I2S音频编解码器播放音频文件

为什么做一款抗丢包音频编解码器?

为什么做一款抗丢包音频编解码器?

评论