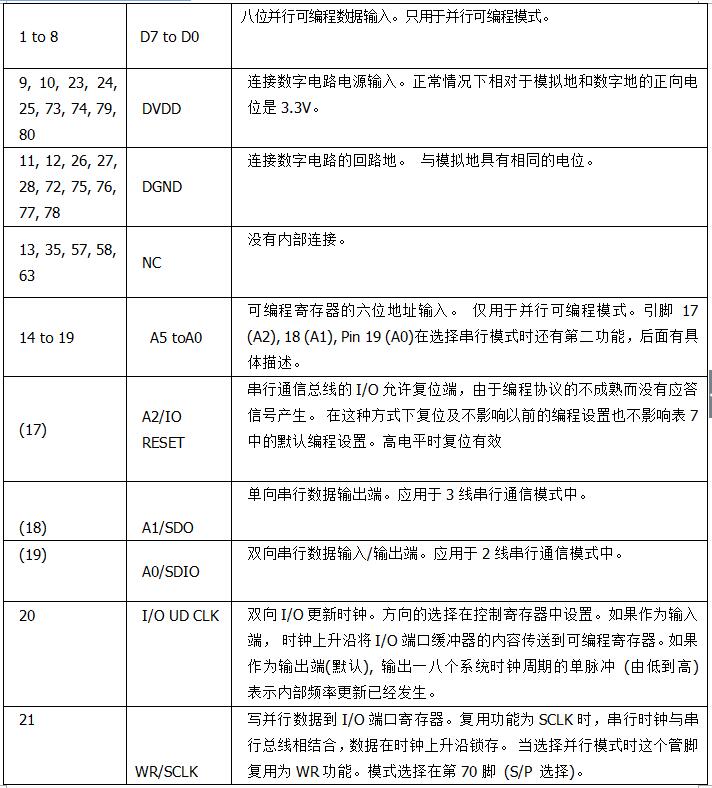

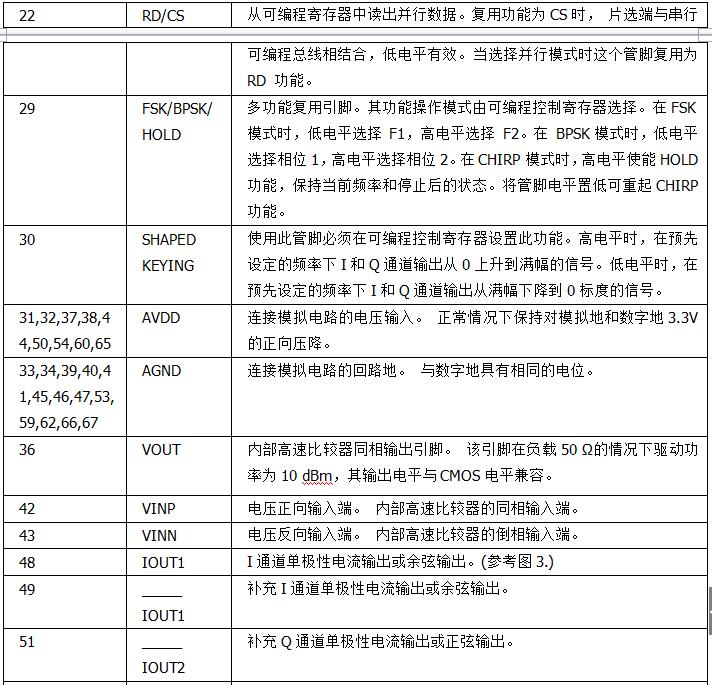

AD9854引脚及功能

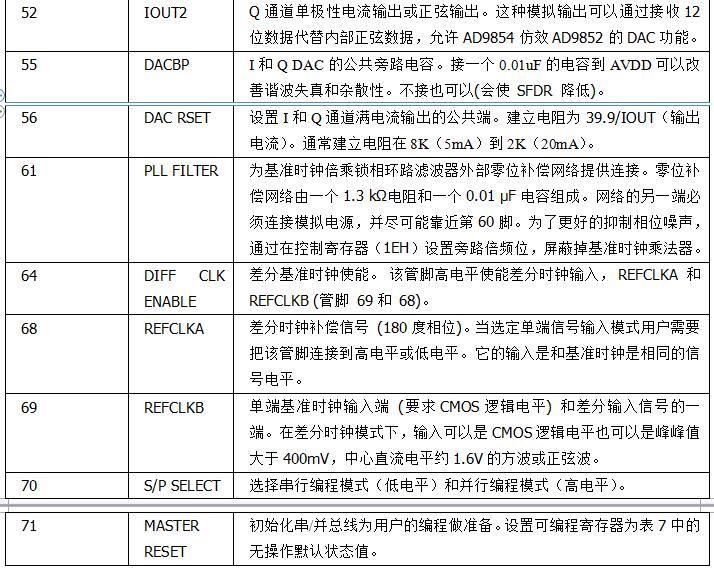

引脚描述:

AD9854的编程

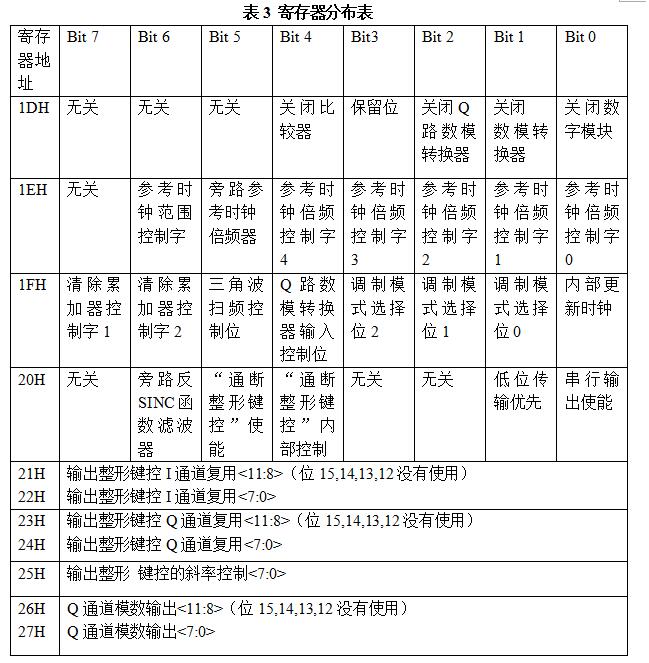

AD9854的各寄存器列出在下表,包含各各功能的片内编程信息。很多应用要求很小的编程规模去装配AD9854,就可以使用了,实现功能了。但有一些要求用户使用所有的12个寄存器入口地址。AD9854支持8位并行I/O操作或一位SPI-compatible串行I/O操作。所有入口寄存器能读和写,在每个I/O操作模式下。S/P选择,引脚70,用于I/O模式选择。若系统使用并行I/O模式,必须连接S/P选择引脚到VDD。若系统操作在串行模式,必须连接S/P选择引脚到GND。

不使用模式,I/O口数据写入缓冲寄存器,不影响该部分操作直到缓冲寄存器传输数据到寄存器数据库。信息传输同时产生在系统时钟,两种产生方式:

(1)内部控制在某一由用户编程产生的速率

(2)由用户外部控制,I/O操作能在没有REFCLK情况下进行,但数据从缓冲期传输到存储器,没有REFCLK是不行的。能从该文献更新时钟章节中了解到更多的详细信息。复位管理——逻辑高电平有效,必须保证电平不小于10个系统时钟周期的持续时间。复位主要引起通信总线的初始化并载入默认值到内部或外部的时钟更新段。

并行输入输出操作

在S/P选择引脚被拉为高电平时,并行输入输出模式被激活。这种输入输出口与标准工业DSPs 和microcontrollers相兼容。6个地址位,8个双向数据位,和分离的写/读控制输入来补足这输入输出口引脚。

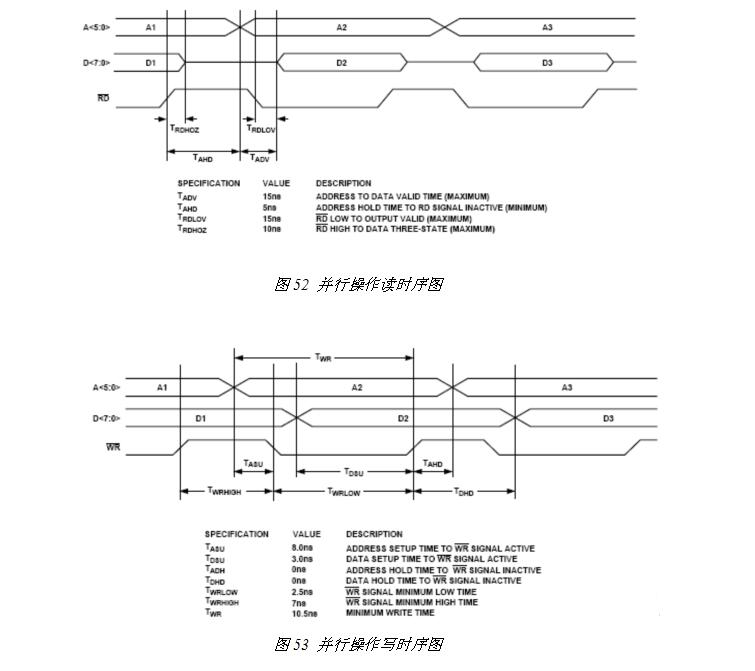

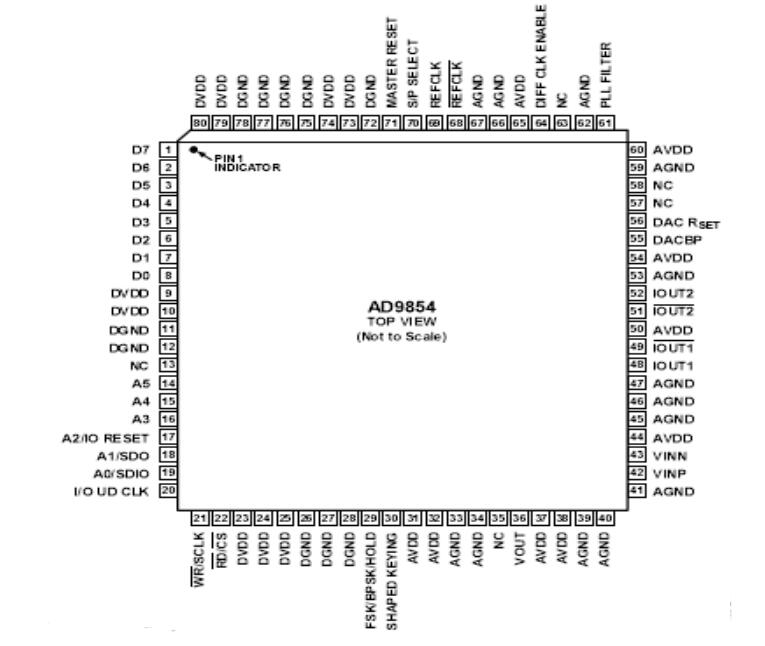

并行输入输出操作模式允许到1/10.5纳秒对每个寄存器进行单字节操作。对寄存的回读操作主要用来优化对AD9854的设计 (读寄存器不能保证100 MHz的操作速度,这一点他们为只是软件调试准备的)。

并行输入输出操作时序图如图52 和图53 所示。