本文为大家介绍电子计时器的VHDL设计方法。

设计要求

设计一个电子计时器,给定时钟信号为512HZ,要求系统达到以下功能:

(1)用6个数码管分别显示时、分、秒,计时范围为00:00:00~23:59:59。

(2)计时精度是1s。

(3)具有启/ 停开关, 复位开关。

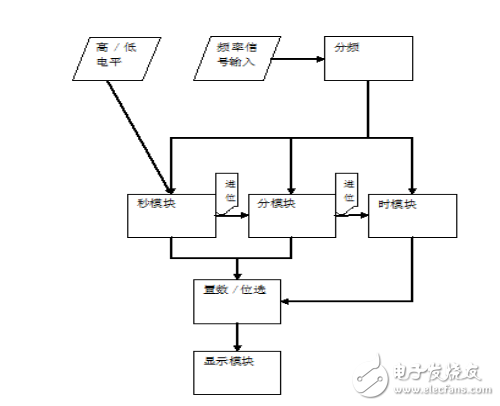

总体方框图

内部各功能模块

本系统由六十进制计数器模块、二十四进制计数器模块、分频模块执行计时功能, 输入信号是512Hz,通过分频后为1Hz,时钟信号是1Hz作为计时器的秒输入,秒为60进制计数器,分也为60进制计数器,小时采用二十四进制计数器, 各级进位作为高位的使能控制。

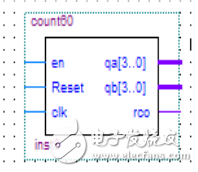

六十进制计数器模块

设计一个八位的六十进制计数器模块,输入信号为en、reset、clk,分别为使能、复位和时钟信号,输出信号为qa[3„0]、qb[3„0]、rco,分别为低4位输出、高4位输出和进位位。

六十进制计数器

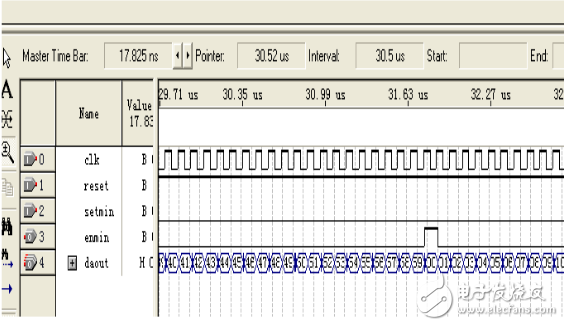

示波形分析

秒计数器的仿真波形图

利用60进制计数器完成00到59的循环计数功能,当秒计数至59时,再来一个时钟脉冲则产生进位输出,即enmin=1;reset作为复位信号低电平有效,即高电平时正常循环计数,低电平清零。因为这种60进制的VHDL语言是很好写的,它并不复杂,再说我们必须要学会这些基本的硬件语言的描写。

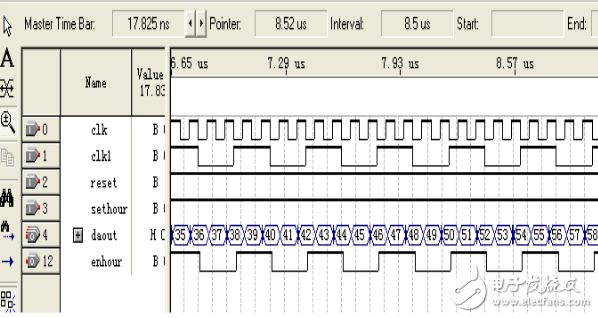

分钟计数器的仿真波形图

VHDL源程序

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_unsigned.ALL;

ENTITY count60 IS

PORT( en,Reset,clk: in STD_LOGIC;

qa: out STD_LOGIC_VECTOR(3 DOWNTO 0);

qb: out STD_LOGIC_VECTOR(3 DOWNTO 0);

rco: OUT STD_LOGIC); END count60;

ARCHITECTURE a OF count60 IS

BEGIN

process(clk)

variable tma: STD_LOGIC_VECTOR(3 DOWNTO 0);

variable tmb: STD_LOGIC_VECTOR(3 DOWNTO 0); begin

If Reset =‘0’then tma:=“0000”;

tmb:=“0000”;

elsif clk‘event and clk=’1‘ then

if en=’1‘ then

rco<=tmb(2)and tmb(0)and tma(3)and tma(0);

if tma=“1001” then

tma:=“0000”;

if tmb=“0101” then

tmb:=“0000”;

else tmb:=tmb+1;

end if;

else tma:=tma+1;

end if;

end if;

end if;

qa<=tma;qb<=tmb; end process; END a;

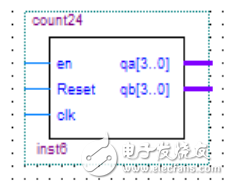

二十四进制计数器模块

设计一个八位的二十四进制计数器模块,输入信号为en、reset、clk,分别为使能、复位和时钟信号,输出信号为qa[3„0]、qb[3„0],分别为低4位输出、高4位输出。

二十四进制计数器示意图

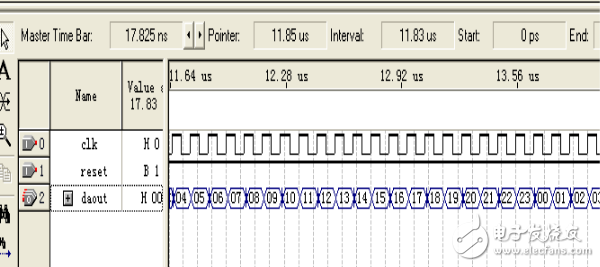

波形分析

小时计数器的仿真波形图

VHDL源程序

小时计数模块利用24进制计数器,通过分钟的进位信号的输入可实现从00到23的循环计数。

该模块部分VHDL 源程序如下:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_unsigned.ALL;

ENTITY count24 IS

PORT( en,Reset,clk: in STD_LOGIC;

qa: out STD_LOGIC_VECTOR(3 DOWNTO 0);

qb: out STD_LOGIC_VECTOR(3 DOWNTO 0));

END count24;

ARCHITECTURE a1 OF count24 IS

BEGIN

process(clk)

variable tma: STD_LOGIC_VECTOR(3 DOWNTO 0);

variable tmb: STD_LOGIC_VECTOR(3 DOWNTO 0);

begin

If Reset = ‘0’then tma:=“0000”;

tmb:=“0000”; else

if clk‘event and clk=’1‘ then

if en=’1‘ then

if tma=“1001” then

tma:=“0000”;

tmb:=tmb+1;

elsif tmb=“0010” and tma=“0011” then

tma:=“0000”;

tmb:=“0000”;

else tma:=tma+1;

end if;

end if;

end if;

end if;

qa<=tma;

qb<=tmb;

end process;

END a1;

用户评论(0)