基于多相滤波的数字接收机的FPGA实现

2012年05月23日 10:43 来源:互联网 作者:秩名 我要评论(0)

0 引言

信道化接收机是在并行多通道接收机基础上提出的全概率频分信道化接收机,它克服了多部接收机并行工作、多通道 下变频等方案具有的设备复杂,各通道性能不一致和可靠性差的缺点。数字信道化接收机具备大的瞬时带宽、较高的灵 敏度、大的动态范围,能够检测和处理同时到达的信号、准确的参数测量能力和一定的信号识别能力。直接信道化接收 机的运算量大且输出速率与采样速率相同,实现困难,后续处理的压力很大,高速ADO与慢速信号处理器(FPGA,DSP) 是一个“瓶颈”;基于多相滤波的信道化接收机抽取在滤波之前,运算量小,且输出速率低,便于FPGA实现,这使得在 一片FPGA中实现数字信道化成为可能。本文利用信道频率重叠的方法连续覆盖整个瞬时带宽,然后利用Rife算法测频, 根据信道重叠的特点,消除虚假信号。系统带宽为875 MHz(62.5~937.5 MHz),可以处理两个同时到达的信号,并实 时给出PDW。

1 宽带数字接收机的结构

1.1 数字信道化原理

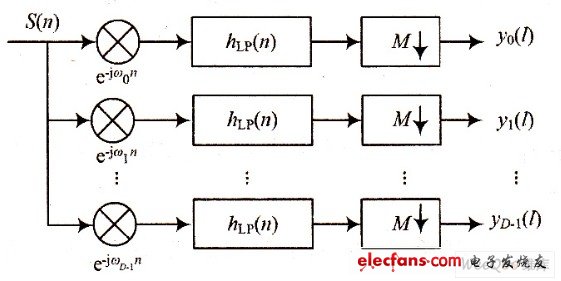

信道划分的基本思想是把信号按频率均匀地分成D个子频段(即信道),每个信道的中心频率为妈,然后分别移到零中频,再通过低通滤波器滤出。由于子信道的带宽远小于系统瞬时带宽,因此可以采用抽取的方法来降低信号的输出速率,降低后续处理的压力。图1中,![]() 为低通滤波器;M↓表示对经过低通滤波器的信号M倍抽取。对于实信号而言,在侦察接收机中,各信道输出经过M=D倍抽取后,会产生频谱混叠,如图2所示。各个信道的中心频率为

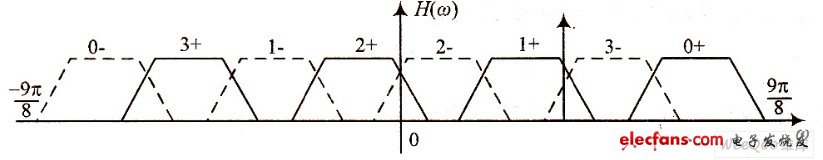

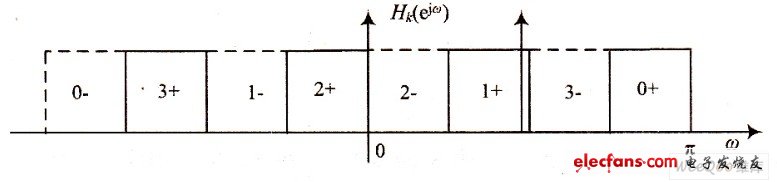

为低通滤波器;M↓表示对经过低通滤波器的信号M倍抽取。对于实信号而言,在侦察接收机中,各信道输出经过M=D倍抽取后,会产生频谱混叠,如图2所示。各个信道的中心频率为![]() ,覆盖整个频域范围。但 是这种接收机存在信道的虚假输出。由图2中可以看出,当输人信号位于某一信道时,靠近这一信道的相邻信道会产生虚 假输出。图2中实线表示实信道,虚线表示镜像信道。在信道化接收机的输出端接瞬时测频模块,可以消除虚假信号,同时还能提高频率精度。推导计算出混叠部分频率的点数,在固定的某一信道,将重叠部分的点只取一次,删除多余的点数,即消除虚假信号,得到如图3所示的等效滤波器组。

,覆盖整个频域范围。但 是这种接收机存在信道的虚假输出。由图2中可以看出,当输人信号位于某一信道时,靠近这一信道的相邻信道会产生虚 假输出。图2中实线表示实信道,虚线表示镜像信道。在信道化接收机的输出端接瞬时测频模块,可以消除虚假信号,同时还能提高频率精度。推导计算出混叠部分频率的点数,在固定的某一信道,将重叠部分的点只取一次,删除多余的点数,即消除虚假信号,得到如图3所示的等效滤波器组。

图1 数字信道化原理框图

图2 覆盖整个频谱的信道分配图

图3 处理后的等效滤波器组

1.2 实信号无言区信道化接收机数学模型

由图1可得第乃路信号的输出为:

令j=iD+p代入上式,得:

定义

![]()

则有

将式(1)代入式(4)得:

式(5)中

则式(5)为:

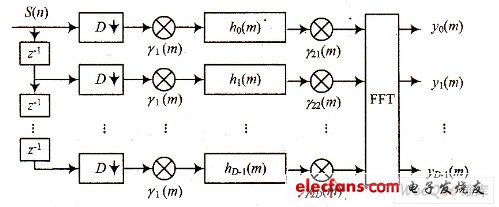

这样得到实信号数字信道化的多相滤波实现模型,如图4所示。

图4 实信号频率信道化的多相滤波实现

上周热点文章排行榜

上周资料下载排行榜

论坛热帖

热门博文

创新实用技术专题

热评

- LM3S9B96开发板手册及原理图

- STM32F103ZET6红牛电路图

- 高通发布全新设计DragonBoard板

- NI推出Single-Board RIO嵌入式介面

- protel99se正式汉化版免费下载

- hi3515海思原版原理图

- matlab 7.0软件下载(免费破解版)

- TX-1C型单片机开发板原理图

- 三菱A500变频器原理图

- 三相IGBT全桥隔离驱动电源设计

博文

- 问什么邮箱激活不了

- 八成大学生认同先就业后择业

- 我的心路

- 你是否曾这样伤害过一个人?

- 为什么邮箱激活不了

- 2012.5.12 第一个DS18B20程序

- 到底有多少人在校园里浪费青春

- 蓝牙技术越来越鸡肋

- 【博客分享季】 我的单片机入门

- 到底有多少人在校园里浪费青春

用户评论

查看全部 条评论

查看全部 条评论>>