什么是逐次逼近模数转换器(ADC)

在电子系统中,数-模(DA)和模-数(AD)转换常为重要的部分。真实世界中的信号都是模拟量,随着科技的飞速发展,现在数字信号的处理技术越来越成熟,我们现在可以使用强大、灵活而可靠的数字信号处理(DSP)器来对模拟信号的数字形式进行处理,这样就要求我们把模拟信号变换为数字信号。因而模数转换器(ADC)就成为数模混合系统的重要组成部分。

逐次逼近寄存器型(SAR)ADC是采样速率低于5MSPS的中等至高分辨率应用的常见结构。SAR ADC的分辨率一般为8位至16位,具有低功耗、小尺寸等特点。这些特点使其具有很宽的应用范围,例如便携/电池供电仪表、笔输入量化器、工业控制和数据/信号采集器等。

顾名思义,SAR ADC实质上是实现一种二进制搜索算法。所以,当内部电路运行在数兆赫兹时,山于逐次逼近算法的缘故,ADC采样速率仅是该数值的几分之一。SAR ADC的一个特点是,功率损耗随采样速率而改变,这一点与闪速ADC或流水线ADC不同,后者在不同的采样速率下具有固定的功耗。这对与低功耗应用或者不需要连续采集数据的应用非常有利。

基本原理:

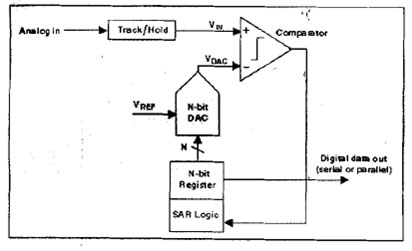

SAR ADC 的基本结构如上图所示。它由采样保持电路(track/hold)、比较器(comparator), DAC(数字模拟转换器)、寄存器(N-bit Register)和移位寄存器(SARLogic)组成。其工作原理基于二进制搜索算法,过程如下:

模拟输入电压(Vin)由采样/保持电路保持。为实现二进制搜索算法,N位寄存器首先设置在数字中间刻度(即:100...00, MSB为‘1' )这样,数字模拟转换器(DAC)输出(Vdac)被设置为Vref/2, Vref是提供给ADC的基准电压。然后,比较判断Vin是小于还是大于Vdac。如果Vin>Vdac,则比较器输出逻辑高电平或‘1’,N位寄存器的MSB保持‘1'。反之,比较器输入逻辑低电平,N位寄存器MSB清为`0'。随后,SAR控制逻辑移至下一位,并将该位设置为高电平,进行下一次比较。这个过程一直持续到最低有效位(LSB)。上述操作过程结束后,也就完成了转换,N位转换结果储存在寄存器内。

下图是一个4位ADC转换结果。Y轴(和图中的粗线)表示DAC的输出电压。在本例中,第一次比较表明Vin

现状和发展:

SAR ADC的主要优点是低功耗、高分辨率、高精度、输出数据不存在延时以及小尺寸。由于这些优势,SAR ADC常常与其它更大的功能集成在一起。SAR结构的主要局限是采样速率较低,并且其中的各个单元,如DAC和比较器,需要达到与整体系统相当的精度。

非常好我支持^.^

(54) 98.2%

不好我反对

(1) 1.8%

相关阅读:

- [工业控制] MOVIPRO:电机初始化Starting up the motor encoder 2023-10-24

- [电子说] 一种用于高精度测量应用的低功耗模数转换器(ADC)解决方案 2023-10-24

- [电子说] 学习STM32F103的ADC功能 2023-10-24

- [电子说] 振弦传感器和信号转换器在桥梁安全监测中的重要性 2023-10-24

- [电子说] 川土微电子发布CA-IS3115AW-Q1 DC-DC转换器芯片 2023-10-24

- [电子说] 失调误差是如何影响单极性ADC传递函数的? 2023-10-24

- [电子说] 电流模式升压DC-DC转换器FP6296介绍 2023-10-24

- [电子说] STM32速成笔记(7)—ADC 2023-10-24

( 发表人:admin )