数字控制振荡器,数字控制振荡器电路原理分析

在实际的通信系统中,携带数字信息的信号通常是由某种类型的载波调制方式发送的,传送信号的带宽限制在以载波为中心的一个频段上,如双边带调制,或在邻近载波的频段上,如单边带调制。无论何种调制方式,在发送端均需要一个高频载波将信息调制上去,以减小信号衰落,相干解调时在接收端也需要一个与发送端同频同相的高频载波将信息从高频上解调下来。为了产生这个高频载波,在数字电路中是采用数控振荡器(NCO),也称为直接数字频率合成器〔DDS),它的输出频率和相位可以受人为控制,从而满足各种需要。

基本原理:

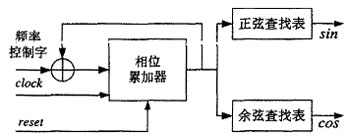

下图为NCO的工作原理框图:

数控振荡器一般由基准时钟(fclk)、相位字寄存器、相位累加器以及幅度/相位转换电路等部分组成。在基准时钟的作用下,每一个时钟周期存贮在相位字寄存器里的值都由相位累加器进行累加,相位果加器的输出作为查找表的输人,从而得到相对应的幅度值。根据奈奎斯特采样定律,输出信号的频率应小于基准时钟的1/2。

相位累加器输出(△Ф)的数值和系统的频率(fclk)决定了输出频率(fout),它门的关系如下:

![]()

N是相位寄存器的位数,N值的大小决定了频率分辨率(fres ),有

![]()

在这里假设,fclk=128MHz, N=32,可以计算出NCO的频率分辨率fres=0.0298Hz

相位累加器是决定NCO电路性能的一个关键部分。我们可以采用了Altera的加法器宏功能模块形成一个32bit的累加器,它以流水线处理方式进行工作。

相位/幅 度转换电路是NCO电路中的另一个关键部分,在设计中面临的主要问题就是资源的开销。

一般电路采用ROM结构,相位累加器的输出是一种数字式锯齿波,通过取它的若干位作为ROM的地址输人,而后通过查表和运算,ROM就能输出所需波形的量化数据。

在APEX器件中,ROM由EAB实现,ROM表的尺寸随着地址位数或数据位数的增加成指数递增关系,因此在满足信号性能的前提条件下,如何减少资源的开销就是一个重要的问题。

在实际设计时,要充分利用信号周期内的对称性和算术关系来减少EAB的开销。

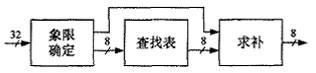

上图为产生正弦信号的相位/幅度转换电路,相位累加器累加值的最高位(MSB )和次最高位(MSB-1)的组合作为象限确定模块的输人,由此来确定输出信号所在的相平面和极性符号,如表所示。

正弦查找表存贮了1/4周期的正弦幅度数据,通过象限确定模块就可以完成完整的正弦波的形成。这里采用了一个256 x 8的ROM宏模块。地址线和数据线输出均为8bit, 8bit地址分别对应相位累加器的30-23bit的输出数据。正弦查找表的输出是无符号的8bit数据,并不能代表正弦波形。求补模块根据象限确定模块的输出符号位的极性来对查找表输出数据进行求补,并把此符号位和正弦查找表输出的高7bit组合作为最终正弦波输出信号。

非常好我支持^.^

(4) 20%

不好我反对

(16) 80%

相关阅读:

- [电子说] 全志R128应用开发案例—获取真随机数 2023-10-24

- [控制/MCU] 单片机学习笔记 2023-10-24

- [电子说] 运算放大器反相输入端电压高于同相输入端会怎样?输出是什么样子? 2023-10-24

- [电子说] 经典的简单型晶体测试仪电路图讲解 2023-10-24

- [电子说] 基于555芯片的振荡器电路分析 2023-10-24

- [电子说] MLCC的结构、特点、应用及发展趋势 2023-10-23

- [电子说] 提高支付体验:YXC扬兴科技 有源晶振 YSO110TR高精度刷卡器 2023-10-23

- [模拟技术] 谈谈双三极管驱动LED的多谐振荡器 2023-10-23

( 发表人:admin )