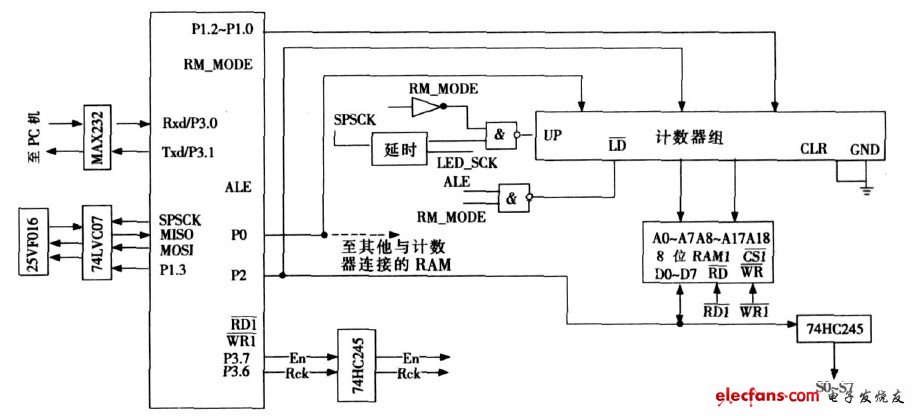

从上文可以得到这样的启示:在LED控制电路的设计中,可借助于SPI 模式读取数据,即增加一块SPI 模式的FLASH 存储器,一方面可以保存重要文档,另一方面可以利用SPSCK 产生的信号,通过计数器电路实现对存储器高速读数据,并且复用此信号产生屏幕显示的控制信号。在给定了输出数据的首地址并启动SPI 后,此方式使数据的读出到屏幕显示这一过程自动进行,同一信号源的全硬件方式大大减少了以往分别产生各控制信号方式时的衔接延时。图3 为SPI 在LED大屏幕控制电路中的运用示例。

图3 SPI 模式下的L ED 大屏幕控制电路图

级联计数器的个数根据RAM 的容量大小,即地址线的数目来确定。微处理器通过驱动器连接SPI 串行存储器, 驱动器可以选择7407 或7417 的型号。RM_MODE 用来区别不同的读写操作方式。当RM_MODE = 1 时,是普通读写外部存储器的方式,当RM_MODE = 0 时,就可以让主机作为主器件,串行FLASH 存储器作为从器件,两者以SPI 方式进行通信,利用此时产生的SPSCK信号对存储器进行高速读数据操作。同时SPSCK信号经过变换与延时处理,可以供给LED做SCK 移位信号用。在计数脉冲的输入端,可以使用跳线做加、减方式的选择处理。当脉冲接于计数器UP 端时, 为加计数方式, 接于DOWN 时,为减计数方式。图3 也可扩展并接多组计数器,多组RAM.

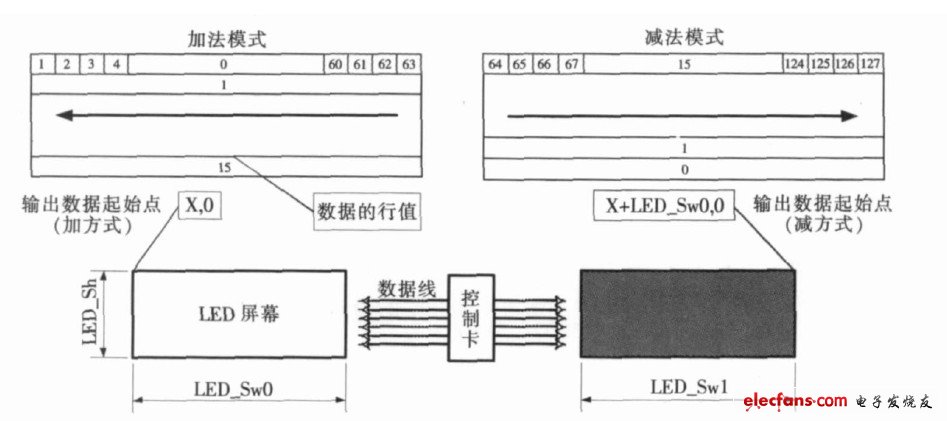

减计数器方式的运用大大增强了数据输出的灵活性。在LED大屏幕显示中,加、减计数器配合使用,可以使相同一块控制卡输出数据的显示长度提高一倍。当使用减计数器方式时,为了与使用加方式时LED大屏幕上显示的图文一致,必须对与减计数器连接的RAM 的数据进行上、下半屏交换处理,并且在输出时要在程序中改变数据的起始点,给出的行控制信号(RCK) 也应做倒序处理(见图4)。

图4 加、减法模式下的数据组织与显示

4 本方式使用时的注意事项

本方式使用时要注意计数器及RAM 芯片的读写速度必须与SPSCK 相匹配。SPI 方式的速率比较高,电路各器件读取速度越高,数据出错的几率就会越小。

此外还有其他一些原因也会引起读数据时的错误。如软件编写不当导致数据地址超出RAM空间,电路设计未重视计数器高速工作时发热对周边器件与布线带来的影响等。

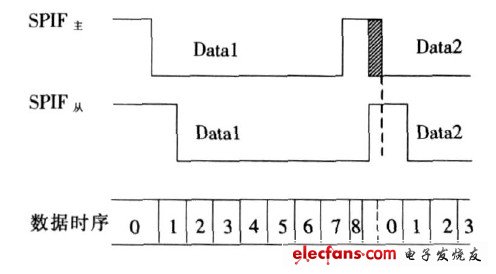

使用SPSCK 信号读取外部储存器时,同样会产生SPI 主、从模式下的溢出错误,即连续传输多个数据时, 后一个数据覆盖了前一个数据而产生的错误。这种错误产生的原因是从器件的传输标志SPIF从相对于主器件的传输标志SPIF主有一定的滞后,在主器件连续发送数据时,会导致从器件的传输标志和主器件下一个数据的传输标志相重叠,而利用SPSCK 触发计数器使地址递加读取数据,第一个收到的数据也会被覆盖。

这种传输错误可以用软、硬件的方法进行改进。在本文的设计中,后期在软件编写上采用了如下解决方法:先启动SPI 模式,再进入计数器读并行RAM ,浪费一个时序。或是在RAM 中存入数据时,全部存到它后一位的地址单元上,再用SPI 方式产生的脉冲去读RAM ,就可得到正确的数据。

理论上本文方式可使显示数据的输出速度高至fOSC的1/ 4 ,但实际运用时却受到了RAM、锁存器等输出电路器件的参数限制。SPSCK 的速率设定要根据所选择RAM 的参数确定,即要满足RAM 最小的地址有效时间与数据有效时间的要求。

图5 主、从SPIF 时序下的数据溢出错误

5 结 语

通过此方法对输出电路进行改造,可极大地使原有控制系统满足数据高速输出的要求。本文给出的例子虽是基于LED大屏幕应用的,但在LCD 或是其他对数据有高速输出要求的系统中,同样具有借鉴运用意义。