74hc165简介

74HC165是8位并行读取或串行输入移位寄存器,可在末级得到互补的串行输出(Q7和!Q7),当异步并行读取引脚(!PL)输入为低时,从D0到D7口输入的并行数据将被读取进寄存器内。而当异步并行读取引脚为高时,数据将在每个时钟脉冲的上升沿从引脚串行进入寄存器并将现有数据右移一位(以此类推)。利用这种特性,只要把Q7输出绑定到下一级的输入,即可实现移位寄存器位数的扩展。74HC165的时钟输入是一个“门控与”结构,CP(时钟脉冲)和CE(时钟允许)共同产生有效时钟输入。只有在CE(时钟允许)为低时,CP(时钟脉冲)才有效。

74hc165特性

8位同步并行输入

异步串行输出

兼容JEDEC标准no.7A

ESD保护

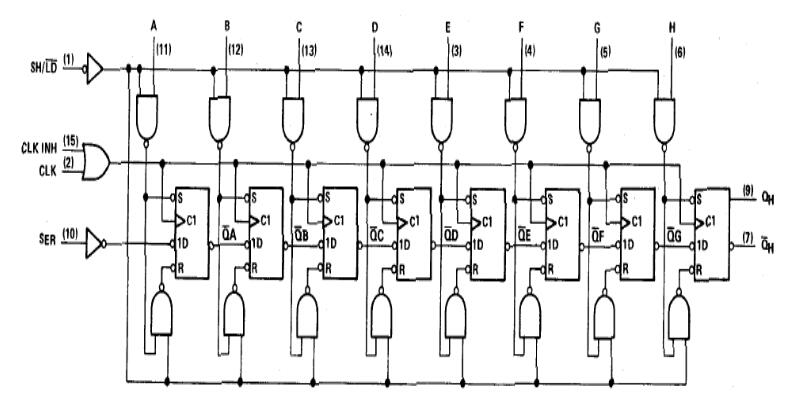

74HC165逻辑图

74hc165基本参数

电压:2.0~6.0V

驱动电流:+/-5.2mA

传输延迟:16ns@5V

最高频率:56MHz@5V

逻辑电平:CMOS

工作温度:-40~+85℃

封装:SO16,SSOP16,DIP16,TSSOP16

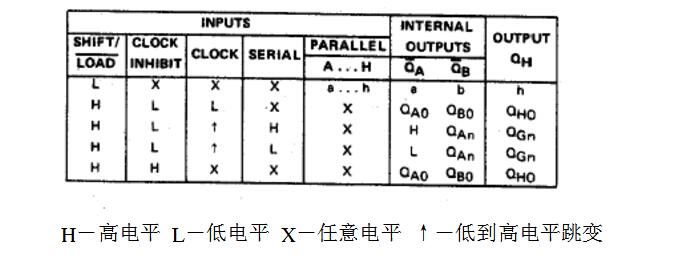

74HC165真值表

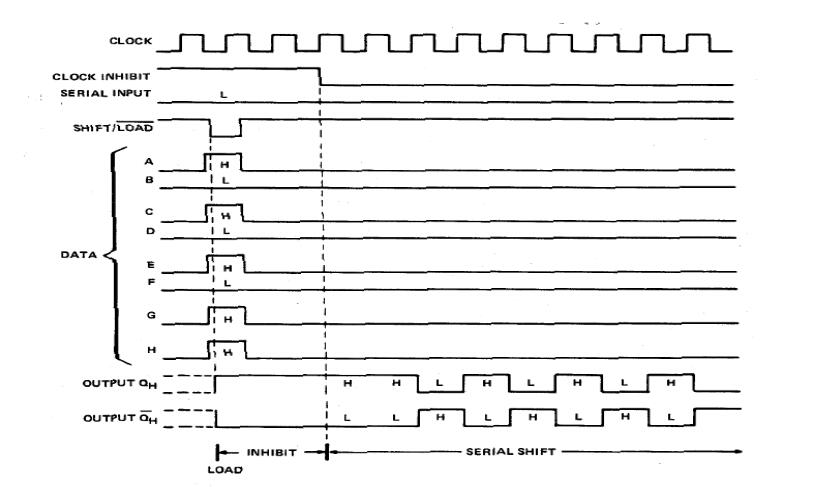

74HC165时序图