电容电阻串并联有什么不同的作用?

电容并联电感,产生并联谐振,也称为电流谐振,谐振时,LC的谐振阻抗达到最大值;电容、电感中的电流达到最大值。并联的R越大,谐振回路的Q值越高。即使不并联电阻,电感、电容本身也有损耗电阻,客观上也存在电阻并联。 电容串联电感,能产生串联谐振,也称为电压谐振。谐振时,LC的谐振阻抗达到最小值;电容、电感上的电压达到最大值。串联的电阻越小,谐振回路的Q值越高。即使不串联电阻,电感、电容本身也存在一定的损耗电阻。由于发电机是交替正负,而切割磁感线的量不是正比而是正弦函数变化,所以就有了市电压为波,滤波的好处在于让交流变成稳定的电流,经过二极管整流与电容的滤波就能得到一般好的直流电,有助于如需要稳定电压的IC工作!

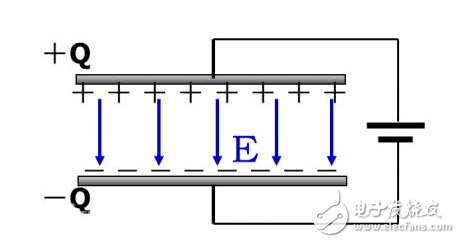

1)电容的作用是:阻止直流信号通过,而允许交流信号通过。或者是减小低频信号的通过能力,增加高频信号的通过能力。

2)电阻与电容并联的作用,是希望直流信号或者低频信号通过较困难,而交流信号或者高频信号较容易的通过。

3)在电容降压电路中,为了给电容器提供泄放通路,而在电容器两端并联一个泄放电阻。以便在停止工作后,泄放掉电容器两端存储的电能。

4)在耦合电路中,在耦合电阻两端并联电容器就组成了相位提前电路。这里,电容器的目的是为了与分布电容和下一级的输入电容组成分压电路,以避免这些电容形成的积分效应,从而使相位得以提前。

滤波电路中如何选择正确的电容类型

去耦电容相当于电池,满足驱动电路电流的变化,避免由于电流的突变而使电压下降,相当于滤纹波。具体容值可以根据电流的大小、期望的纹波大小、作用时间的大小来计算,去耦电容一般都很大。由于强调产品的物理尺寸,处理器制造商一般只规定满足器件能量转换要求所需要的电容量,而不考虑为适合的电容排列留置的可用空间。嵌入式单板计算机中所用的处理器还要求更高的电容充放电性能,从而要求一个低的时间常数。

随着电容制造向更小型化封装应用的继续推进,一种高电容量、低ESR及低电压应用的理想方案是3-D多阳极涂层(conformal coated)片式电容。

Polymer钽电容

Polymer钽电容运用了新式高导电性的聚合物。高导电性聚合物用于阴极而非二氧化锰。聚合物阴极在导电率上的改善带来更低的阻抗和更低的ESR。低阻抗还带来优异的高频滤波响应。Polymer钽电容技术拥有最低的ESR,大大低于相近尺寸的常规固体钽电容。事实上,引线框结构主要制约给定外形尺寸下可用电容量。

多阳极钽电容

现今,高容积和低ESR的双重要求正在由一种3-D的封装方式来解决,它是一种多阳极钽电容,该结构去除了常规的引线框。此结构在小型化SMD封装下取得了高电容量,并可以与常规模压钽器件引脚兼容。重要的是,该技术取得了非常低而稳定的ESR。

高电容:一般》1000 F ;

工作温度范围内非常低而稳定的ESR ;

低电感;

宽的额定电压范围:4V、6.3V及10V ;

低DCL 《 60 A ;

小尺寸、低厚度3D片式封装 ;

无引线框;

标准引脚,与常规模压钽电容尺寸兼容

体去耦电容应用

当今大量的嵌入式控制器是采用一种单板计算机(SBC)建立的。主导性的工业标准是PC/104,它规定了3.8” x 3.6”的形状系数。新的更小的专有规格也在涌现,特别是基于16位和32位处理器的SBC。此外,PC/104 SBC还必须做到多个PC/104板的stack-through(堆叠嵌入)连接,以充分利用4.0mm(0.16”)的最大安装元件高度。

高电容量和低ESR技术

有多种技术已可实现单位体积电容量的优化。例如,涂层片式钽电容技术,该技术去除了常规模压固体钽电容的引线框结构,同时这种类似于半导体特殊封装的技术大大降低平均尺寸。 Vishay已经开发了涂层钽片式技术,用于满足NASA要求的电容使用。这些产品远远超过了常规模压表面安装钽电容(SMD)的容积效率。不过设计师们还需要使ESR最小化,而这一要求刺激了多种候选方案。

Polymer铝电容

Polymer铝电容具有非常低的ESR,在10 m 或更小的范围,它填充了高电容量多层陶瓷电容(MLCC)和钽聚合物电容之间的应用空间。不过,尽管它们满足了滤波应用中所需的ESR要求,但它们的容积效率通常要比钽技术小很多。在组装空间十分珍贵的应用中,这种技术必须让位于其它技术如钽式技术等。

固体钽电容

固体钽电容有标准和低ESR两种类型。两种类型均采用通常的引线框结构制作。固体钽低ESR类型所具有的ESR值100 KHz 时在100 m 范围。由于ESR值取决于阳极的外表面,因此较大的外形尺寸一般都拥有较低的ESR值。固体钽电容方面大量的粉末研制工作产生了新的更低水平的ESR值。另外浪涌电压方面也得到改进使固体钽技术功能更强大。

滤波电容的选择比较

相当数量的设计师还倾向于用一个微控制器或微处理器加选定外围元件,做自己的定制嵌入式控制器方案。这些方案或许可以在PCB上直接实现,同普通SBC一样也受到压缩空间的限制。

所以,材料和封装结构必须做到使一个电容适合装入CPU和芯片组之间的十分小的空间,而不超出严格的高度限制。

功率要求通常由微处理器或微控器制造商根据电压调节模块(VRM)而制定。大多数系统根据一个能提供多个电压值的同步降压转换器建立。通常,它们将提供1.5~1.8V、3.3V及5.0V的电压,分别给处理器核心、处理器与芯片组I/O,以及通用板上各个基础电单元。处理器核心电压或VCORE,通常是选择低ESR体电容时的一个主要难点。对合适电容技术的评估

分析处理器制造商对有关核心电压的推荐建议,例如为VCORE指定一个适合的滤波电容。要求1.5V核心电压的新式处理器,其例举要求如下:

输出电压=1.5V~1.8V;

输出纹波电压=输出电压的2%;

输出电流》14A;

输出滤波电容=3900F/4V,ESR《3m

调查该新封装技术的效果,对前面描述的电容技术进行了评估,以确定作为一种PC/104SBC用整体输出滤波电容在板布局、元件高度、电气性能方面的最佳技术。不过,由于现有铝电解电容超出了4.0mm(0.16”)的最大高度,因此被排除在外。

多阳极技术以最小占用空间、拥有最好的ESR,被选择用于此应用。4个多阳极597D并联安装在板上,占用面积124mm2(0.19inch2)。这产生了与其它技术相比更好的容积效率。并联电容布置的ESR《3m,满足目标应用要求。

虽然Polymer钽电容具有很好的ESR,但总体电容值需求要求更多的单个贴装电容。为取得必需的体电容量,需要18个255D系列的330F,占用板空间总量为558mm2(0.88inch2)。这大大高于4个Vishay597D多阳极钽电容构成的排列。

通观各电容技术以确定印刷电路板(PCB)上最小总引脚、具有最低的ESR,同时满足高度限定的实现方案。