�������ŵ��Ӽ����ر������ּ��ɵ�·������Ѹ�ͷ�չ�������ϳ�����FPGA��CPLD�ȴ��ģ���ּ��ɵ�·�������乤���ٶȺͲ�Ʒ����������ߡ����ô��ģ���ּ��ɵ�·ʵ�ֳ���ĵ���̬���ɵ�·��ʵ�ֵĹ��ܣ�����������ȡ����Ⱥ��¶��ȶ��Է����Ҫ����ʵ���������öࡣ���棬���߾�����ڴ��ģ���ּ��ɵ�·�н������խ�����ź�չ���ɾ���һ�����Ⱥ;��ȵĿ������ź���һ��ϸ���ܡ�

����1 ����CPLD�����ĵ���̬����չ����·

�������ڶ��CPLD�����У�LatTIce��˾��GAL����������isp������������һϵ��ispLSI���߿ɱ��������(���¼��isp����)����ԭ�����ص���������־�����б��������ҹ��������൱��ĵ�·�����Ա�dz���Ϥ��Lattice��˾��isp����������ӡ����������乤���Ŀɿ��ԱȽϸߡ�ͼ1����һ�ֽ������խ�����ź�չ���ɾ���һ�����Ⱥ;��ȵĿ������źŵĵ�·ԭ��ͼ��

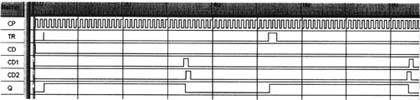

����ͼ�У�TRΪ�����խ�����״��źţ�CPΪ�����ϵͳʱ�������źţ�Q���ǵ���̬����չ����·����Ŀ������źš�ͼ�еĵ�Ԫ��·����D1����չ�������ǰ�ز�����·������չ����������γɵ�·��D2��D3�Ƕ����Ƽ���������Ҫ����չ������Ŀ��ȿ��Ƶ�·�����ݶ�������ȵIJ�ͬҪ���Բ��ò�ͬλ���Ķ����ƻ��������Ƶļ����� (���������ȵ����ֵ��3.2��s����CP���������ֵ��0.1��s)��D4��չ��������ز�����·����������D3�Ľ�λ�����NQΪ���ߣ�����CP����������ص���ʱ��D4��������һ���������źţ���D5����D1��CD"����"�ˣ��Ӷ�������һ��խ�����źŵ�չ�����̣���D1��Q��������һ������չ�������źš�ͬʱ��D5������źŻ�����D2��D3��CD"����"�ˣ�����"����"�ȴ���һ��խ����ĵ�������ͼ1��ʾ�ĵ�·ԭ��ͼ�п��Կ�����ͨ�����Խ�D3�Ľ�λ����ź�NQֱ������D5����ˣ���ΪD1��D2��D3��"����" �����źš�

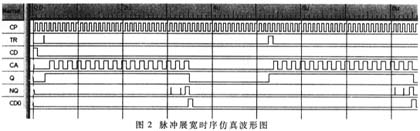

��������ͼ2��ʾ��ʱ����沨���п��Կ�����D3�Ľ�λ���NQ�����У����������Ľ�λ�����ź�����⣬����ǰ�滹�п��Ⱥ��������ȵĸ���խ���塣�����NQ���徭D5��ֱ����ΪD1��"����"�źţ���չ������Ŀ��Ƚ��ܸ���խ�����Ӱ������ȶ�����Ϊisp�����д�������"����"�����������첽���еġ�����D4��ֻ�������ʱ���������ͬ����ϵ���Ǹ���λ���壬������D4��������γ�"����"���塣��������ȫ�ų�����Щ����խ�����Ӱ�죬�Ӷ���֤��չ��������ȵ��ȶ��Ժ�ȷ�ԡ�ͼ2����������չ����ʱ����沨��ͼ�����õ�������Lattice��˾��ispLSI1032/883-64PIN��PGA��װ������

����2 ����CPLD��������չ����·���ص�

����������ĵ�·ԭ��ͼ��ʱ����沨��ͼ���Կ���������isp�������ɵ�����չ����·���������ص㣺

����(1)�����������źŵĿ�����Ӧ������ǿ����խ���Ե�ns������������������õ�CPLD�����Ĺ����ٶ��йء���ˣ��ر������ڶ�խ�����״��źŽ���չ����

����(2)չ������Ŀ��ȿ��Ը�����Ҫ�����趨����ɸı��·(�����뵥Ƭ������)��ʹ�������ֳ�ʵʱ�Զ����ء�

����(3)չ������Ŀ����ȶ���ȷ���������R��C��ʱԪ��������������Ƚ��������õ�ʱ��Ƶ�ʺ�CPLD�����������йء�

����(4)չ�������ǰ��������խ�����ǰ��֮����ӳ�ʱ������㶨��������ӳ�ʱ�����źŴ�D1��ʱ������˵�D1�������Q���ӳ�ʱ�䡣

����(5)��·���Լ�����Ҫ����չ������Ŀ���ʱ���������Ԫ������ֻҪ��������ơ�����ͨ�����JED��˿ͼ�ļ���ͨ�����ص�����ʱ���ص�CPLD�����ڼ��ɡ����ڶԵ�·���иߡ����µ���������ʱ��ü�Ϊ�������Ч��

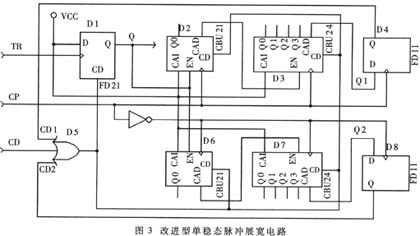

������ͼ1�����Կ��������ֵ���̬����չ����·����������������С��"+"��"-"һ��CPʱ�����ڡ���Ҫ���չ��������ȵľ��ȣ����Բ���ͼ3��ʾ�ĸĽ��͵���̬����չ����·������ͼ����·�Ļ����ϣ�������isp������ʱ�������źž��������������Ϊ��һ����ͬ�������Ƶ�·�ļ�������ʱ�����塣

��������������խ������ʱ�������ǰ�������ڵ������D6��D7��D8��ɵ��������Ƶ�·�ȿ�ʼ��������������խ������ʱ������ĺ�������ڵ������D2��D3��D4��ɵ��������Ƶ�·�ȿ�ʼ�������������������������Ƶ�·��ʱ�����ֵ����ͬ�ģ����ȼ������Ƚ����������������������֮��Ϊ���ʱ������ֵ��չ�������źŵĿ��ȣ�ʼ������խ�����ǰ�أ���ֹ�������������Ƶ�·�����������ʱ�������Ǹ��������Ľ�λ������������"����"�����źš���ˣ���������խ�����źŵ�ǰ����ʱ����������ʱ���ϵ��Σ������չ������Ŀ���Ϊ�������Ƶ�·��ʱ�����ֵ������խ�����ǰ�ؼ���ʱ�������ǰ�ػ����֮������������Ƽ�����·��ʱ����������û�иı䣬����������խ�����ǰ������Ƽ�����·ʱ�����������ص����ʱ��ֻ�а��ʱ����������(ע�⣺ʱ�������źŵ�ռ�ձ�Ϊ1:1)����չ�������źŵĿ������С�ڣ�+����"-"���ʱ���������ڡ�ͼ4��ͼ3��ʾ��·��ʱ����沨��ͼ��

��������������խ������ʱ�������ǰ�������ڵ������D6��D7��D8��ɵ��������Ƶ�·�ȿ�ʼ��������������խ������ʱ������ĺ�������ڵ������D2��D3��D4��ɵ��������Ƶ�·�ȿ�ʼ�������������������������Ƶ�·��ʱ�����ֵ����ͬ�ģ����ȼ������Ƚ����������������������֮��Ϊ���ʱ������ֵ��չ�������źŵĿ��ȣ�ʼ������խ�����ǰ�أ���ֹ�������������Ƶ�·�����������ʱ�������Ǹ��������Ľ�λ������������"����"�����źš���ˣ���������խ�����źŵ�ǰ����ʱ����������ʱ���ϵ��Σ������չ������Ŀ���Ϊ�������Ƶ�·��ʱ�����ֵ������խ�����ǰ�ؼ���ʱ�������ǰ�ػ����֮������������Ƽ�����·��ʱ����������û�иı䣬����������խ�����ǰ������Ƽ�����·ʱ�����������ص����ʱ��ֻ�а��ʱ����������(ע�⣺ʱ�������źŵ�ռ�ձ�Ϊ1:1)����չ�������źŵĿ������С�ڣ�+����"-"���ʱ���������ڡ�ͼ4��ͼ3��ʾ��·��ʱ����沨��ͼ��

������ʱ����沨��ͼ�п��Կ�����ǰ������������խ�����ǰ�����Ӧ�� չ�������źŵ�ǰ��֮����ӳ�ʱ����һ���ġ���չ�������źŵĺ��������������������Ƽ�����·�����Ƚ����������Ǹ��������Ľ�λ������������"����" �����ź����Ӧ�ġ��Ӷ�֤ʵ�˲���ͼ3��ʾ��·�������������źŵĿ��Ⱦ�ȷ�Ƚ�ͼ1��ʾ֮��·�������һ�������ⲿ�������������£����չ�������źž��ȵķ����ж��֣����ﲻ��һһ���١�

������CPLD�����У����Խ������խ����չ������Ȼ������Խ�����Ŀ������խ����ʹ�������54HC123����̬��������������ʱ�Ϳ��ش������ܡ���CPLD��������ʵ�ֳ��õ���̬��·�Ĺ��ܣ���FPGA������ͬ������ʵ���������ܡ����ú����������ַ�������Ҫ����·��Ƶļ���ָ�꣬����������е���ƻ�������Χ��·����ʹ�����������͡���֮�����Ŵ��ģ���ɵ�·��Ʒ���ܵIJ�����ߡ�����IJ��ϼ�С�ͳɱ��IJ��Ͻ��ͣ�����CPLD������Ƶĵ���̬��·�����ܽ������ߣ����ֵ���̬��·��Ӧ���ཫԽ��Խ�㷺��