基于FPGA的数据采集控制模块设计

0 引 言

数据采集和控制系统是对生产过程或科学实验中各种物理量进行实时采集、测试和反馈控制的闭环控制,它在工业控制、军事电子设备、医学监护等许多领域发挥着重要作用。其中,数据采集部分尤为重要,而传统的数据采集系统,通常采用单片机或DSP作为控制器,用以控制ADC、存储器和其他外围电路的工作,使得采集速度和效率降低。近年来,微电子技术,如:大规模集成电路和超大规模集成电路技术的发展,为数据采集系统的发展提供了良好的物质基础。从而使器件向模块化和单片化发展,使所用软件均向实时高级语言和软件模块化发展,接口向标准化发展。由于FPGA时钟频率高,内部延时小,全部控制逻辑均由硬件完成,速度快,效率高,同时它有非常强大的硬件描述语言和仿真工具,方便检验结果的正确性。基于以上考虑,在设计中采用FPGA作为控制处理器。而VGA接口的设计,更突出了该模块的兼容性,更易于采集数据的直观表现。

1 系统总体设计方案

完整的数据采集过程通常由数据的通道选择、采样、存储、显示构成,有时也要对数据进行适当的处理。其中,控制模块起到了核心作用,他作为控制信号产生和处理的中枢对这些外围电路进行着实时的监控和管理。设计过程中采用FPGA作为控制器,完成对A/D转换器的控制,并将采集到的数据存储到一定的存储单元.通过VGA接口协议,最后在显示器上显示。具体涉及的外围电路中,数据采集部分主要应用ADC0809作为数据采集芯片,对输入的模拟量进行A/D转换;数据缓存部分应用6116作为存储芯片,用来缓存0809采集的数据;按键控制部分利用8个按键来控制0809的转换通道选择;图形显示部分输出标准的VGA信号,使用CRT显示器,以显示实时波形。由于在设计中对外部器件进行控制的控制器都是由FPGA完成的,FP-GA的工作量很大,因此所采用的FPGA芯片为FLEX系列中30万门的EPF10K30。

2 基于FPGA的主控模块的实现

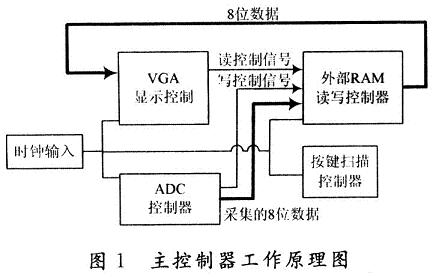

主控制器的工作原理如图1所示。

通过一个A/D转换控制器产生对ADC0809的控制信号。启动ADC0809之后,随即就会按照一定频率进行A/D转换。同时通过一个数据锁存信号将数据锁存到A/D转换控制模块中。这个锁存信号将作为RAM控制器写输入控制信号。当RAM读写控制器的写控制信号有效之后,将开启RAM的写使能有效信号,将采集到的数据写入RAM的第600个地址单元中,然后RAM控制器将RAM中的数据向上移动一位,移动完之后,产生一个数据更新完毕信号,之后才通过内部的一个控制信号,允许从RAM读出数据。若RAM中读数据使能,每当VGA显示控制器发出一个读数据命令时,RAM读写控制器便开启RAM的读有效信号,读出RAM中的数据,并且通过VGA控制器的时序控制和输出信号进行显示。外部的按键部分共有8个,这8个按键控制ADC0809的8路通道的选择。键盘控制器的功能就是扫描所按下按键的行和列值,并且合成键值。转换成按键数值0~7,最终控制8个模拟输入通道的选择。

2.1 VGA显示控制器的设计

常见的彩色显示器一般由阴极射线管(CRT)构成,彩色是由红、黄、蓝(R,G,B)三基色组成的,用逐行扫描的方式解决图像显示。其引出线共含5个信号:R,G,B三基色信号;HS;行同步信号;VS;场同步信号。

对于VGA显示器的这五个信号的时序驱动要严格遵循“VGA工业标准”,即640×480×60模式,否则会损害VGA显示器。在此,控制器共有2个输入信号,6个输出信号。CLK连接到外部的晶振上,其晶振频率是50 MHz。由于VGA工业标准所要求的晶振频率是25 MHz。因此,在此控制器中首先要将时钟进行二分频。RD是一个8位的数据量,它接收从RAM读出的数据。输出信号READ用于控制RAM控制模块开启RAM的读有效信号,只要READ有变化,那么将进入读数据状态,由RD接收读出来的数据。HS和VS分别是行同步信号和场同步信号,R,G,B为三条输出的信号线。显示波形是通过改变R,G,B这三条输出信号的值来实现的。

每读出一个数据,其实是对应着一个像素点。由于这里所采集的电压值范围是0~5 V,对应ADC0809转换成的数据量是0x00~0xFF、,所以在设计时只要将RD接收的具体数值与显示器中的某一行相对应即可,具体实现用比较语句就可以实现行定位,同时列辅助寄存器LLV加1即可,这样即可实现连续波形。这些点连接起来就是一个完整的波形,而其中行同步和场同步信号的产生则分别由内部信号CC,LL根据已知的输入时钟,通过计数器计数的方式,达到工业标准要求的频率。

2.2 A/D转换控制器的设计

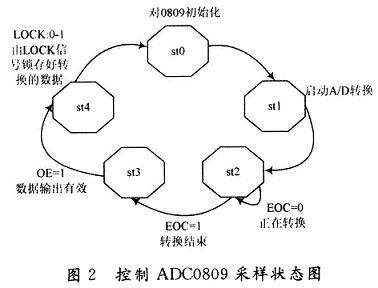

在此设计中,是利用状态机对A/D转换进行控制的。控制ADC0809采样状态图,如图2所示。

在状态ST0中,对0809进行初始化,之后进入到状态ST1;在状态ST1中,ALE和START信号有效,这时EOC信号变为低电平,进入转换状态ST2。此时,需要对0809工作状态信号EOC进行测试,如果为低电平,表示转换没结束,仍需要停留在ST2状态中等待,直到变成高电平后才说明转换结束,在下一时钟脉冲到来时转向状态ST3。在状态ST3,由状态机向0809发出转换好的8位数据输出允许命令,这一状态周期同时可作为数据输出稳定周期,以便能在下一状态中向锁存器中锁入可靠的数据。在状态ST4,由状态机向FPGA中的锁存器发出锁存信号,将0809输出的数据进行锁存。

2.3 RAM读写控制器的设计

在该模块设计中,RAM读写控制模块又分为读控制模块、写控制模块和读写状态转换模块。写控制模块中两个输入信号分别与A/D转换控制模块的数据锁存和转换输出相连。当锁存信号使能,即发出写信号,将数据存储到外部RAM的第600个地址空间之后,再对之前的数据进行前移,以达到数据的及时更新。读控制模块的控制信号分别与写更新完毕信号和读信号相连,当写更新完毕信号使能时,只要接到读信号,则依次读完外部RAM前600个地址空间(一场)的数据。

2.4 键盘扫描控制器的设计

键盘控制模块由四个模块组成,包括:时钟分频模块、行键值输出模块、键值锁存模块和键值合成模块。键值锁存模块将按下按键的行、列信息锁存,并交由键值合成模块,该模块配合行键输出模块输出的结果进行查表,最终确定键值。

3 仿真结果

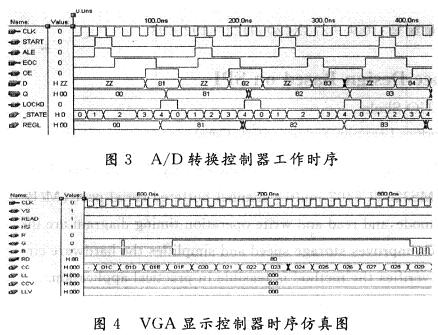

Max+PlusⅡ仿真平台的图形输入方式直观,符合传统数字系统设计人员的习惯,便于进行接口的设计,容易实现仿真,便于信号的观察。基于以上考虑,利用此平台,用硬件描述语言VHDL来实现各个功能模块,A/D转换控制器和VGA显示控制器模块的时序仿真结果如图3、图4所示。

4 结 语

这里的数据采集控制模块主要以FPGA为基础,本着软件硬件化的思路,着重研究主控制模块的实现。由于采用FPGA作为控制处理器,其速度快,效率高,且标准的VGA接口使得系统的使用更加便捷,键盘控制的多通道间切换,也为实现多路采集奠定了基础。

<-- 2010/2/6 10:17:12-->