概述:

在各种复杂的数字电路中,不但需要对二值信号进行算术运算和逻辑运算,还经常需要将这些信号和运算结果保存起来。为此,需要使用具有记忆功能的基本逻辑单元。能够储存1位二值信号的基本单元电路统称为触发器。

u 触发器的特点:

① 具有两个能自行保持的稳定状态,用来表示逻辑状态的0和1,或二进制数的0和1。

② 根据不同的输入信号可以置成1或0状态。

u 触发器分类

§4.1 触发器

一、 基本RS触发器

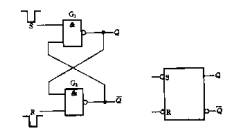

基本RS触发器是触发器中电路结构最简单的一种,它也可以是其它触发器的基本组成部分,即最基本的逻辑单元。可以用两个或非门或两个与非门交叉耦合构成。

1. 用与非门构成的基本RS触发器

(1) 电路构成和工作原理

基本RS触发器的电路结构和图形符号

用两个与非门构成的基本RS触发器,其R、S为触发器的两个输入端,又称为激励端,R称为直接复位端(置0端),S称为直接置位端(置1端)。  和

和  是两个互补输出端,一般用

是两个互补输出端,一般用  端的逻辑值来表示触发器的状态,即

端的逻辑值来表示触发器的状态,即  称触发器处于1状态,而

称触发器处于1状态,而  称触发器处于0状态。(规定

称触发器处于0状态。(规定  表示触发器的现态,

表示触发器的现态,  表示触发器的次态)

表示触发器的次态)

根据电路中的与非逻辑关系,可以得出以下结论:

Ⅰ.当R=1、S=0时,  ,

,  触发器处于置位状态。此时,S=0是

触发器处于置位状态。此时,S=0是  的决定性条件。

的决定性条件。

Ⅱ.当R=0、S=1时,  ,

,  触发器处于复位状态。此时,R=0是

触发器处于复位状态。此时,R=0是  的决定性条件。

的决定性条件。

Ⅲ.当R=1、S=1时,  ,即两个与非门的状态由原来触发器的状态决定,此时触发器维持原来状态不变,体现了触发器的记忆功能。

,即两个与非门的状态由原来触发器的状态决定,此时触发器维持原来状态不变,体现了触发器的记忆功能。

Ⅳ.当R=S=0时,  ,

,  触发器的输出为不定状态,这种情况应该避免。

触发器的输出为不定状态,这种情况应该避免。

逻辑符号中输入端小圆圈表示“低电平有效”,输出端小圆圈表示“反相输出”。

(2)基本RS触发器的特性表 :

|

S |

R |

Qn |

Qn+1 |

|

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

|

0 |

0 |

0 |

不定 |

|

0 |

0 |

1 |

不定 |

二、同步RS触发器

在数字系统中,为协调各部分的动作,常常要求某些触发器于同一时刻动作。为此,必须引入同步信号,使这些触发器只有在同步信号到达时,才按输入信号改变状态。通常把这个同步信号叫做时钟脉冲,简称时钟,用CP表示(Clock Pulse)。CP是触发器(时序电路)的输入信号。实现时序控制的最简单方式如下图。该电路的组成部分:与非门G1、G2组成的基本RS

同步RS触发器电路结构和逻辑符号图

触发器和G3、G4组成的输入控制电路。

同步RS触发器特性表即分析如下:

|

CP |

S |

R |

|

|

分析: |

||

|

0 0 |

X X |

X X |

0 1 |

0 1 |

保持(CP=0时,门G3、G4截止,输入信号S、R不会影响输出端状态,故触发器保持原来状态不变 |

||

|

1 1 |

0 0 |

0 1 |

0 1 |

0 1 |

保持(此时 |

||

|

1 1 |

1 1 |

0 1 |

0 1 |

0 0 |

与 S 相 同 |

|

|

|

1 1 |

0 0 |

0 1 |

0 1 |

1 1 |

|

||

|

1 1 |

1 1 |

0 1 |

0 1 |

- - |

不定 |

此时G3,G4输出均为0,与基本RS触发器中R=S=0情况相同 |

|

如果用逻辑表达式描述同步RS触发器逻辑功能,可以得到其特性方程。

u 同步RS触发器的动作特点:

在CP=1的全部时间里S和R的变化都将引起触发器输出端状态的变化。据此,可以想象:如果CP=1的期间内输入信号多次发生变化,则触发器的状态也会发生多次翻转,这就降低了电路的抗干扰能力。为了提高触发器工作的可靠性,希望在每个CP周期里输出端的状态只能改变一次。为此,在同步RS触发器的基础上又设计出了主从触发器。

三、 主从触发器

1. 主从RS触发器

电路结构图

主从RS触发器电路结构和逻辑符号

主从触发器由两级触发器构成,其中一级接收输入信号,其状态直接由输入信号决定,称为主触发器;还有一级的输入与主触发器的输出连接,其状态由主触发器的状态决定,称为从触发器。工作原理:

Ⅰ. CP=1时,G7、G8被打开,G3、G4被封锁,此时主触发器根据S和R的状态翻转而从触发器保持原来的状态不变。

Ⅱ. CP由  后,G7、G8被封锁,此后无论S、R的状态如何改变,在CP=0的全部时间里主触发器的状态不再改变。与此同时,G3、G4被打开,从触发器按照与主触发器相同的状态翻转。

后,G7、G8被封锁,此后无论S、R的状态如何改变,在CP=0的全部时间里主触发器的状态不再改变。与此同时,G3、G4被打开,从触发器按照与主触发器相同的状态翻转。

∴ 在CP的一个变化周期中,触发器输出端的状态只可能改变一次。

例如:  0时触发器初始状态为

0时触发器初始状态为  ,当CP由

,当CP由  后,若S=1,R=0则主触发器被置1,即

后,若S=1,R=0则主触发器被置1,即  ,

,  而从触发器保持0状态不变。当CP回到低电平以后(

而从触发器保持0状态不变。当CP回到低电平以后(  ),

),  ,

,  ,

,  则从触发器被置成

则从触发器被置成  。

。

² 注:从同步RS触发器到主从RS触发器的这一演变,克服了CP=1期间触发器输出状态可能多

次翻转的问题。但由于主从触发器本身是同步RS触发器构成的,所以在CP=1期间  和

和  的状态仍然会随S、R状态变化而多次改变,而且输入信号也必须遵守RS=0的约束条件。

的状态仍然会随S、R状态变化而多次改变,而且输入信号也必须遵守RS=0的约束条件。

为了使用方便,希望即使出现了S=R=1的情况,触发器的状态也是确定的,因而需要进一步改进触发器的结构。

如果把主从RS触发器的  和

和  端作为一对附加的控制信号接回到输入端,就可以达到上述要求。这一对反馈线通常在制造集成电路时一再内部连好。为表示与主从RS触发器在逻辑功能上的区别,以J、K表示两个信号输入端,并将其称为主从JK触发器。

端作为一对附加的控制信号接回到输入端,就可以达到上述要求。这一对反馈线通常在制造集成电路时一再内部连好。为表示与主从RS触发器在逻辑功能上的区别,以J、K表示两个信号输入端,并将其称为主从JK触发器。

2. 主从JK触发器

主从JK触发器电路结构和逻辑符号

工作原理:

Ⅰ. J=1,K=0 则 CP=1时主触发器置1

(原来是0则置成1,∵设  且

且  推出

推出  ,此时相当于基本RS触发器

,此时相当于基本RS触发器  的情况;原来是1则保持1,∵

的情况;原来是1则保持1,∵  且

且  推出

推出  ,此时相当于基本RS触发器

,此时相当于基本RS触发器  的情况)

的情况)

待CP=0以后从触发器亦随之置1,即  。

。

Ⅱ. J=0,K=1 则CP=1时主触发器置0,待CP=0以后从触发器也随之置0,即  。

。

Ⅲ. J=K=0 则由于G7和G8门被封锁,触发器保持原状态不变,即  。

。

Ⅳ. J=K=1则需要考虑两种情况:

①  :此时G8被

:此时G8被  端的低电平封锁,CP=1时,仅G7输出低电平信号,故主触发器置1;CP=0以后从触发器也跟着置1,即

端的低电平封锁,CP=1时,仅G7输出低电平信号,故主触发器置1;CP=0以后从触发器也跟着置1,即  。

。

②  :此时G7被

:此时G7被  端的低电平封锁,因而在CP=1时仅G8能给出低电平信号,故主触发器被置0;CP=0以后从触发器跟着置0,即

端的低电平封锁,因而在CP=1时仅G8能给出低电平信号,故主触发器被置0;CP=0以后从触发器跟着置0,即  。

。

综合上述两种情况,  即J=K=1时CP下降沿到达后触发器将翻转为与现态相反的状态。

即J=K=1时CP下降沿到达后触发器将翻转为与现态相反的状态。

3. 动作特点:

Ⅰ. 触发器的翻转分两步动作。第一步,在CP=1期间主触发器接收输入端(S、R或J、K)的信号,被置成相应的状态,而从触发器不动;第二步,CP下降沿到来时从触发器按照主触发器的状态翻转,所以  断状态的改变发生在CP的下降沿。

断状态的改变发生在CP的下降沿。

Ⅱ. 因为主触发器其本身是一个同步RS触发器,所以在CP=1的全部时间里输入信号都将对主触发器其控制作用。

因此,在使用主从触发器时必须注意,只有在CP=1的全部时间里输入状态始终未变的条件下,用CP下降沿到达时输入的状态解决触发器的次态才肯定是对的,否则,必须考虑CP=1期间输入状态的全部变化过程,才能确定CP下降沿到达时触发器的次态。

例:已知主从JK触发器的CP,J,K波形如图,设触发器的初始状态为Q=0,试画出Q端输出波形。

解:1)第一个CP高电平期间始终为J=1,K=0,CP下降沿到达后触发器置1。

2)第二个CP高电平期间K端状态发生过变化,因而不能简单的以CP下降沿到达时J,K的状态来决定触发器的次态。因为在CP高电平期间出现过短时间的J=0,K=1状态,此时主触发器便被置 0,所以虽然CP下降沿到达时输入状态回到了J=K=0,但从触发器仍按主触发器的状态被置0,即  。

。

3)第三个CP下降沿到达时J=0,K=1,如果以这时的输入状态决定触发器状态,应  。但是由于CP高电平期间曾出现过J=K=1状态,CP下降沿到达之前主触发器已被置1,所以CP下降沿到达后从触发器被置1。

。但是由于CP高电平期间曾出现过J=K=1状态,CP下降沿到达之前主触发器已被置1,所以CP下降沿到达后从触发器被置1。

为了提高触发器的可靠性,增强抗干扰能力,希望触发器得次态仅仅取决于CP信号的下降沿(或上升沿)到达时刻输入信号的状态。而在此之前和之后输入状态的变化对触发器的次态没有影响。为实现这一设想,人们相继研制成了各种边沿触发器电路。

四、边沿形触发器

1. 维持阻塞触发器

这是边沿触发器的一种电路结构形式,在TTL电路中常用该形式。下面给出维持——阻塞式边沿D触发器的逻辑图和逻辑符号。

维阻型触发器电路结构和逻辑符号

该触发器由6个与非门构成,其中G1和G2组成基本RS触发器。分析工作原理:

Ⅰ.  时,不论输入端D为何种状态,都会使

时,不论输入端D为何种状态,都会使  ,即触发器置1。

,即触发器置1。

时,不论输入端D为何种状态,都会使

时,不论输入端D为何种状态,都会使  ,即触发器置0。

,即触发器置0。

因此,SD 和RD 通常称预置端和清零端。

Ⅱ. 当触发器工作时,必须使 SD =RD =1 ,

(1)CP=0时,G3 和G4 封锁,其输出Q3 =Q4 =1,此时基本RS触发器处于保持状态,即  状态不变。同时,由于Q3 至G5 和Q4至G6 的反馈信号将这两个门打开,因此可接收输入信号D,

状态不变。同时,由于Q3 至G5 和Q4至G6 的反馈信号将这两个门打开,因此可接收输入信号D,

。

。

(2)当CP由0变1时,即上升沿到来:G3 和G4打开,它们的输出Q3和Q4的状态由 G5和G6的输出状态决定。  ,

,  。由基本RS触发器的逻辑功能,可知Q=D.

。由基本RS触发器的逻辑功能,可知Q=D.

(3)触发器翻转后,在CP=1时输入信号被封锁。G3和G4打开后,他们的输出Q3 和Q4 的状态时互补的,即必定有一个是0,若Q3=0,则经G3输出至G5 输入的反馈线将G5封锁,即封锁了D通往基本RS触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。Q4=0 时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。Q4输出至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输出至G3 输入的反馈线起到了阻止触发器置0的作用,称为置0阻塞线。因此该触发器称为维持-阻塞触发器。

2. 利用传输延迟时间的边沿触发器

利用传输延迟时间的边沿触发器

这个电路包含一个由与或非门G1和G2组成的基本RS触发器和两个输入控制门G3和G4。而且,门G3和G4传输延迟时间大于基本RS触发器的翻转时间。

设触发器的初始状态为  ,

,  。

。

Ⅰ.  时,门B、B’和G3、G4被CP的低电平封锁,而G3、G4的输出P、P’均为高电平,

时,门B、B’和G3、G4被CP的低电平封锁,而G3、G4的输出P、P’均为高电平,

门A、A’是打开的,所以基本RS触发器的状态通过A、A’得以保持。

Ⅱ.CP变为高电平以后,门B、B’首先解除封锁,基本RS触发器可以通过B、B’继续保持原

状态不变。此时输入为  、

、  ,则经过门G3、G4的传输延迟时间后

,则经过门G3、G4的传输延迟时间后  、

、  ,门

,门

A、A’均不导通,对基本RS触发器的状态没有影响。

Ⅲ.当CP下降沿到达时,门B、B’立即封锁,但由于门G3、G4存在传输延迟时间,所以P、P’

的电平不会马上改变。因此,在瞬间出现A、B各有一个输入端为低电平的状态,使  ,

,

并经过门A’使  。由于G3的传输延迟时间足够长,可以保证在P点的低电平消失之前

。由于G3的传输延迟时间足够长,可以保证在P点的低电平消失之前  的

的

低电平已反馈到了门A,所以在P点的低电平消失以后触发器获得的1状态仍将保持下去。

经过门G3、G4的传输延迟时间以后,P、P’都变为高电平,但对基本RS触发器状态并无影响。而CP的低电平已将门G3、G4封锁,J、K状态即使再发生变化也不会影响触发器的状态了。

3. 边沿触发器的特点

不论是维阻型D边沿触发器还是利用传输延迟时间的JK边沿触发器,它们共同的动作特点就是触发器的次态仅取决于CP信号的上升沿或下降沿到达时输入的逻辑状态,而在这之前或之后,输入信号的变化对触发器输出的状态没有影响。这一特点有效的提高了触发器的抗干扰能力,因而也提高了电路的工作可靠性。

与基本RS触发器中R=S=1情况相同)

与基本RS触发器中R=S=1情况相同) G3输出1,

G3输出1,  G4输出0,与R=0,S=1情况相同

G4输出0,与R=0,S=1情况相同 G3输出0,

G3输出0,  G4输出1,与R=1,S=0情况相同

G4输出1,与R=1,S=0情况相同