MOS逻辑电路与前述的双极型逻辑电路相比具有如下特点:

① 制造工艺简单,集成度和成品率较高,成本较低;

② 工作电源允许变化的范围大,功率小;

③ 输入阻抗高,一般达500M  以上,扇出系数大;

以上,扇出系数大;

④ 抗干扰性能较好。

由于上述特点,MOS逻辑电路已成为与双极型逻辑电路并行发展的另一重要分支,它特别适合制造中、大规模集成器件。当前在微型计算机系统中,MOS逻辑电路的使用占有绝对优势。

一、MOS晶体管

MOS晶体管是MOS集成电路的基本元件。MOS管有N沟道场效应管(NMOS管)和P沟道场效应管(PMOS管)两种。

1. MOS晶体管

NMOS晶体管的结构如图2-3-1(a)所示。当栅极G与源极S之间电压  大于某个电压值

大于某个电压值  (称为开启电压)时,在漏极D与源极S之间形成N沟道,管子导通。当

(称为开启电压)时,在漏极D与源极S之间形成N沟道,管子导通。当  ≤

≤  时,漏极与源极之间无沟道形成,管子截止。NMOS管的转移特性和输出特性依次如图2-3-1(b)、(c)所示,其中

时,漏极与源极之间无沟道形成,管子截止。NMOS管的转移特性和输出特性依次如图2-3-1(b)、(c)所示,其中  >0。这种NMOS管称为增强型NMOS管。此外,还有一种耗尽型NMOS管,其开启电压

>0。这种NMOS管称为增强型NMOS管。此外,还有一种耗尽型NMOS管,其开启电压  <0。耗尽型NMOS管的转移特性与输出特性如图2-3-2所示。

<0。耗尽型NMOS管的转移特性与输出特性如图2-3-2所示。

(a) (b) (c)

图2-3-1 NMOS管结构及共特性

(a) (b)

图2-3-2 耗尽型NMOS管结构的特性

NMOS管的符号和等效电路如图2-3-3所示,(c)图VGS>VT,管子导通,K闭合;VGS≤VT,管子截止,K断开。

(a) 增强型 (b) 耗尽型 (c)

图2-3-3 NMOS管的符号和等效电路

2. PMOS晶体管

PMOS晶体管与NMOS晶体管的结构正好相反,其结构如图2-3-4(a)所示。当  (

(  即为开启电压)时,在源极和漏极间形成P沟道,管子导通。而当

即为开启电压)时,在源极和漏极间形成P沟道,管子导通。而当  ≥

≥  时,源极与漏极之间无沟道形成,管子截止。

时,源极与漏极之间无沟道形成,管子截止。

PMOS管也有增强型和耗尽型两种。增强型PMOS管的  ≤0,而耗尽型PMOS管的

≤0,而耗尽型PMOS管的  。PMOS管的符号、等效电路依次如图2-3-4(b)、(c)和(d)所示。

。PMOS管的符号、等效电路依次如图2-3-4(b)、(c)和(d)所示。

(a) (b)增强型 (c)耗尽型 (d)

图2-3-4 PMOS管的结构、符号和等效电路

无论是NMOS管还是PMOS管,都只有一种载流子导电,故称其为单极型晶体管。

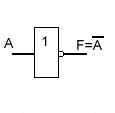

二、MOS反相器

1. 单沟道MOS反相器

MOS反相器是MOS数字集成电路的基本单元电路,如图2-3-5所示。该电路中,NMOS

图2-3-5 NMOS电阻负载反相器

管的漏极D是反相器的输出端,电阻  为反相器的漏极负载,栅极G是反相器的输入端,输入信号

为反相器的漏极负载,栅极G是反相器的输入端,输入信号  的电平控制了NMOS管的导通与截止,从而控制了输出电平

的电平控制了NMOS管的导通与截止,从而控制了输出电平  。

。

当  V(输入低电平)时,NMOS管截止,

V(输入低电平)时,NMOS管截止,  (输出高电平);当

(输出高电平);当  为正电压且大于开启电压(输入高电平)时,NMOS管导通,

为正电压且大于开启电压(输入高电平)时,NMOS管导通,  。因漏源间导通时的等效电组约为750

。因漏源间导通时的等效电组约为750  ,故适当地选择R,例如30K

,故适当地选择R,例如30K  ,可使

,可使  ,从而

,从而  V(输出低电平),因此该电路实现了反相功能。从逻辑角度看,若输入为A,输出F,则

V(输出低电平),因此该电路实现了反相功能。从逻辑角度看,若输入为A,输出F,则 。

。

但是,在硅片上生成几十千欧的电阻  ,占据面积太大,约为MOS管的20倍,对提高集成度极为不利,所以制造大规模MOS集成电路时很少采用电阻负载反相器。

,占据面积太大,约为MOS管的20倍,对提高集成度极为不利,所以制造大规模MOS集成电路时很少采用电阻负载反相器。

图2-3-6是用NMOS管作负载的反相器。图中  为驱动管;

为驱动管;  为负载管,其栅极直接与电源

为负载管,其栅极直接与电源  相联,且在制造时保证其漏源之间的等效电阻远大与驱动管的导通电阻。该电路的特点是负载管等效电阻

相联,且在制造时保证其漏源之间的等效电阻远大与驱动管的导通电阻。该电路的特点是负载管等效电阻  »

»  (驱动管导通电阻),以保证输出低电平的正确性。为此,负载管与驱动管的尺寸不会相同,且应满足一定的比例关系,通常把这种电路称作有比电路。

(驱动管导通电阻),以保证输出低电平的正确性。为此,负载管与驱动管的尺寸不会相同,且应满足一定的比例关系,通常把这种电路称作有比电路。

图2-3-6 NMOS管负载反相器

运用同样的原理可以构成电压极性完全相反的PMOS管负载反相器,其电路如图2-3-7。注:该电路的高、低电平分别为0V和  。与NMOS管一样,PMOS管负载反相器一定也是有比电路,以保证负载等效电阻远大于驱动管导通电阻。

。与NMOS管一样,PMOS管负载反相器一定也是有比电路,以保证负载等效电阻远大于驱动管导通电阻。

图2-3-7 PMOS管负载反相器

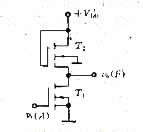

2. 互补MOS(CMOS)反相器

2-3-8图给出的MOS反相器电路中驱动管  是NMOS型,负载管

是NMOS型,负载管  是PMOS型,两者栅极相连作为反相器的输入;它们的漏极相连作为反相器的输出。

是PMOS型,两者栅极相连作为反相器的输入;它们的漏极相连作为反相器的输出。  的源极接至正电源

的源极接至正电源  ,

,  的源极接至电源的负端(接地),且使电源

的源极接至电源的负端(接地),且使电源  大于或等于两管开启电压绝对值之和。

大于或等于两管开启电压绝对值之和。

图2-3-8 CMOS反相器

工作原理:当  V时,

V时,  截止,

截止,  导通,

导通,  截止电阻为500M

截止电阻为500M  ,而

,而  导通电阻仅为750

导通电阻仅为750  ,故

,故  ;当

;当  时,

时,  导通,

导通,  截止,

截止,  导通电阻为750

导通电阻为750 ,而

,而  截止电阻为500M

截止电阻为500M  ,故

,故  V,实现逻辑功能

V,实现逻辑功能  。

。

这种形式的MOS电路与单沟道电路不同,在一个反相器中,同时存在两种沟道形式的MOS管,通常称为互补型MOS(CMOS)电路。显然在CMOS反相器中,无论电路处于何种工作状态, 和

和  中总有一个截止,因此它的静态功耗极低。在MOS电路中,为绝缘和隔离的需要,NMOS管的衬底应接电路中的最低电位,PMOS管的衬底应接电路中的最高电位。为简明起见电路图中将省略MOS管衬底的接线。

中总有一个截止,因此它的静态功耗极低。在MOS电路中,为绝缘和隔离的需要,NMOS管的衬底应接电路中的最低电位,PMOS管的衬底应接电路中的最高电位。为简明起见电路图中将省略MOS管衬底的接线。

三、 MOS门电路

在MOS反相器的基础上,可以构成各种MOS逻辑门。

1. NMOS门电路

图2-3-9为NMOS或非门电路。它实际上是具有两个并联的驱动管  和

和  的NMOS反相器。当输入A=B=0时,

的NMOS反相器。当输入A=B=0时,  和

和  均截止,输出F=1; 当A、B中至少有一个为1时,那么

均截止,输出F=1; 当A、B中至少有一个为1时,那么  和

和  中就至少由一个管子导通,F=0。显然该电路实现了

中就至少由一个管子导通,F=0。显然该电路实现了  的功能。以此类推,n个驱动管并联即可组成n输入或非门。

的功能。以此类推,n个驱动管并联即可组成n输入或非门。

图2-3-9 二输入端NMOS或非门 图2-3-10 二输入端NMOS与非门

图2-3-10为NMOS与非门电路,它由两个驱动管串连的反相器组成。不难分析出该电路实现了  的功能。同样,n个驱动管串联即可组成n输入端与非门。

的功能。同样,n个驱动管串联即可组成n输入端与非门。

PMOS逻辑门的组成及原理与NMOS相似,不同之处:①工作电源改为负极性②采用负逻辑来描述逻辑功能。用单沟道MOS管也可构成其他逻辑门(如与或非门、异或门等)。

值得指出的是,当MOS驱动管串联时(与非门),要求各串联管导通时的总的等效电阻必须远小于负载管的等效电阻,否则输出低电平就会被抬高,为此要仔细设计每只串联管的尺寸,对制造工艺极为不利。而MOS驱动管并联时(或非门),只会减小总的导通电阻,对输出低电平有利。因此,MOS集成电路中常采用或非门。

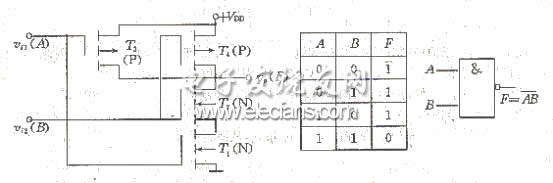

2. CMOS门电路

在CMOS反相器的基础上可以组成各种CMOS逻辑门。图2-3-11为二输入端CMOS与非门。图中  、

、  是两只串联的NMOS管,

是两只串联的NMOS管,  、

、  是两只并联的PMOS管,当输入

是两只并联的PMOS管,当输入  、

、  中有一个为低电平时,

中有一个为低电平时,  、

、  中就有一只管子截止,而

中就有一只管子截止,而  、

、  中有一只管子导通,输出

中有一只管子导通,输出  为高电平;只有当

为高电平;只有当  、

、  均为高电平时,

均为高电平时,  、

、  均为导通,

均为导通,  、

、  均截止,输出

均截止,输出  才为低电平,因此该电路实现了

才为低电平,因此该电路实现了  的逻辑功能。

的逻辑功能。

图2-3-11 CMOS与非门

下图为两输入端CMOS或非门,

图2-3-12 CMOS或非门

3. CMOS传输门

下图(a)为一种实现CMOS电路级间耦合的控制电路。它由一个NMOS管和一个PMOS管并联

(a) (b)

图 CMOS传输门

而成,两管并联连接的两端分别为传送信号的输入、输出端,两个管子的栅极分别由极性相反的信号  和

和  来控制。由于MOS管的结构和特性决定了它的源极和漏极可以互换,因此这个电路的输入,输出端也可以互换,它可以控制信息双向流通,就像一个双向开关。通常把这种CMOS控制电路称作CMOS传输门,其逻辑符号如上图(b)所示。工作过程:

来控制。由于MOS管的结构和特性决定了它的源极和漏极可以互换,因此这个电路的输入,输出端也可以互换,它可以控制信息双向流通,就像一个双向开关。通常把这种CMOS控制电路称作CMOS传输门,其逻辑符号如上图(b)所示。工作过程:

当  时,T1,T2均导通,传输门接通,信号畅行无阻;

时,T1,T2均导通,传输门接通,信号畅行无阻;

当  时,T1,T2均截止,传输门关闭,信号被阻隔。

时,T1,T2均截止,传输门关闭,信号被阻隔。

CMOS传输门的导通电阻与截止电阻相差甚大,当它驱动MOS负载时,接近于理想开关,可用来传输模拟信号,故又称为模拟开关,广泛用作数/模和模/数转换器及其他各种电路中的控制开关。

上图(a)所示的模拟开关中,由于控制信号  、

、  的高/低电平均为VDD/0V,因此,所能传输的模拟信号电平范围为0V~VDD。若VDD为5V,则模拟信号电平范围仅为0~5V.

的高/低电平均为VDD/0V,因此,所能传输的模拟信号电平范围为0V~VDD。若VDD为5V,则模拟信号电平范围仅为0~5V.

下图给出了一种改进型的CMOS模拟开关。即使控制信号Cin为0V/5V,它所能传输的信号电平范围仍达-15~15V。该电路采用的电平变换电路将输入0V/5V的外部控制信号Cin变换成-15/15V的内部控制信号  和

和  ,从而将通过该传输门的模拟信号电平范围扩展成为-15~15V。

,从而将通过该传输门的模拟信号电平范围扩展成为-15~15V。

图 改进型CMOS模拟开关

四、CMOS门电路的主要电气指标

CMOS电路示最常用的逻辑电路之一。现给出CMOS门电路的一些主要电气指标和测量方法以便正确使用CMOS电路。

1. 电压传输特性及有关性能参数

采用图2–47(a)所示的测量方法,可测出CMOS非门的传输特性,如图2–47(b)所示。

图2– CMOS非门的电压传输特性

由电压传输特性可得下列参数。

① 输出高、低电平VOH和VOL 显然VOH为VDD(最小值一般为0.99VDD);VOL为0V(最大值一般为0.01VDD),因此CMOS电路的逻辑摆幅较大,接近电源电压VDD值。

② 阈值电压VT 由于CMOS非门电压传输特性中输出高低电平的过渡区很陡,故阈值电压VT约为VDD/2。

③ 抗干扰容限 由图2–47(b)可见,CMOS非门的开门电平Von门电平Voff分别为0.45VDD和0.55VDD,因此其高、低电平抗干扰容限均达0.45VDD。其他CMOS门电路的抗干扰容限尽管不一定能达到非门的水平,但一般均大于0.3VDD.当电源电压VDD较大时,其抗干扰能力就很强。

2. 电源电压范围

标准CMOS电路的电源电压范围很宽,可在3~18V范围内工作,电源电压不同,CMOS电路的性能就不同。上述几个与电压传输特性有关的参数,基本上都与电源电压VDD呈线性关系。

3. 传输延迟与功耗

CMOS电路的功耗较小,传输延迟较大,且它们均与电源电压有关。下表列出了温度为

25℃且负载电容为50pF时,不同电源电压下CMOS非门的传输延迟和功耗。由表可见,电源电压越高,CMOS电路的传输延迟越小,功耗越大。

CMOS非门的传输延迟和功耗与电源电压的关系

4. 扇出系数

因CMOS电路有极高的输入阻抗,因此其扇出系数很大,额定扇出系数可达50。但是,

必须指出的是,扇出系数是指驱动CMOS电路的个数,若就灌电流负载能力和拉电流负载能力而言,CMOS电路远远低于TTL电路。

五、使用MOS集成电路的注意事项

尽管CMOS和大多数MOS集成电路输入端均有保护电路,但这些电路吸收的瞬时能量有限,过大的干扰信号也会破坏保护电路,甚至烧坏芯片。因此使用适应注意以下几点。

1. 焊接时,电烙铁外壳应接地。

2. 不能带电插拔集成块。

3. 因MOS电路输入阻抗极高,不用的输入端不能开路,以免感应较高的电压。应根据逻辑要求接电源(与非门)或接地(或非门)或与其他输入端并接使用。

4. 输出级所接电容负载不能大于500Pf,否则输出级功率过大会损坏电路。