ESD(静电放电)保护电路的设计是确保电子设备可靠性和寿命的关键环节。设计时需结合系统特性(如信号速度、电压、接口类型)和ESD标准(如IEC 61000-4-2)。以下是实现ESD保护电路设计的详细步骤和要点:

一、ESD保护核心原则

- 低阻抗泄放路径:提供比内部电路更低阻抗的路径到地(GND)或电源(VCC)。

- 快速响应:保护器件响应时间需远小于ESD事件持续时间(<1ns)。

- 箝位电压足够低:保护期间电压必须低于被保护电路的最大耐受电压。

- 无信号干扰:不影响信号完整性(如电容负载、漏电流)。

二、设计步骤

1. 识别保护需求

- 接口分析:列出所有外部接口(USB、HDMI、电源、按键等)。

- ESD等级要求:参考行业标准(如IEC 61000-4-2 Level 4: ±8kV接触放电)。

- 被保护电路特性:确定敏感器件的耐受电压(如MCU引脚耐压5V)。

2. 选择保护器件

| 常用器件及适用场景: | 器件类型 | 特点 | 适用场景 |

|---|---|---|---|

| TVS二极管 | 响应快(ps级),电容可选(0.2pF~100pF) | 高速信号(USB, HDMI, RF) | |

| ESD抑制器 | 低电容(<0.5pF),多通道集成 | 高速差分线(以太网、MIPI) | |

| 压敏电阻(MOV) | 通流能力强,但电容大(>100pF) | 电源线、低速接口 | |

| 聚合物ESD器件 | 自恢复,无漏电流 | 高可靠性场景 |

选型关键参数:

- 击穿电压(VBR) > 工作电压

- 箝位电压(VC) < 被保护器件耐压

- 结电容(Cj)不影响信号带宽(如USB 2.0需Cj < 3pF)

3. 电路拓扑设计

- 单线保护:TVS对地并联(信号线→TVS→GND)。

- 差分线保护:

- 使用双向TVS箝位线间电压(如USB D+/D-之间加TVS)。

- 或选用集成ESD保护阵列(如TPD4E001)。

- 电源线保护:

- TVS并联在VCC与GND之间,搭配LC滤波器(抑制传导干扰)。

典型电路示例:

USB_D+ ──┬─────┤ TVS ├── GND

│ └─────┘

└─ 22Ω电阻 ── MCU_IO 4. PCB布局关键要点

- 最短泄放路径:TVS器件紧靠被保护接口(<5mm)。

- 独立接地:为ESD器件设置专用接地焊盘(避免共享走线)。

- 避免锐角走线:使用圆弧布线减少电场集中。

- 电源隔离:敏感电路与噪声源(如电机)分区域布局。

5. 分层与地平面设计

- 多层板结构:至少4层(信号-地-电源-信号)。

- 完整地平面:避免地平面分割,确保低阻抗回流路径。

- 地线缝合:不同地平面间通过过孔阵列连接(间距<λ/20)。

6. 系统级防护补充

- 金属外壳接地:机壳通过1MΩ电阻并联2kV高压电容接GND。

- 空气间隙设计:高压与低压线路间距 > 2.5mm(防爬电)。

- 导电泡棉/簧片:用于接口屏蔽罩接地。

三、仿真与测试验证

- SPICE仿真:

- 模拟ESD脉冲(如2ns上升时间)下保护器件的箝位效果。

- TDR测试:

- 检测TVS引入的阻抗不匹配(目标阻抗变化<10%)。

- 实际ESD测试:

- 按IEC 61000-4-2执行±4kV~±15kV放电测试,检查功能异常或复位。

四、常见错误与规避

-

错误:TVS距离接口过远(>10cm)

后果:ESD能量在PCB走线上感应出高压。

解决:TVS必须布局在接口连接器之后的第一位置。 -

错误:未隔离数字地与模拟地

后果:ESD噪声耦合到敏感ADC电路。

解决:单点接地(星型接地),或使用磁珠隔离。 -

错误:TVS选型电容过大(如10pF用于USB 3.0)

后果:信号边沿退化,通信失败。

解决:选用超低电容TVS(如SMAJ5.0A,Cj=50pF)或专用ESD抑制器。

五、高级优化技巧

- 组合保护:TVS + 气体放电管(GDT)用于工业设备(如RS485),分级泄放大电流。

- 自恢复保险丝:配合TVS防止ESD引起的持续短路(如PPTC+TVS)。

- 芯片内置保护:优先选用自带ESD防护的IC(如USB Hub芯片 ESD tolerance >8kV)。

总结:ESD保护设计需系统化思维——从器件选型、电路拓扑、PCB布局到测试验证全流程把控。掌握“快速泄放、低箝位电压、最小信号干扰”三要素,并结合具体应用场景优化方案,才能通过严苛的ESD测试。

ESD保护电路POWERclamp原理

ESD(Electrostatic Discharge,静电放电)保护电路是电子设备中非常重要的组成部分,它能够保护电子设备免受静电放电的损害。POWERclamp是一种常见的ESD保护电路,它通过

2024-09-14 14:41:17

在I/O电路中ESD保护结构的设计要求

ESD(静电放电)是CMOS电路中最为严重的失效机理之一,严重的会造成电路自我烧毁。论述了CMOS集成电路ESD保护的必要性,研究了在CMOS电路中ESD保护结构的设计原理,分析了该结构对版图的相关要求,重点讨论了在I/O电路中ESD保护结构的设计要求。

![]() chm6

2021-04-02 06:35:57

chm6

2021-04-02 06:35:57

基于CMOS电路的ESD保护设计

ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不但要能吸收ESD电流,还要能箝位工作电路的电压,防止工作电路由于电压过载而受损。

2019-03-04 14:24:01

如何设计ESD保护电路?

,提高了芯片的运算速度。 但是,随着工艺的进步和尺寸的减小,静电释放(ESD),Elecyro Static Discharge)问题变得日益严峻。据统计,在集成电路设计中大约40%的失效电路是ESD问题造成的。如何设计ESD保护电路?这个问题急需解决。

![]() whc94115

2019-08-07 06:24:17

whc94115

2019-08-07 06:24:17

采用HDMI接口实现ESD保护

情况严重。考虑上述原因,生产商强烈建议为外部端口增加额外的ESD保护电路。 目前,恩智浦半导体(NXP Semiconductor)开发了多种DVI/HDMI接口IC芯片,不仅确实能够提供出色的ESD

![]() 小蜜蜂12346

2019-06-17 05:00:06

小蜜蜂12346

2019-06-17 05:00:06

CMOS电路的ESD保护结构设计

ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不但要能吸收ESD电流,还要能箝位工作电路的电压,防止工作电路由于电压过载而受损。

2019-04-08 15:26:11

ESD保护元件介绍

`ESD器件概述ESD保护元件的作用是转移来自敏感元件的ESD应力,使电流流过保护元件而非敏感元件,同时维持敏感元件上的低电压;ESD保护元件还应具有低泄漏和低电容特性,不会降低电路功能;不会对高速

![]() dodo1999

2020-03-19 11:32:36

dodo1999

2020-03-19 11:32:36

PCB板“ESD保护电路设计”实战经验分享!!!

ESD设计。在设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。通过调整PCB布局布线,能够很好地防范ESD。以下是一些常见的防范措施。几种典型的通用ESD保护电路分享个人的ESD保护9大措施

![]() ElecFans小喇叭

2019-06-28 08:00:00

ElecFans小喇叭

2019-06-28 08:00:00

电容触摸屏的ESD保护电路

电容触摸屏的ESD保护电路ESD TVS能够提高电容触摸屏的抗干扰能力,有效防止因为系统电源和使用环境等干扰信号导致的电容触摸屏死机,重启,跳点误触发等问题;提高电容触摸屏的ESD能力,防止因为触

![]() dodo1999

2021-12-13 15:50:37

dodo1999

2021-12-13 15:50:37

ESD保护电路设计法则

造成栅氧击穿,所以他不见的是一种很好的ESD设计方案,而且有源区越小则栅压的影响越大,而有源区越大则snap-back越难开启,所以很难把握。4、还有一种复杂的ESD保护电路:可控硅晶闸管(SCR

![]() lin364884292

2021-12-04 07:00:00

lin364884292

2021-12-04 07:00:00

NFC天线的ESD保护组件

将NFC与移动电话整合在一起,提供消费者以近距离感测方式进行有价交易,是现在广为讨论与实现的功能。但在大家热中于讨论与实现NFC的各种整合与实现方式时,有一项不可被忽视的影响是静电放电(ESD

![]() mmvjsuds2

2019-06-13 08:18:01

mmvjsuds2

2019-06-13 08:18:01

esd保护电路为什么加正向的二极管 esd保护是防止什么对电路板的损坏

ESD(Electrostatic Discharge,静电放电)保护电路中加入正向二极管的原因,主要是基于二极管的电气特性和其在电路中的保护作用。以下是对ESD保护电路加入正向二极管的原因以及

2024-10-06 10:58:00

ESD341 TVS ESD保护二极管技术解析与应用指南

Texas Instruments ESD341 TVS ESD保护二极管是用于HDMI 1.4电路保护的TVS ESD保护二极管。ESD341的额定ESD冲击消散值为IEC61000-4-2

2025-09-11 14:42:54

PT0504N-F10是一款ESD保护器件,用于保护电路免受静电放电(ESD)的影响民信微

2023-11-17 20:44:32

数据通信端口ESD静电保护电路如何设计

难度特别大。理解器件如何提供高于1GB/s的串行数据速率和完整的通信协议保护可以避免这个问题。硕凯电子专注电路保护领域,对静电放电保护有着丰富经验,更多ESD静电保护器件及电路设计,请直接进入硕凯电子网站咨询在线客服。

![]() SHUOKAIDIANZI

2019-07-19 17:40:22

SHUOKAIDIANZI

2019-07-19 17:40:22

ESD的3种模型和RF PA ESD保护方案介绍

芯朴科技所有5G n77 n77/79 PAMiF LFEM 天线口内置IEC ESD保护电路设计,无需外加额外ESD保护电路情况下,都通过 IEC ESD 8kV 测试标准,保障抗ESD可靠性,在产线组装和大批量出货后确保无IEC ESD损坏。

2024-04-24 10:12:12

HFTA-16.0:双极型集成电路的ESD保护

静电放电(ESD)会对集成电路(IC)造成破坏性的能量冲击,良好的IC设计能够在IC装配到应用电路的过程中保护IC免遭ESD冲击的破坏。安装后,IC还必须能够承受ESD穿过静电防护电路进入最终电路

2023-06-10 15:40:58

ESD器件的工作原理?CMOS I/O上的内部ESD保护实现

静电保护器件(ESD) 是由一个或多个 TVS 晶粒采用不同的电路拓扑制成具有特定功能的多路或单路 ESD 保护器件。

2024-02-17 16:01:00

在静电保护电路设计中的ESD器件选型

电子设备需要使用外部保护器件,除了因为:产品的功能集成化造成I/O接口的增多,为ESD进入电路及电压敏感型元件提供了有效路径;产品外观小型化,使得IC更容易受到ESD损坏;满足ESD抑制标准

2021-12-14 05:17:19

ESD静电保护管的工作原理

ESD静电保护管是一种常用性的过压、静电保护元件,保护电子设备中敏感电路免遭静电影响。ESD静电保护管并联于电路中,当电路正常运作时,ESD静电保护管处于高阻态,不影响线路正常工作;当电路出现异常过

2022-09-22 17:36:59

常用的ESD保护器件及原理

Resistor不单独用于芯片的ESD保护,它往往用于辅助的ESD保护,如芯片Input第一级保护和第二级保护之间的限流电阻。如图5,当ESD电流过大,第一级ESD器件难以将电压钳位至安全区域时,第二级ESD器件的导通将使其与电阻分压,从而进一步降低进入内部电路的电压。

2023-12-07 09:15:04

ESD保护电路的计算方法及注意事项

为了能更加清晰透彻的掌握ESD保护电路的设计,今天就用实际的例子进行一遍电路的计算选型,假定C ESD = 330pF,V ESD = 8kV,我们的任务是计算需要安装在IC引脚边上的陶瓷电容器的容

2022-04-26 13:57:21

HDMI接口的ESD保护方案

较低电位上,该较低电位指的是ESD保护芯片的钳位电压VC(Clamping Voltage),它将由不同的ESD保护芯片型号而限定其不同。

2024-12-29 13:56:10

一种常见的ESD静电保护器件

具有特定功能的单路或多路ESD保护器件。ESD静电保护二极管响应速度快(小于0.5ns)、低电容、低导通电压、高集成度、小体积、易安装,可以同时实现多条数据线保护,是业内较理想的高频数据保护

![]() langtuodianzi

2021-03-11 13:00:12

langtuodianzi

2021-03-11 13:00:12

SIM卡模块的SIM卡接口的ESD静电和闭锁保护 TVS 管 SMF05C

ESD的产生来实现保护;二是通过使用保护边路来实现,如使用ESD保护器件等来实现电路保护。以下就以SIM800/900模块为例,就模块设计中SIM卡接口、RF射频接口、电源管理这三部分来分析相关的ESD

![]() dodo1999

2021-02-01 11:21:33

dodo1999

2021-02-01 11:21:33

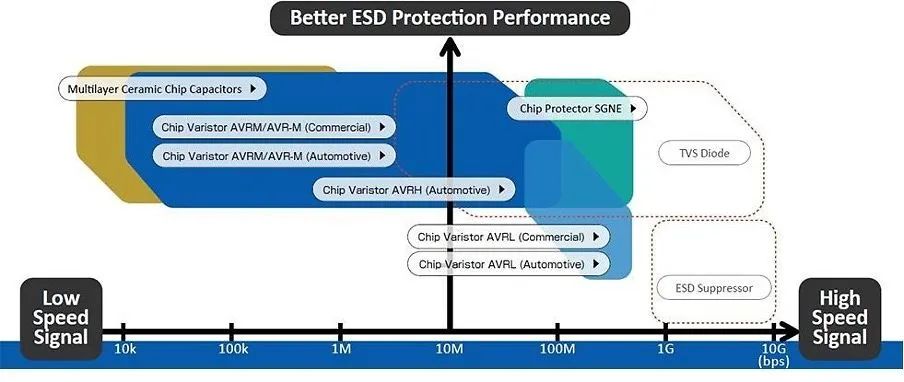

TDK | 如何选择ESD保护元件?

随着信号传输速度的提高和供电电压的降低,集成电路对瞬态ESD更加敏感。电路中连接的设备也日益增多,因此保护更广泛系统中每个设备免受ESD的影响就变得更加重要。那么,为ESD保护选择正确的元件时需要考虑哪些因素?

2024-02-22 14:16:24