ad9852与ad9854区别

AD9852内置的只有一个DAC,AD9854的内置两个DAC。AD9854支持完全正交的两个输出,而AD9852仅有一个输出,另一个DAC仅为控制用DAC,但AD9854的引脚与ad9852的单频信号发生器模式相兼容。

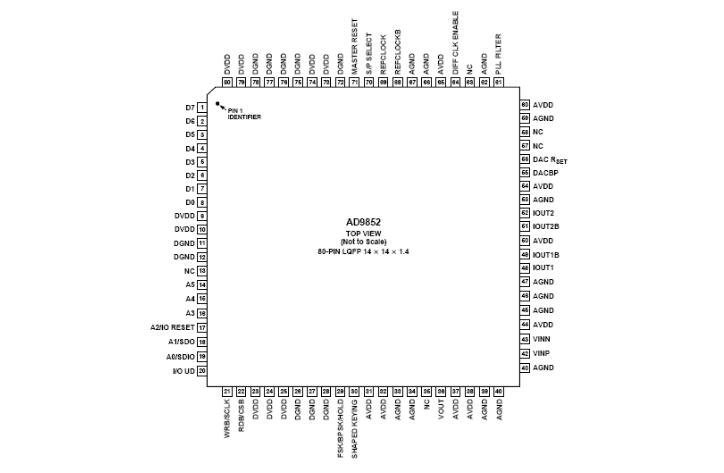

ad9852引脚图及功能

AD9852的引脚说明:D7—D0:Pin1—8,并行编程模式下的8位并行数据I/O口。

A0—A5:Pin14—19,并行编程模式下的6位并行地址口。其中,Pin17与串行通信的复位端复用,Pin18与串行数据输出口复用(3线模式),Pin19与串行数据I/O口复用((2线模式)。

DVDD:Pin9,10,23,24,25,73,74,79,80,数字电路电源端,相对于数字地3.3V供电,3.135V—3.465V可保证设计指标。

DGND:Pinll,12,26,27,28,72,75,76,77,78,数字地。

AVDD:Pin31,32,37,38,44,50,54,60,65,模拟电路电源端,相对于模拟地3.3V供电,3.135V—3.465V可保证设计指标。电路设计时,应加强DVDD和AVDD之间的去藕,以防噪声相互串扰。

AGND:Pin33,34,39,40,41,45,46,47,53,59,62,66,67,模拟地。

NC:Pin13,35,57,58,63,内部无连接的引脚,布线时可以悬空。

I/OUD:Pin20,频率更新端口。要向AD9852寄存器内写数据,先是写到端口的缓冲器里,等工作模式所需的数据写完后,再在此引脚上加一持续至少8个系统时钟周期的高电平,使DDS芯片按照所设置的方式运行。频率更新也可以设置成内部更新模式,这时DDS按照UDC寄存器设置的值定时自动更新频率,同时输出持续8个系统时钟周期高电平的同步信号。

WRB/SCLK:Pin21,并行模式下的写控制端,与串行模式时钟信号输入端复用。

RDB/CSB:Pin22,并行模式下的读控制端,与串行模式片选端复用。FSK/BPSK/HOLD:Pin29,多功能复用引脚。FSK工作模式下,低电平选择频率F1,高电平选F2;BPSK模式时,低电平选相位1,高电平选相位2;Chirp模式时,高电平使DDS输出保持当前频率。

SHAPEDKEYING:Pin30,高电平使DDS输出有一个调幅过程,若电路设计为低电平,DDS将没有输出。

VOUT:Pin36,高速比较器输出端。

VINP:Pin42,比较器正电压输入端。

VINN:Pin43,比较器负电压输入端。

IOUTl:Pin48,余弦DAC单极电流输出端。

IOUTIB:Pin49,余弦DAC单极电流互补输出端。

IOUT2B:Pins51,控制DAC单极电流互补输出端。

IOUT2:Pin52,控制DAC单极电流输出端。

DACBP:Pin55,DAC旁路电容连接端。从该端口串接一0.01uF电容到AVDD可以改变SFDR性能。

DACRSET:Pin56,DAC满幅输出设置:RsET=39.9/IouT。

PLLFILTER:Pin61,串接1.3k。电阻和0.01uF到AVDD(Pin60),构成参考源倍频PLL环路滤波器的零补偿网络。

DIFFCLK:Pin64,差分时钟使能端,高电平有效。AD9852的时钟输入有两种方式:单端正弦输入和差分输入,具体采用哪一种方式,通过它来选择。REFCLKB:Pin68,差分时钟的互补输入端。

REFCLK:Pin69,单端时钟信号输入或差分时钟的另一输入端。

S/PSELECT:Pin70,编程模式选择端。逻辑高选择并行模式。

MASTERRESET:Pin71AD9852的复位端,持续10个系统时钟周期的高电

AD9852的主要性能参数

·300MHz内部时钟上限;

·集成化12位D/A输出;

·良好的动态性能:在100MHz输出时仍具有80dBSFDR;

·内含4~20倍可编程参考时钟倍乘器;

·双向48位可编程频率寄存器和双向14位可编程相位寄存器;

·12位振幅调谐和可编程ShapedOn/OfKe2

ying功能;

·单脚FSK和PSK数据接口;

·HOLD引脚具有线性或非线性调频功能;

·可自动双向频率扫描;

·可进行sin(x)/x校正;

·简化的控制接口:10MHz串行两线或三线外围接口;100MHz8位并行程序设计接口;

·用3.3V单电源供电;

·单端或差分参考时钟输入。

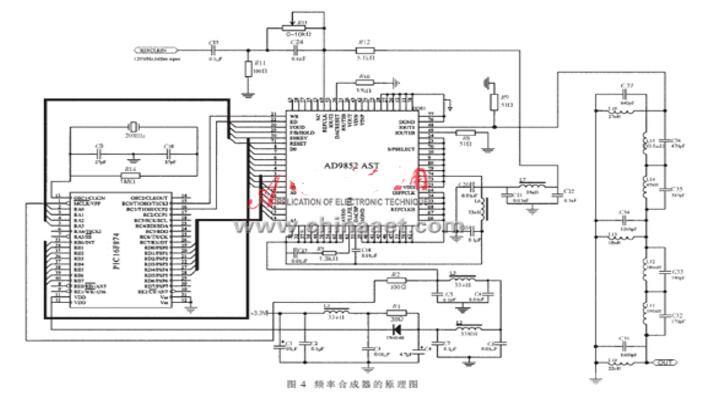

ad9852应用电路

由于采用了参考信号单端输入的方式,所以REFCLKB端应该接地或电源;参考信号输入端REFCLK要跟电源相连接。因为DDS的参考信号要求有1.6V的直流电平,在参考信号输入到REFCLK端的端点处,应接一个5.1kΩ的电阻到3.3V直流电源,同时接一个0~10kΩ的可变电阻(此处取5kΩ)到100Ω的电阻,经过电阻分压,REFCLK端就有1.6V的直流电压。这个0~10kΩ的可调电阻同时用来微调REFCLK端对地的电阻,以调节REFCLK的直流电位,具体情况请参看图4。图4中的∏形滤波部分是为了滤除电源对REFCLK端的干扰。该频率合成器原理图如图4所示。

检验证明,利用AD9852设计的频率合成器具有跳频速度快、频率分辨率高、体积小、系统工作稳定、使用方便等优点。因此它有很强的实用价值。

DDS除了用于跳频系统中外,还可以用于任意波形产生、信号调制等。随着高速集成电路的飞速发展,DDS必将开拓更多新的应用领域。

AD9854的特征

·300M内部时钟频率

·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作

·正交的双通道12位D/A转换器

·超高速比较器,3皮秒有效抖动偏差

·外部动态特性:

80dB无杂散动态范围(SFDR)@100MHz(±1MHz)AOUT

·4倍到20倍可编程基准时钟乘法器

·两个48位可编程频率寄存器

·两个14位可编程相位补偿寄存器

·12位振幅调制和可编程的通断整形键控功能

·单引脚FSK和BPSK数据输入接口

·PSK功能可由I/O接口实现

·具有线性和非线性的脉冲调频(FMCHIRP)功能,带有引脚可控暂停功能

·具有过渡FSK功能

·可自动进行双向频率扫描

·能够对信号进行sin(x)/x校正

·简易的控制接口:

可配置为10MHZ串行接口,2线或3线SPI兼容接口或100MHZ8位并行可编程接口

·3.3V单电源供电

·具有多路低功耗功能

·单输入或差分输入时钟

·小型80脚LQFP封装