资料介绍

描述

SP701是一款基于 Spartan-7 的 FPGA 开发板。Spartan-7 FPGA 是赛灵思产品线中最理想的 FPGA 之一,因为它的每瓦性能效率。使用 MicroBlaze 软处理器与 Zynq SoC 对应的物理实例化 ARM 内核相比,我个人发现功耗可以降低近 75%。

SP701 开发板非常方便,因为它的外围设备和可用 I/O 范围包括 2 个 RJ45 以太网连接器、USB 到 UART 桥接器、6 个 PMOD、一个 VITA 57.1 FMC LPC、HDMI、MIPI-CSI 和 MIPI-DSI,以及作为一些按钮和DIP开关。这是概念验证类型项目的理想起点。

我在这篇文章中创建的硬件设计在功能上等同于 Xilinx 网站上提供的 IPI 示例设计,但将提供有关如何布局设计的详细指南,因为它是为SP701设计的,因此希望它更清晰从哪里开始添加任何定制设计。

为 SP701 生成许可证文件

SP701(1G/2.5G 以太网控制器)所需的 IP 之一需要许可证才能生成比特流。购买 SP701 评估套件时包含此许可证,因此只需在主机 PC 上的 Vivado 中生成并安装数字许可证文件。

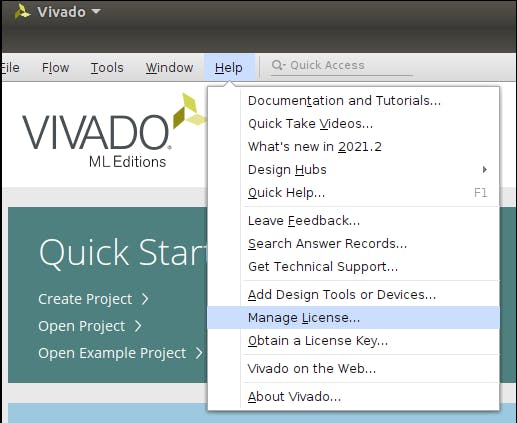

通过选择Help > Manage License...从 Vivado启动Xilinx License Manager

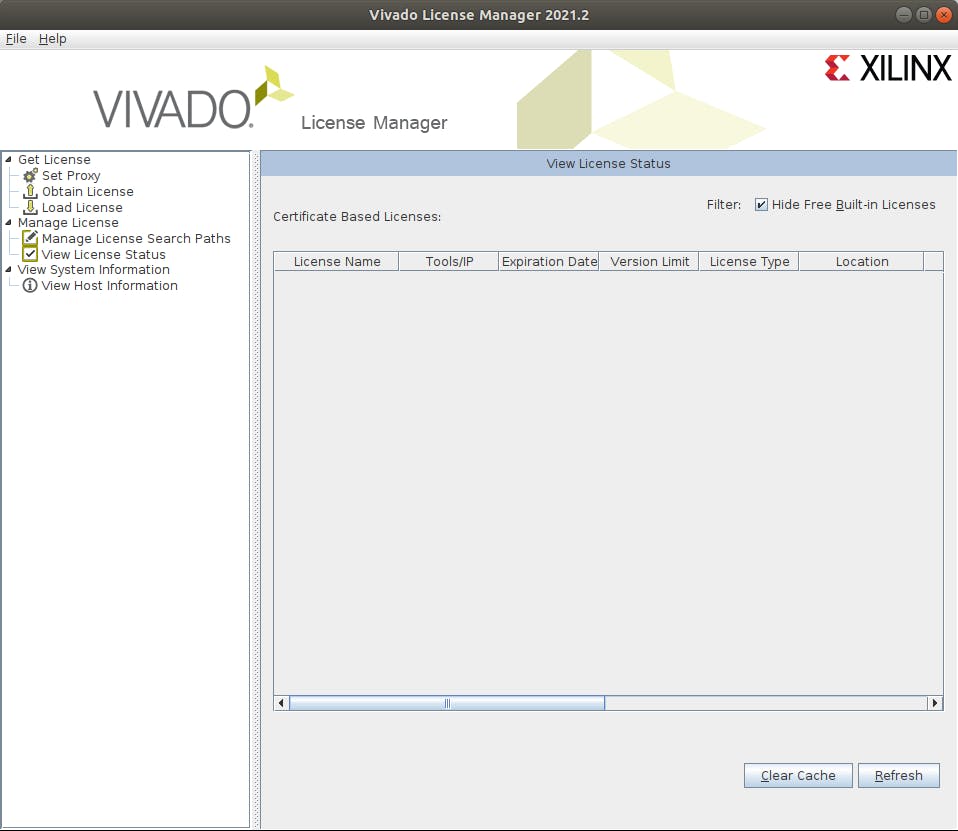

选择获取许可证选项卡并选中获取我的完整或购买的基于证书的许可证选项,然后单击立即连接,这将在您的浏览器中打开一个窗口,访问 Xilinx 的网站。

出现提示时登录 Xilinx 网站并提供所需信息(由于 FPGA 的某些敏感信息和美国的出口管制法律,需要提供此信息)。

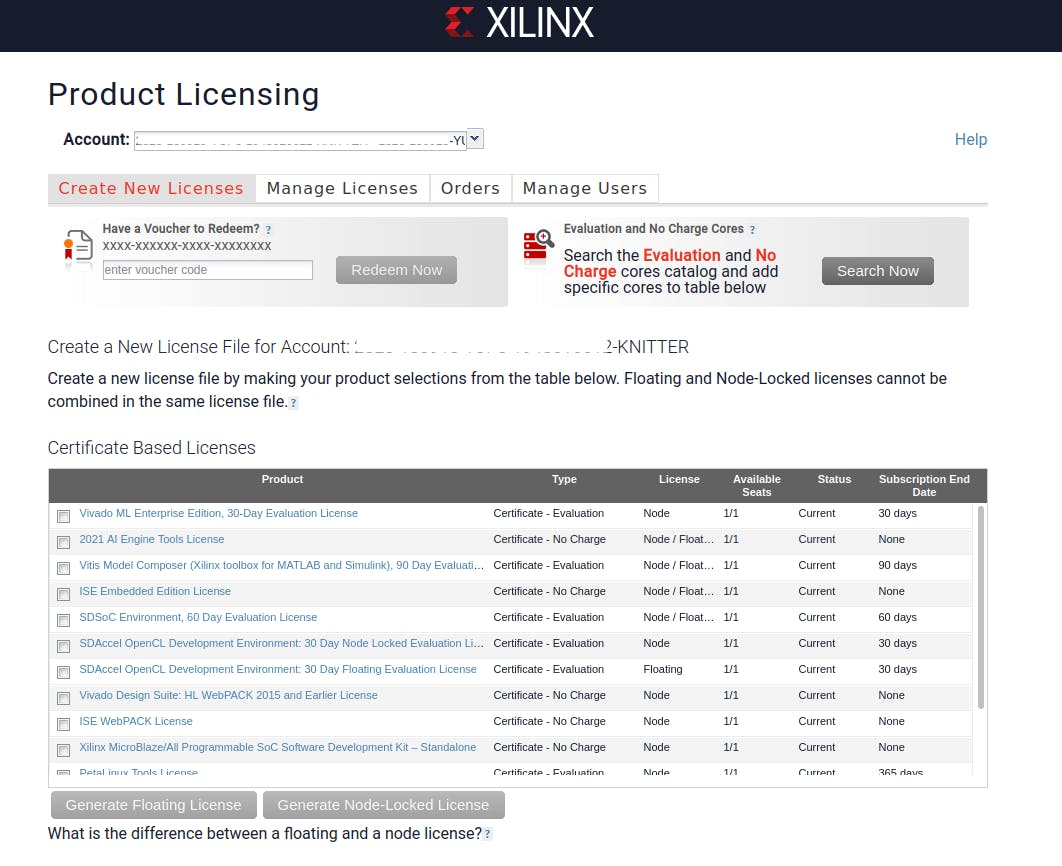

登录后,您会看到一个框,您可以在其中输入代码,在有要兑换的凭证?输入 SP701 包装盒中随附的快速入门指南背面的凭证编号(它将在条形码正上方以红色突出显示),然后单击立即兑换。

一个弹出窗口将确认凭证是用于 SP701 评估套件的,单击Yes 。

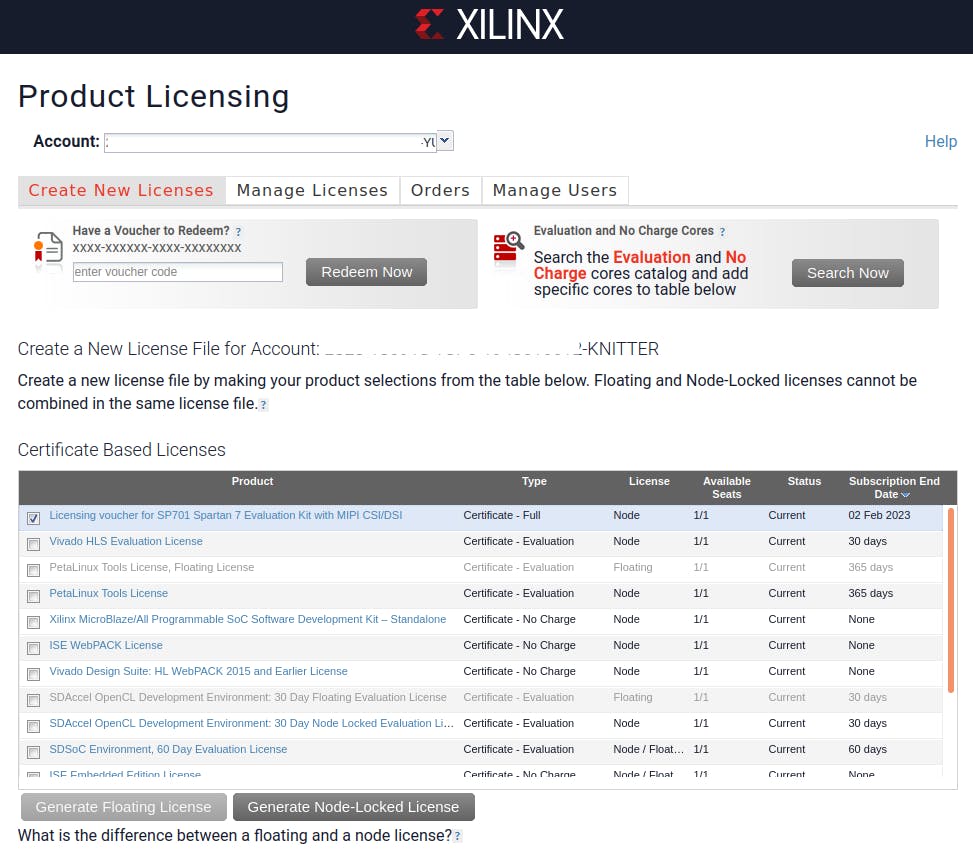

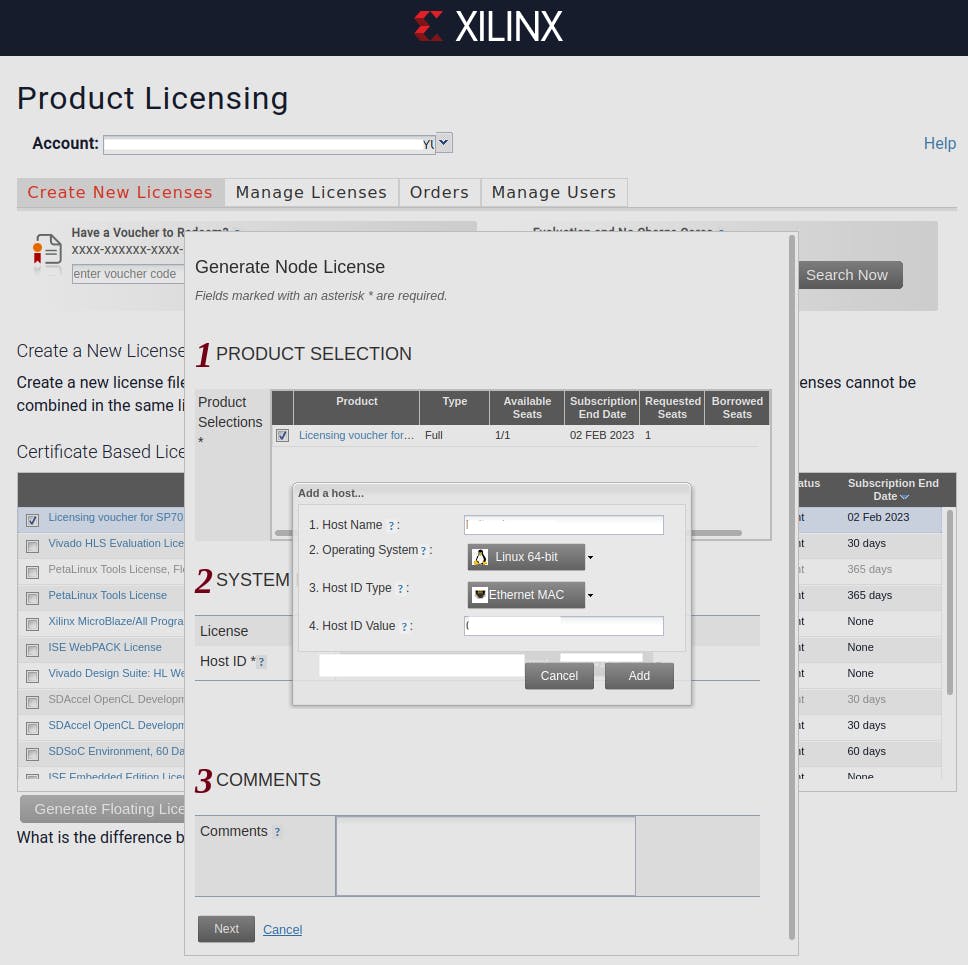

SP701 评估套件的基于证书的许可证表顶部将出现一个新行。选中旁边的框,然后单击生成节点锁定许可证(凭证仅适用于节点锁定许可证,因此不能选择浮动许可证)。

输入您的主机 PC 信息,您可以在Xilinx License Manager的查看主机信息下找到该信息。单击下一步。

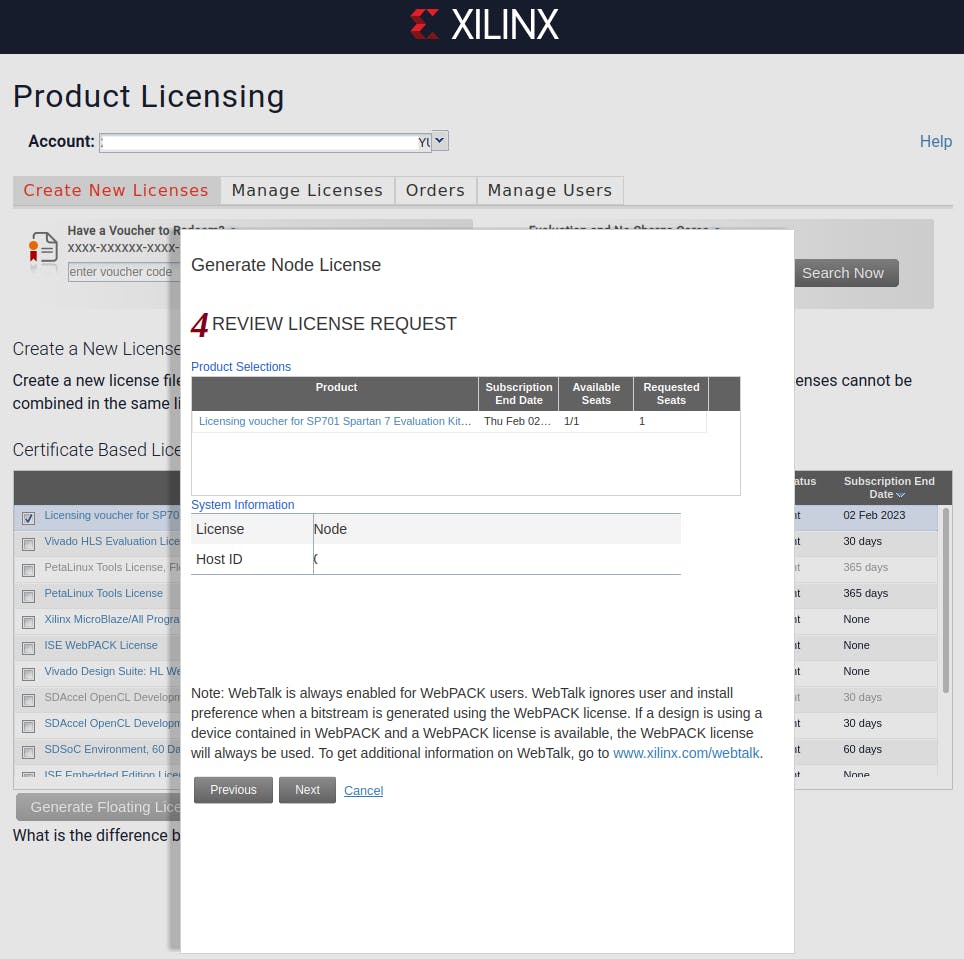

确认一切并再次单击下一步,然后您必须接受许可协议。

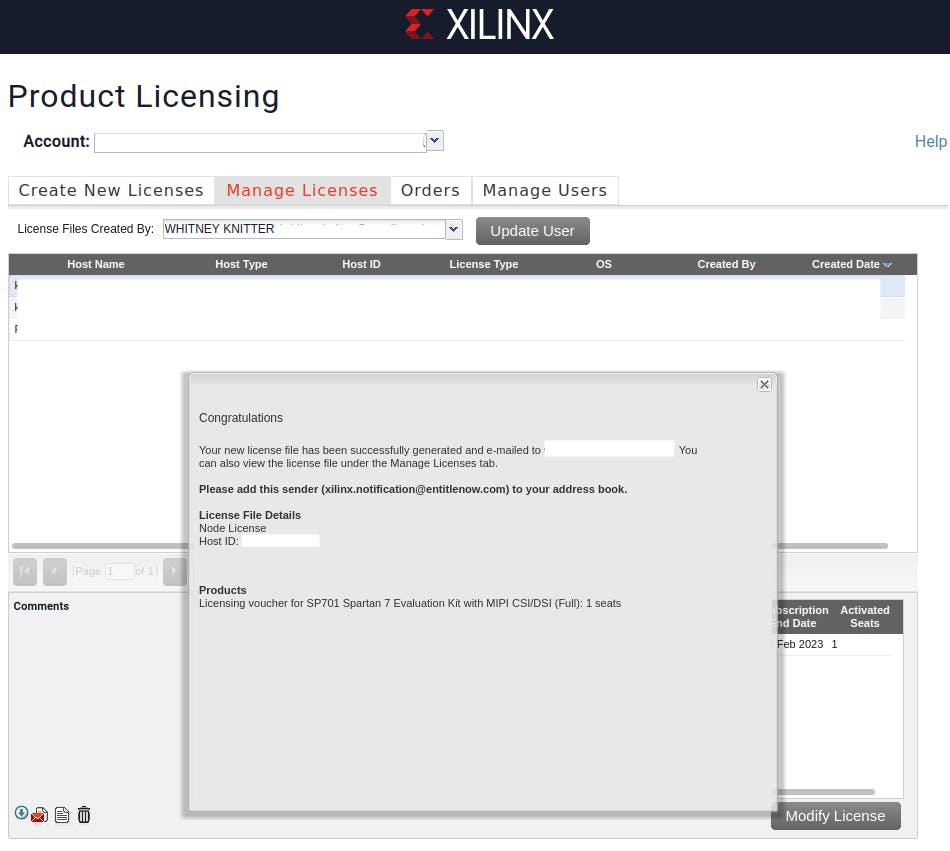

许可证文件将通过电子邮件发送给您,说明在 Windows 和 Linux 中放置它的位置。

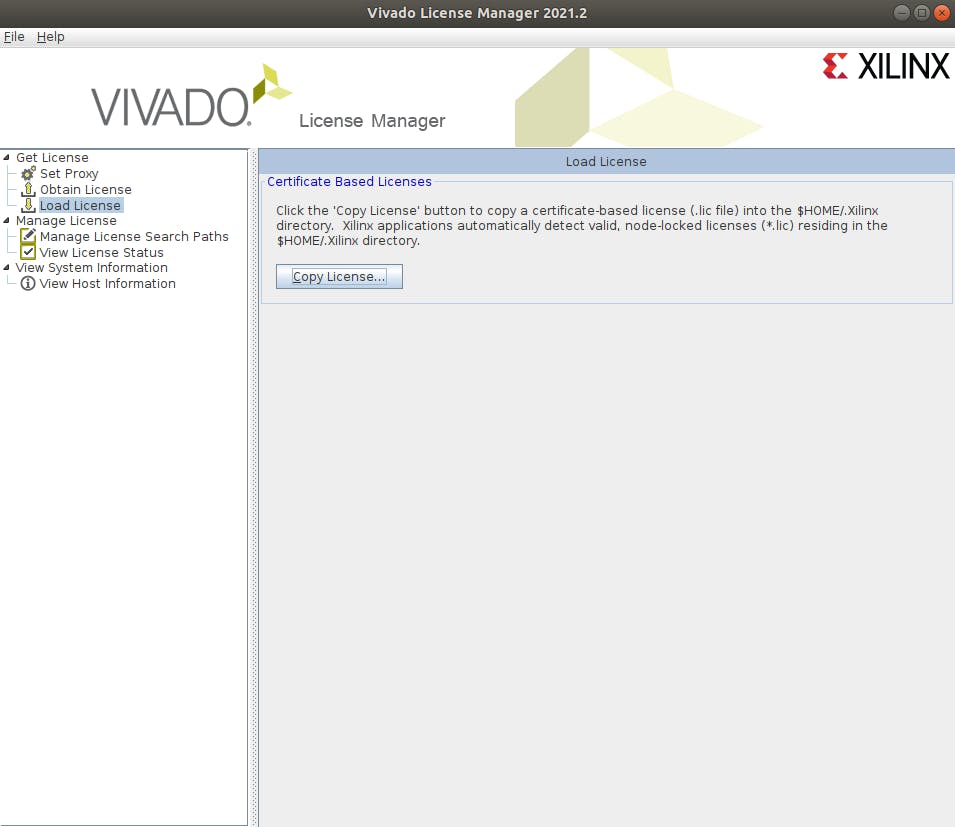

将电子邮件中收到的 Xilinx.lic 复制到 $HOME/.Xilinx,或者您可以返回Xilinx 许可证管理器并选择加载许可证,其中的复制许可证按钮将让您指向下载的 Xilinx.lic 文件所在的位置,它将复制为您将其复制到 $HOME/.Xilinx。

重新启动 Vivado,以便它可以检测并获取新的许可证文件。

注意:安装在同一主机上的所有版本的 Vivado 都会选择此许可证文件,因此不必担心为每个版本的 Vivado 单独安装相同的许可证。

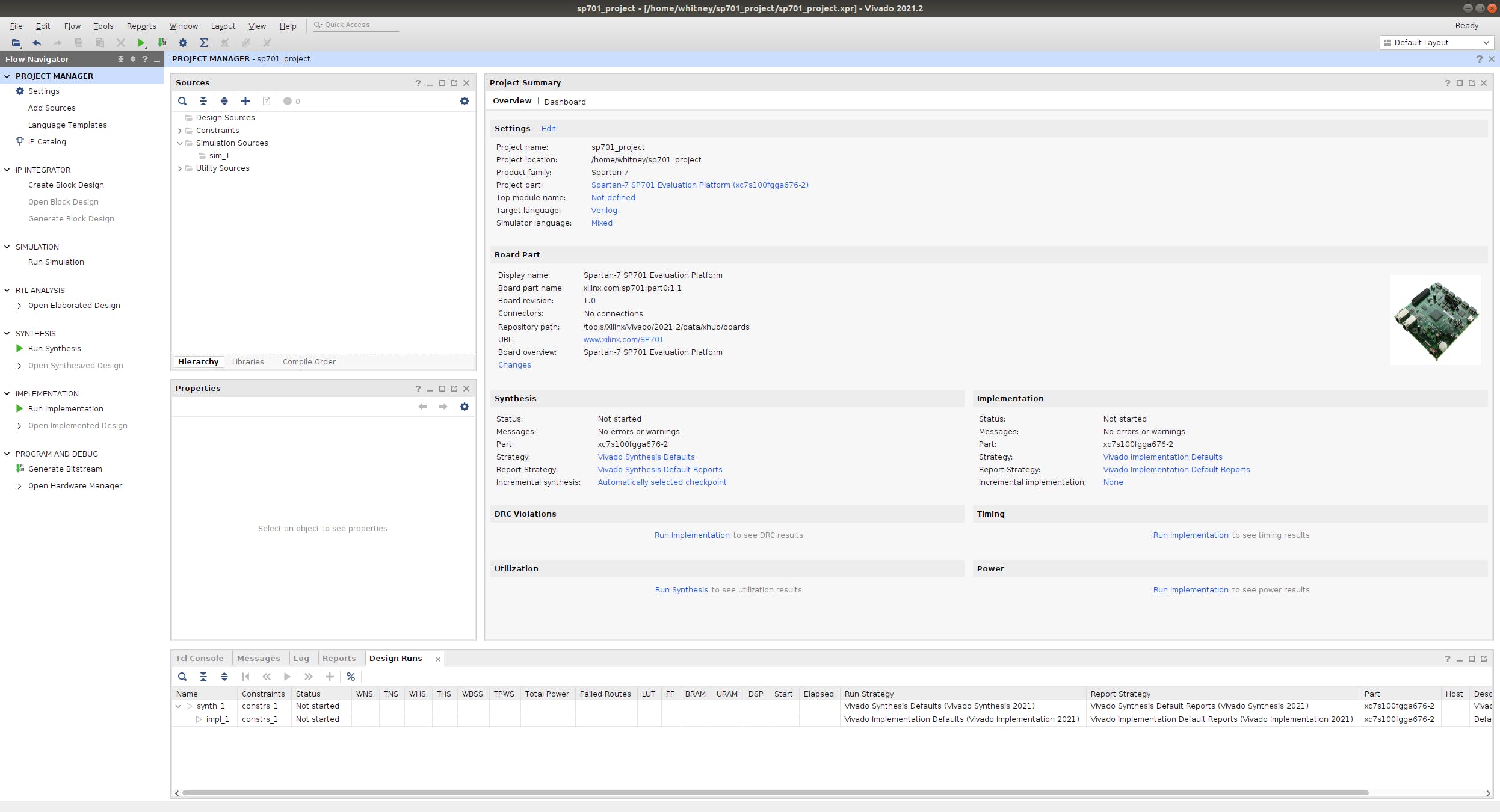

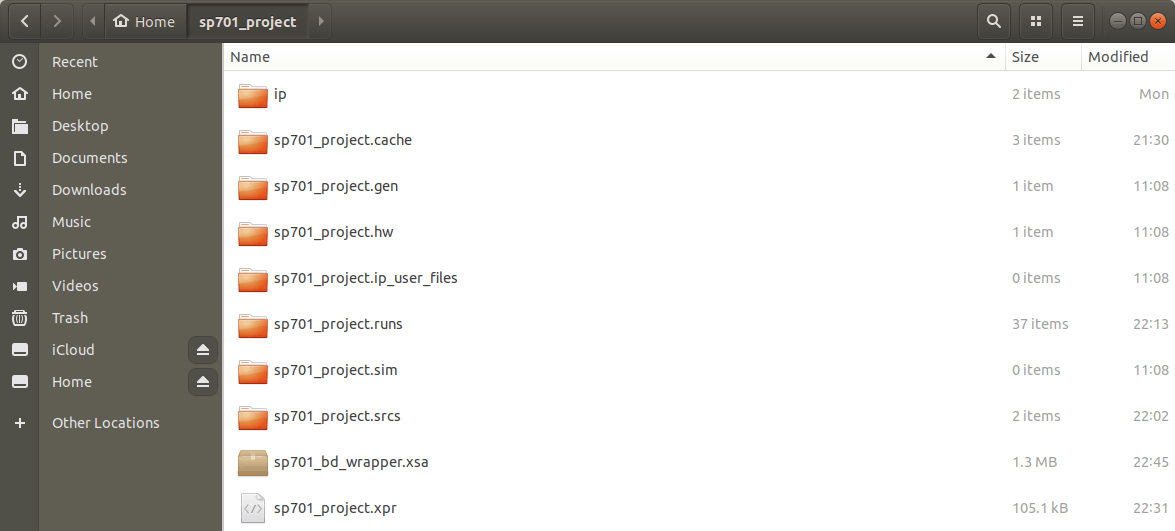

创建新的 Vivado 项目

从 Vivado 主窗口中选择Create Project ,然后逐步完成项目设置窗口。为项目命名并选择所需的项目目录。

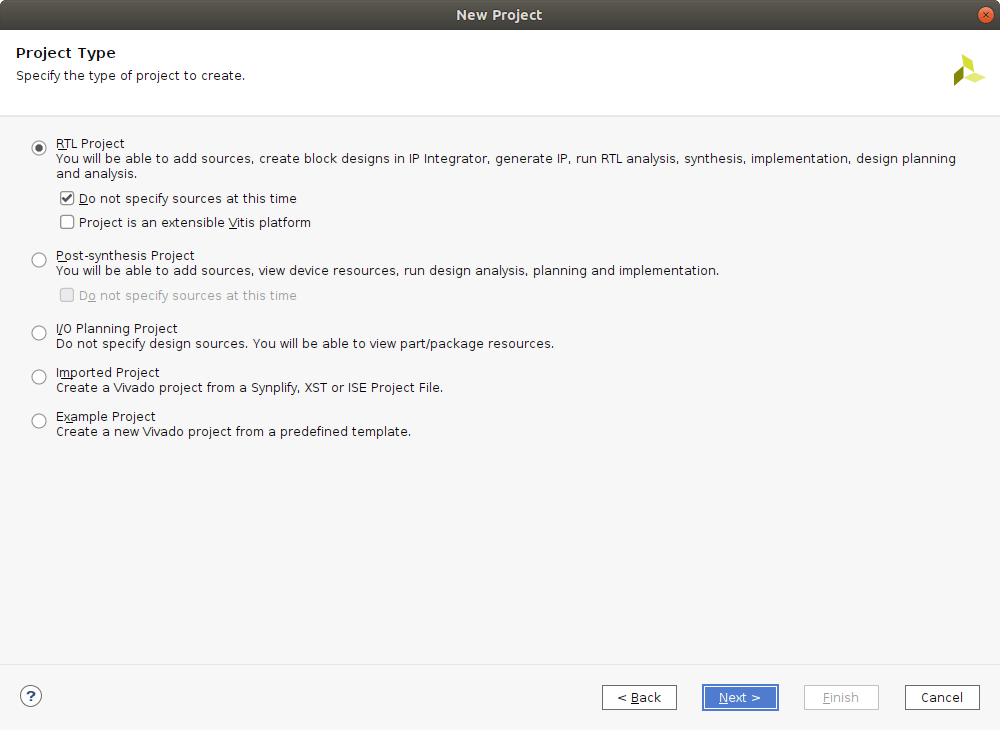

保留该选项以在此时不指定源,并且不要选择使项目成为 Vitis 可扩展平台的选项(这是不同日期的不同主题)。

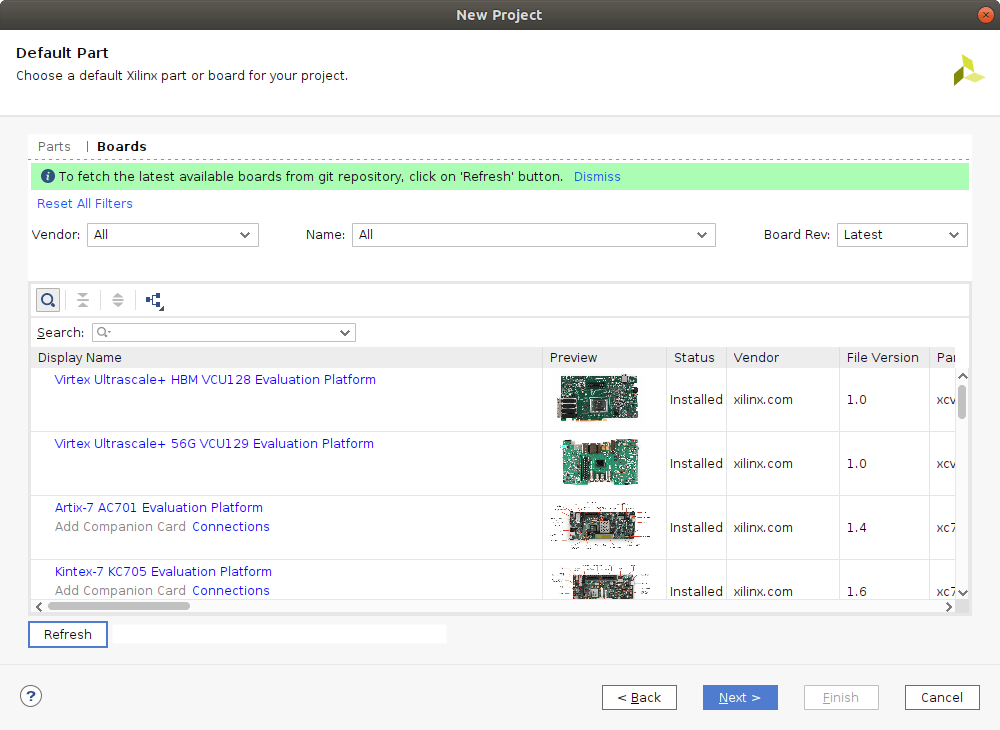

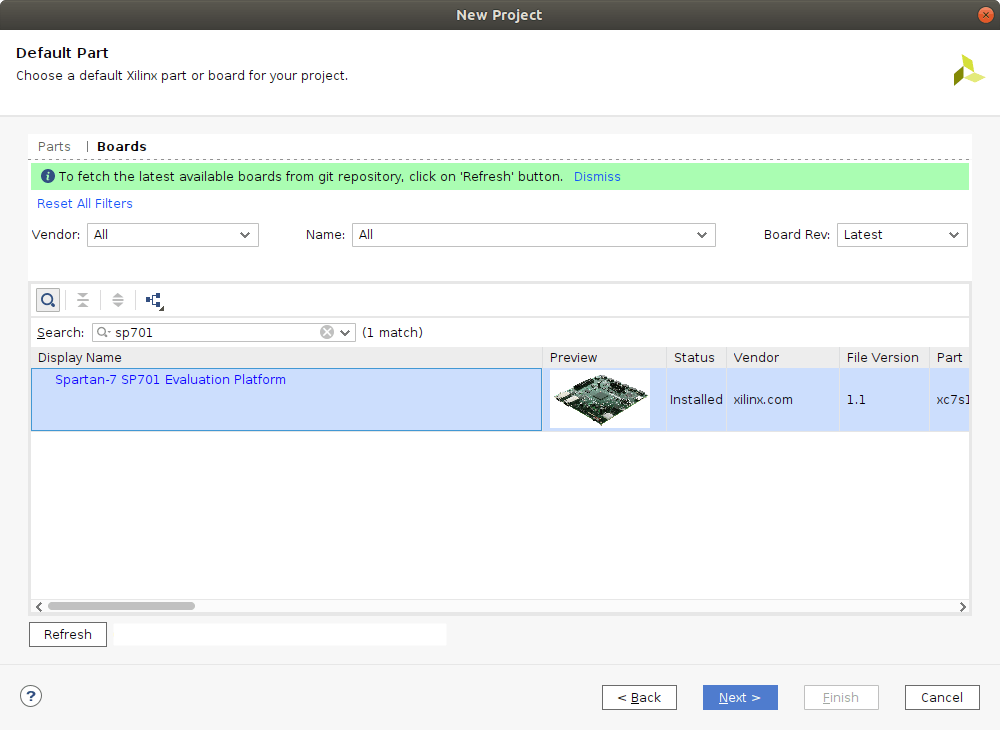

最后,必须选择目标FPGA芯片或开发板。Vivado 2021.2 不再需要手动安装大量板卡,不仅来自 Xilinx 自己的产品,还包括 Avnet、Digilent 和 Trenz Electronic。Vivado 2021.2 连接到 Xilinx Board Store,这是 Xilinx 维护的 Github 上的后端存储库。您最初需要互联网连接才能刷新并查看 Xilinx 电路板商店的当前版本,并下载所需电路板的预设。之后,您将能够离线使用它们。

搜索并选择 SP701 作为目标板,然后单击Next 。最后一页是要创建的 Vivado 项目的摘要。

单击完成以生成项目。

块设计

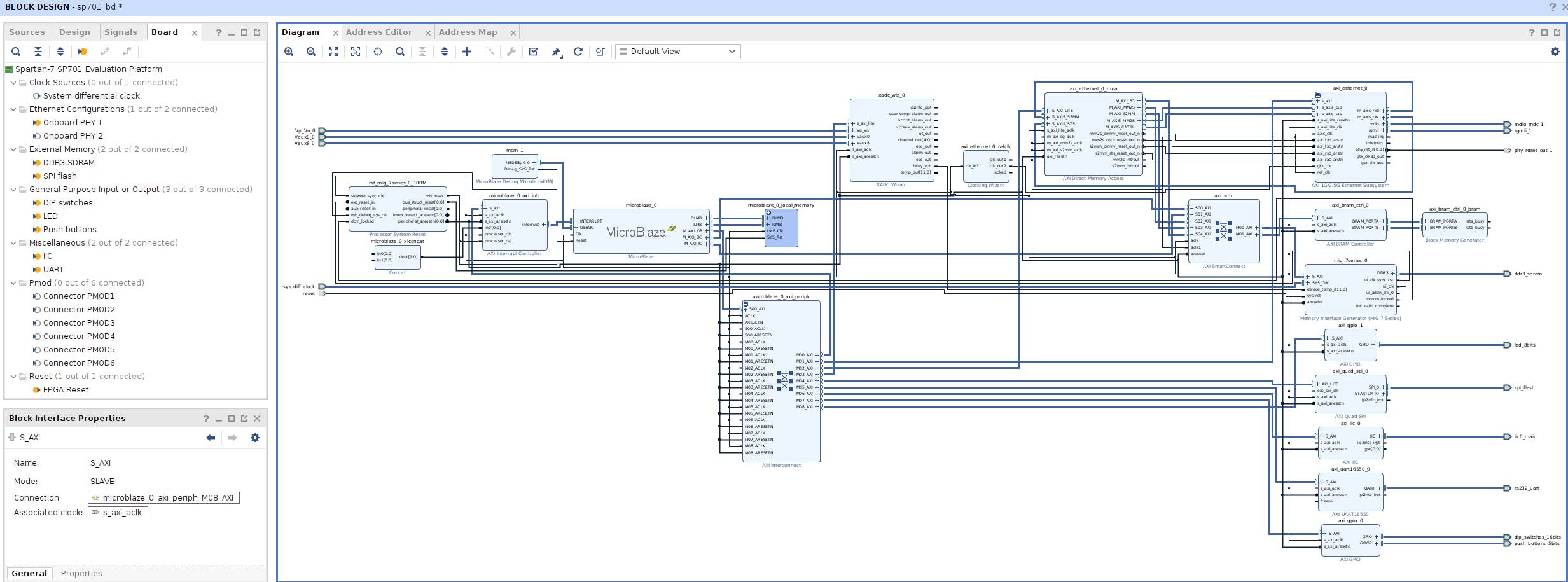

99% 的新 Vivado 项目将从创建块设计开始。块设计是一种将预先存在的 IP 块添加到设计中的直接方法,它带有用于自动设置配置和 IP 之间的接口连接的辅助工具。主要是,块设计是 FPGA 设计的处理器内核也通过其支持 IP 进行实例化的地方。由于 SP701 的 FPGA 是 Spartan-7,因此必须使用软处理器(与 Xilinx SoC 系列中的 Zynq 处理器相比,它是 FPGA 可编程逻辑中的物理实例化 ARM 内核)。因此,我将使用 Xilinx 的软处理器 MicroBlaze。

注意:我不会介绍如何将自定义 HDL 添加到 SP701 的这个特定项目中,它将在以后的帖子中。但是,我过去曾多次为其他董事会介绍过它。

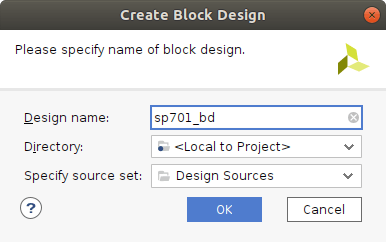

通过在Flow Navigator窗口中选择IP Integrator下的Create Block Design来创建一个新的模块设计。

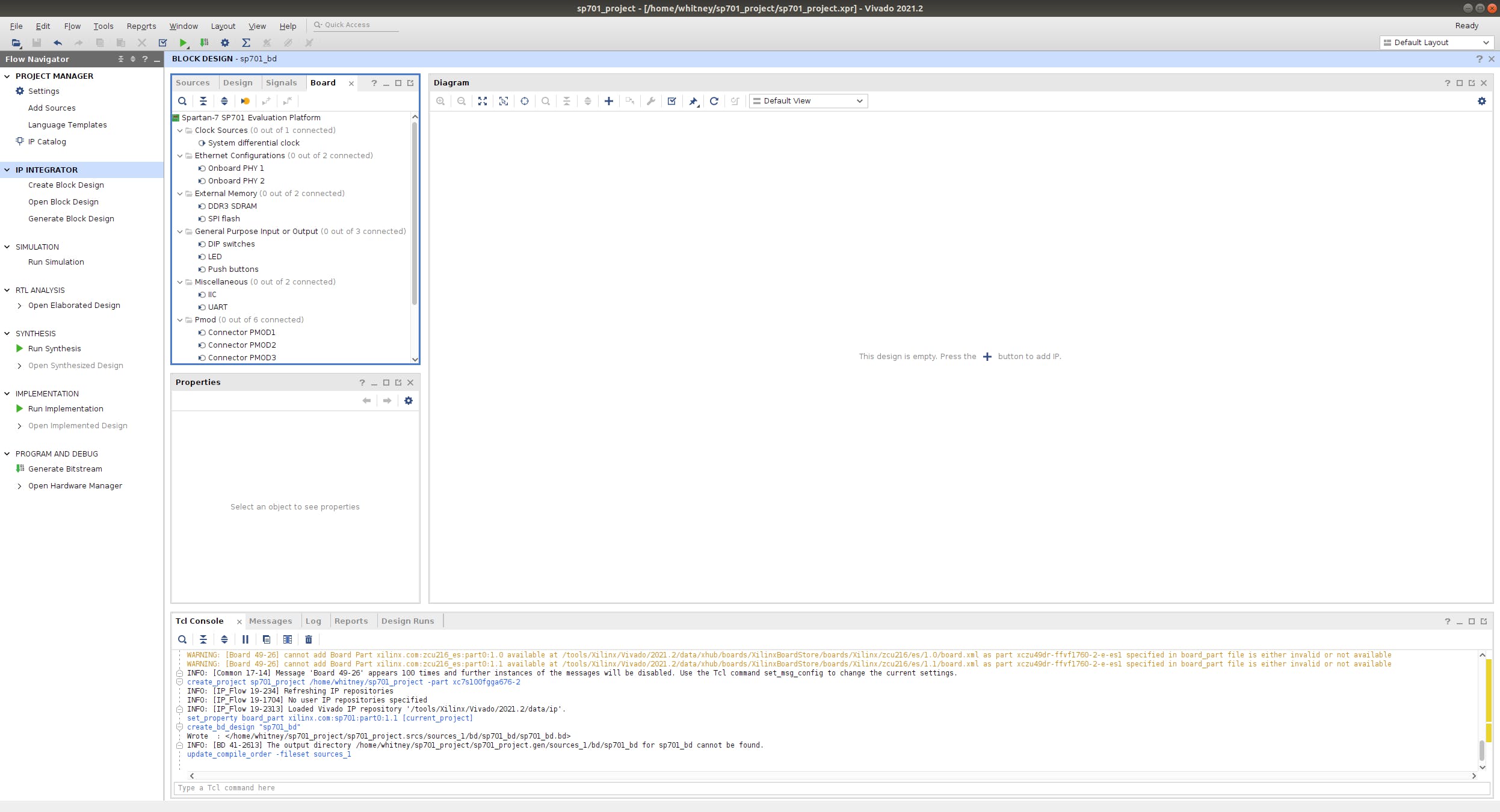

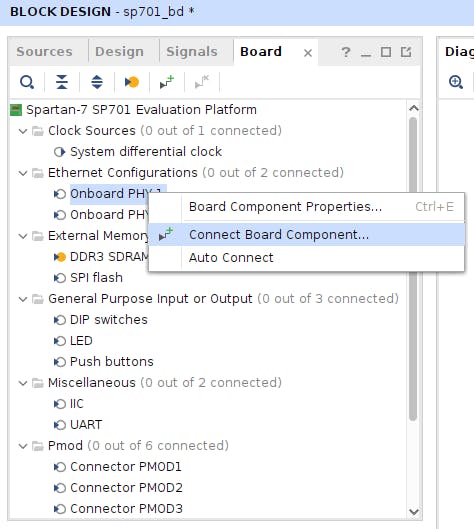

生成空白块设计后,您会注意到Board选项卡出现。从Sources选项卡切换到Board选项卡,您会看到 Vivado 已检测到 SP701 板上可用的外围接口。

此选项卡是选择特定板作为 Vivado 项目的目标而不是仅选择 FPGA 部件号本身的好处。它有助于加快设计过程,因为它会在您单击每个外围设备时过滤 IP 目录,以仅显示哪些 IP 块可以连接到选定的外围设备。

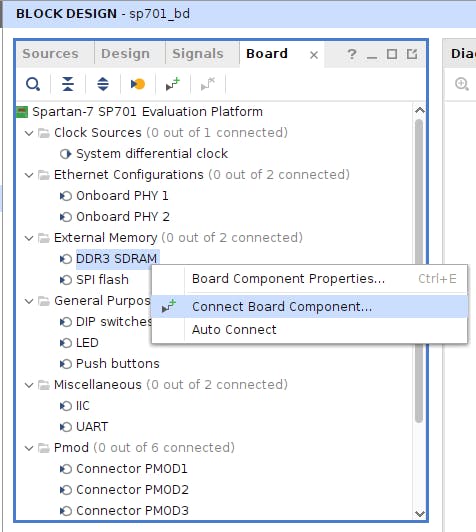

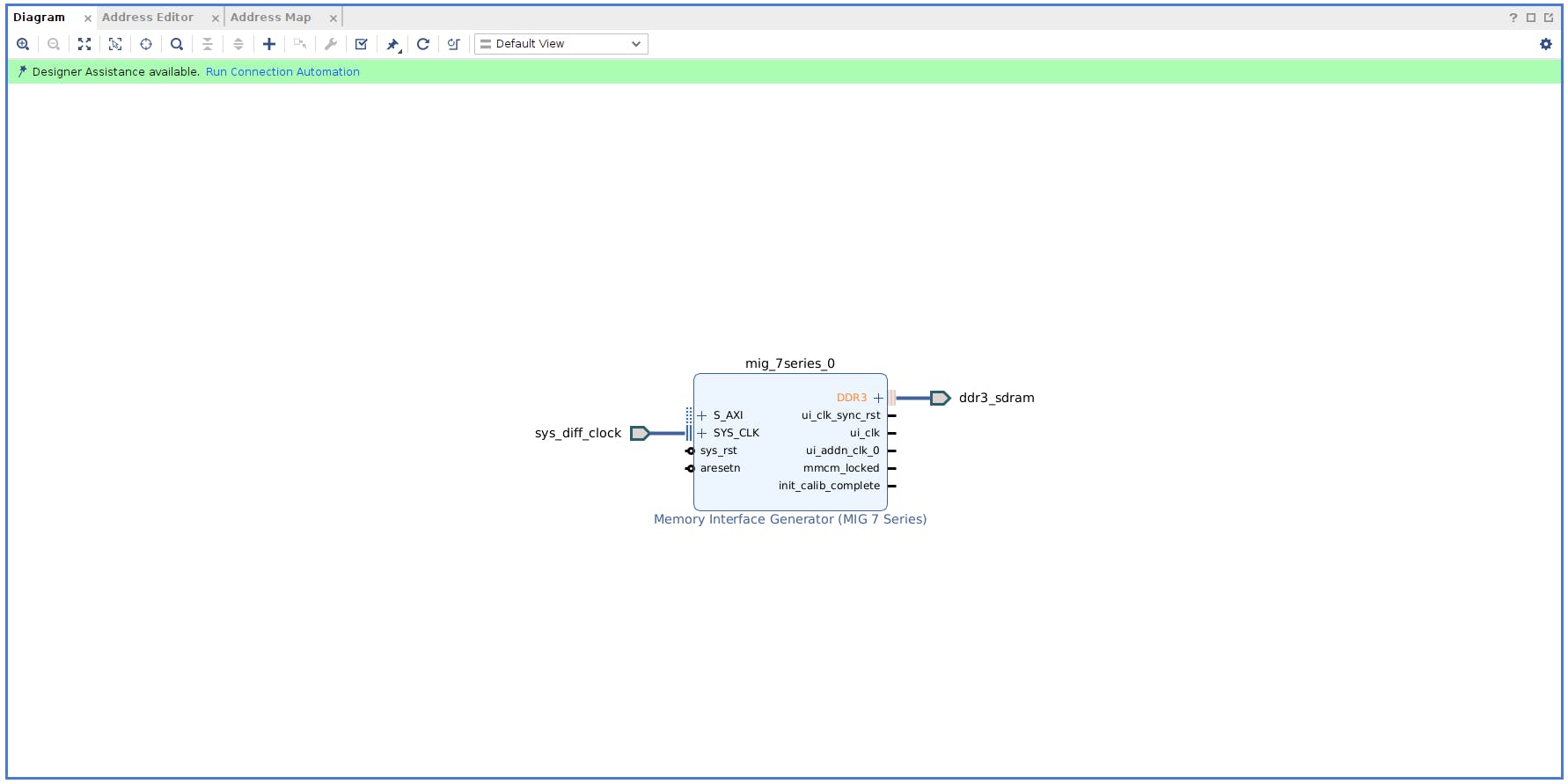

通常我首先在块设计中添加处理器 IP 块(在本例中为 MicroBlaze),但 SP701 有点不同。由于 DDR3 SRAM 的外部存储器控制器启动、运行和同步所需的时间最长,因此最好将其作为振荡器(系统时钟)馈送的第一件事,然后将其余 IP 置于下游. 所以我要添加到 SP701 块设计的第一件事将是内存接口生成器IP 块。

右键单击Board选项卡中的DDR3 SRAM并选择Connect Board Component ,然后从弹出窗口中选择选项mig_ddr_interface 。

跳过运行生成的连接自动化,该连接自动化在 Block Design 窗口顶部以绿色横幅弹出以连接 FPGA 复位信号。

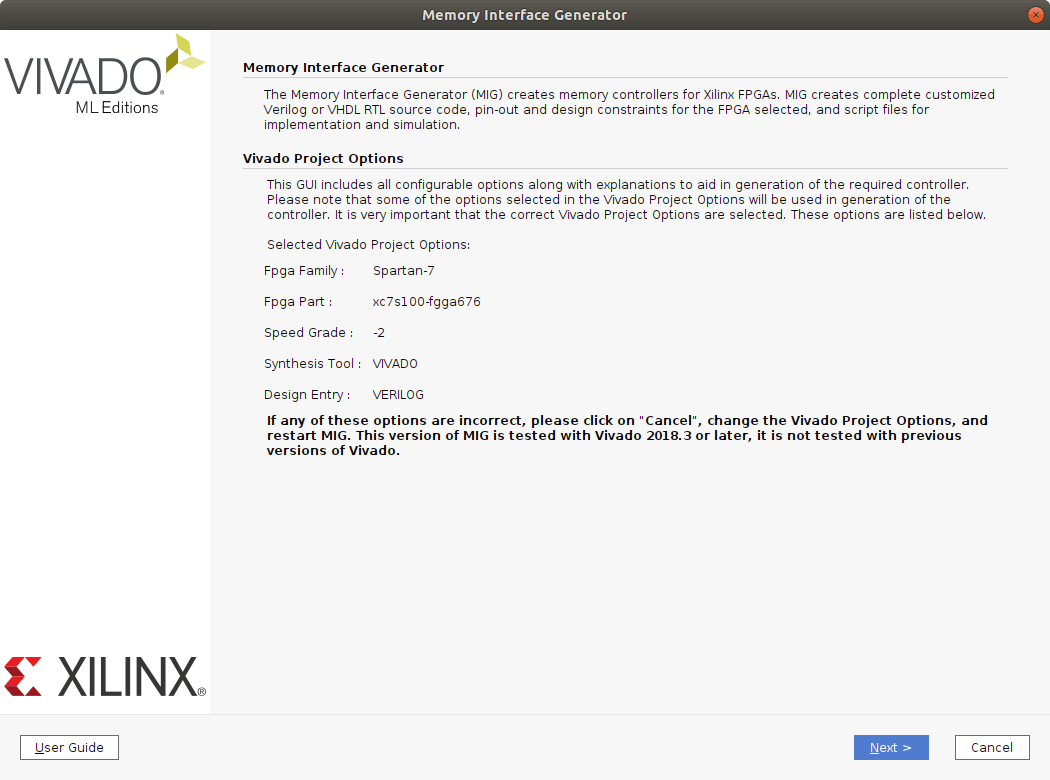

双击Memory Interface Generator IP 模块以打开其定制窗口。

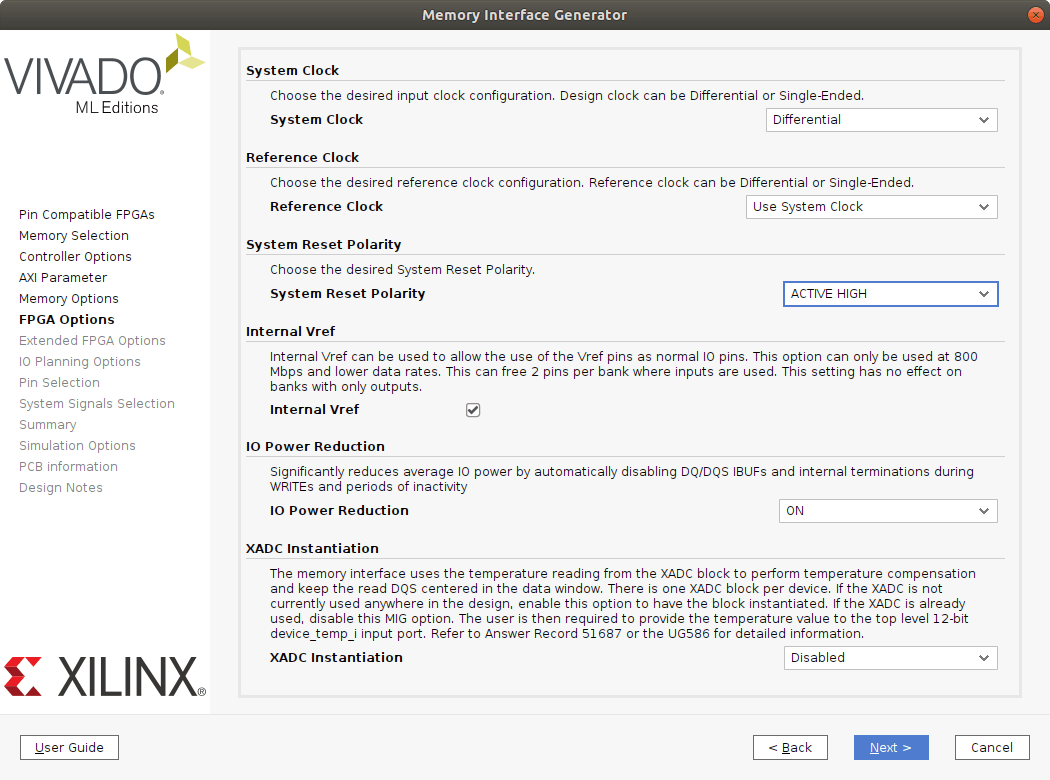

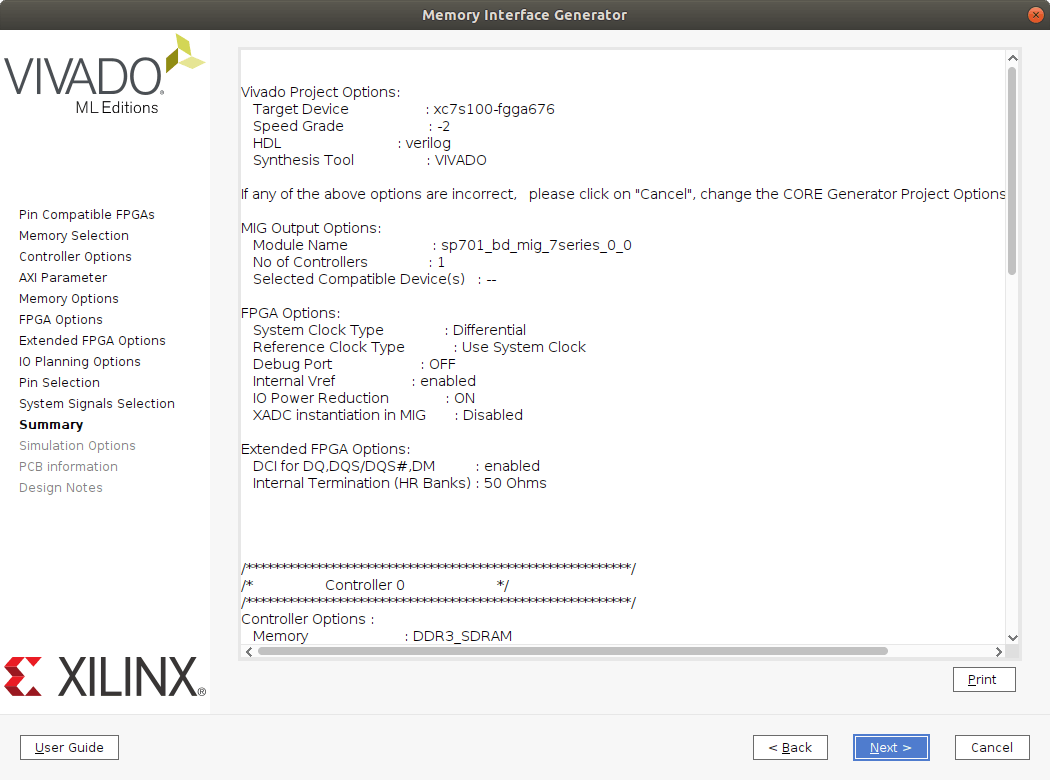

在FPGA Options下,将System Reset Polarity更改为Active High并将XADC Instantiation更改为Disabled 。

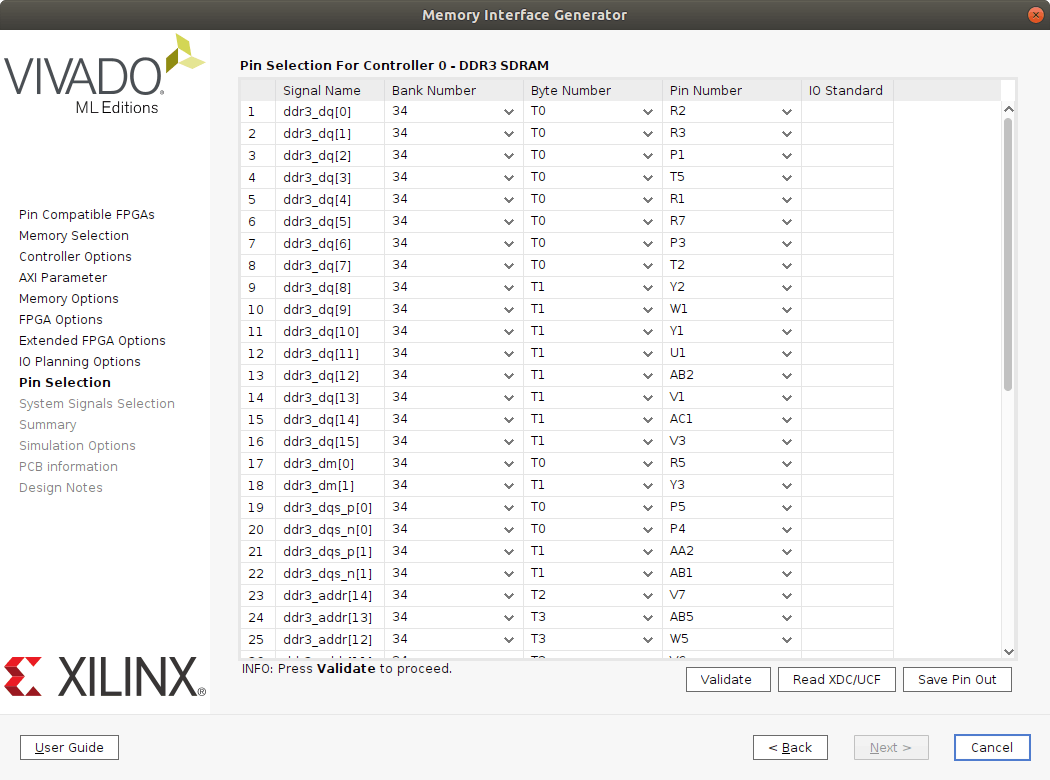

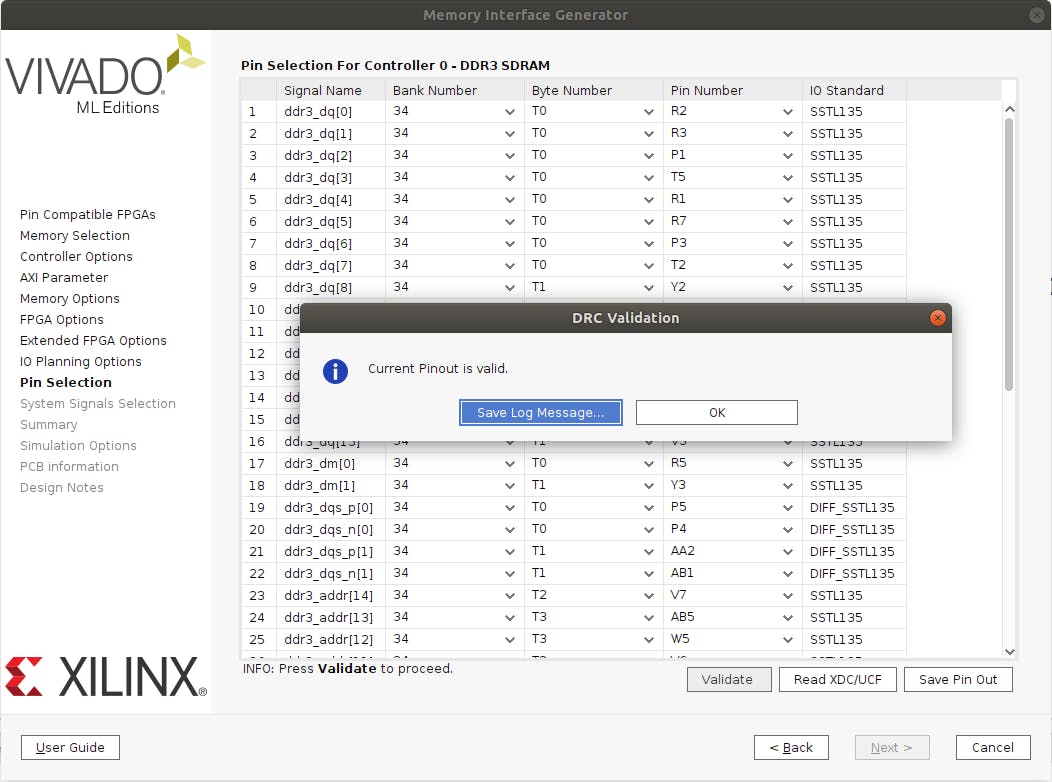

在Pin Selection选项卡中,单击 Read UCF/XDC 并导航到您保存 SP701 (mig_7series_0.xdc) 的 DDR 引脚输出文件的位置,以将其读入 Memory Interface Generator (MIG) IP 块。

导入 DDR 引脚后,单击Validate 。验证引脚后,下一步按钮将不再灰显。

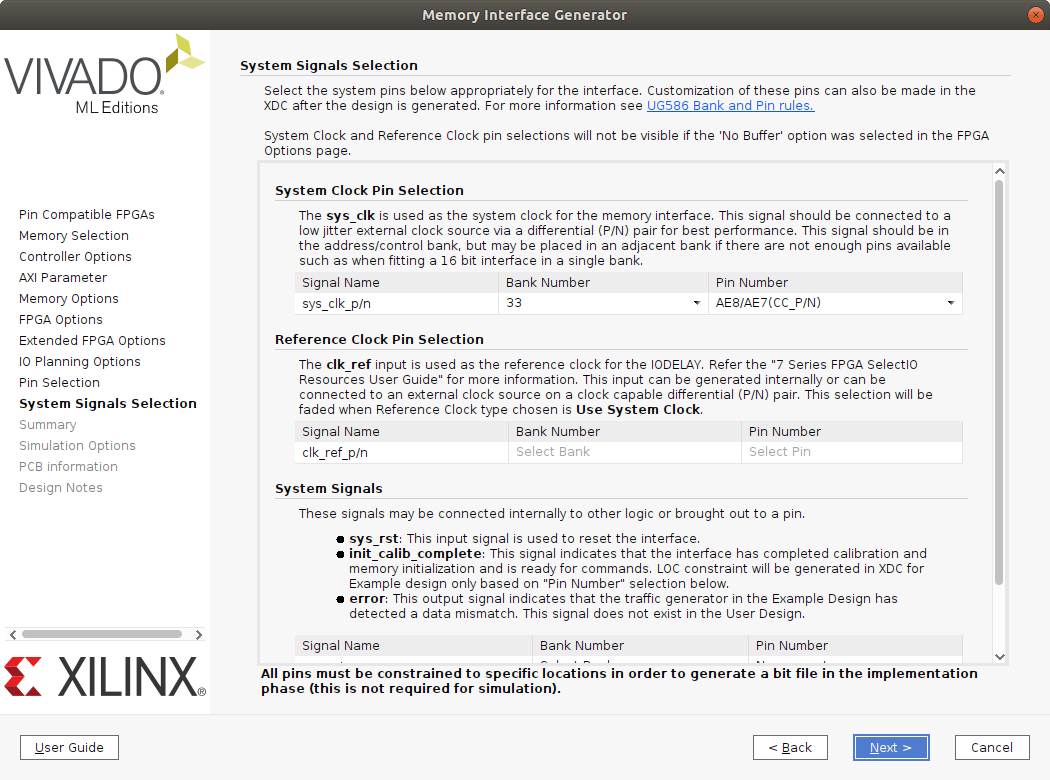

在System Signals Selection选项卡中,将sys_rst Bank Number设置为13 ,将 sys_rst Pin Number设置为AE15 。

单击显示指定配置摘要的其余选项卡,然后在最后一页上单击Generate 。

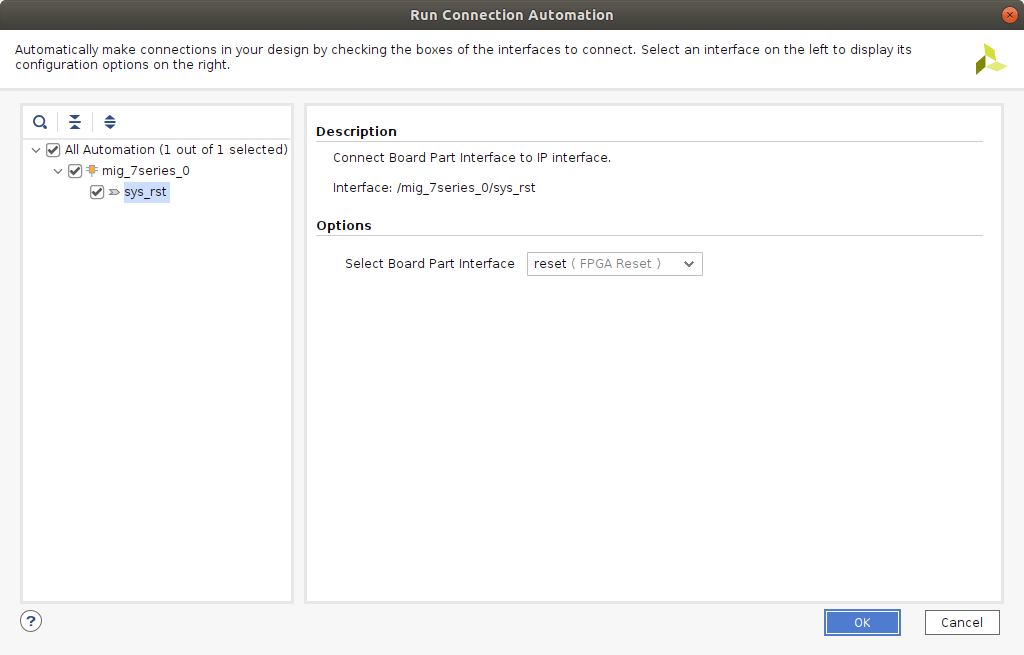

现在运行生成的连接自动化,它会在 Block Design 窗口顶部以绿色横幅弹出,以连接 FPGA 复位信号。

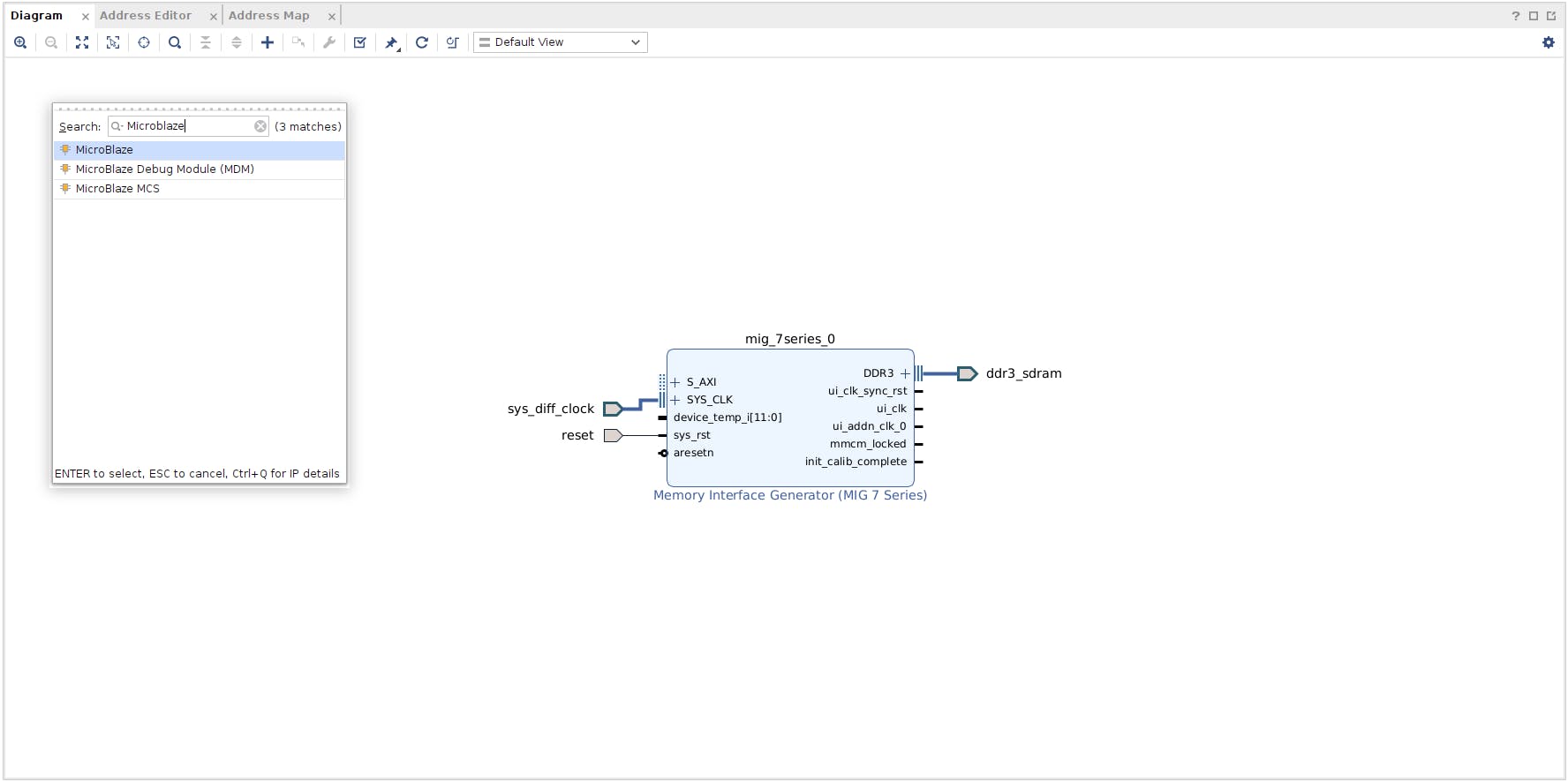

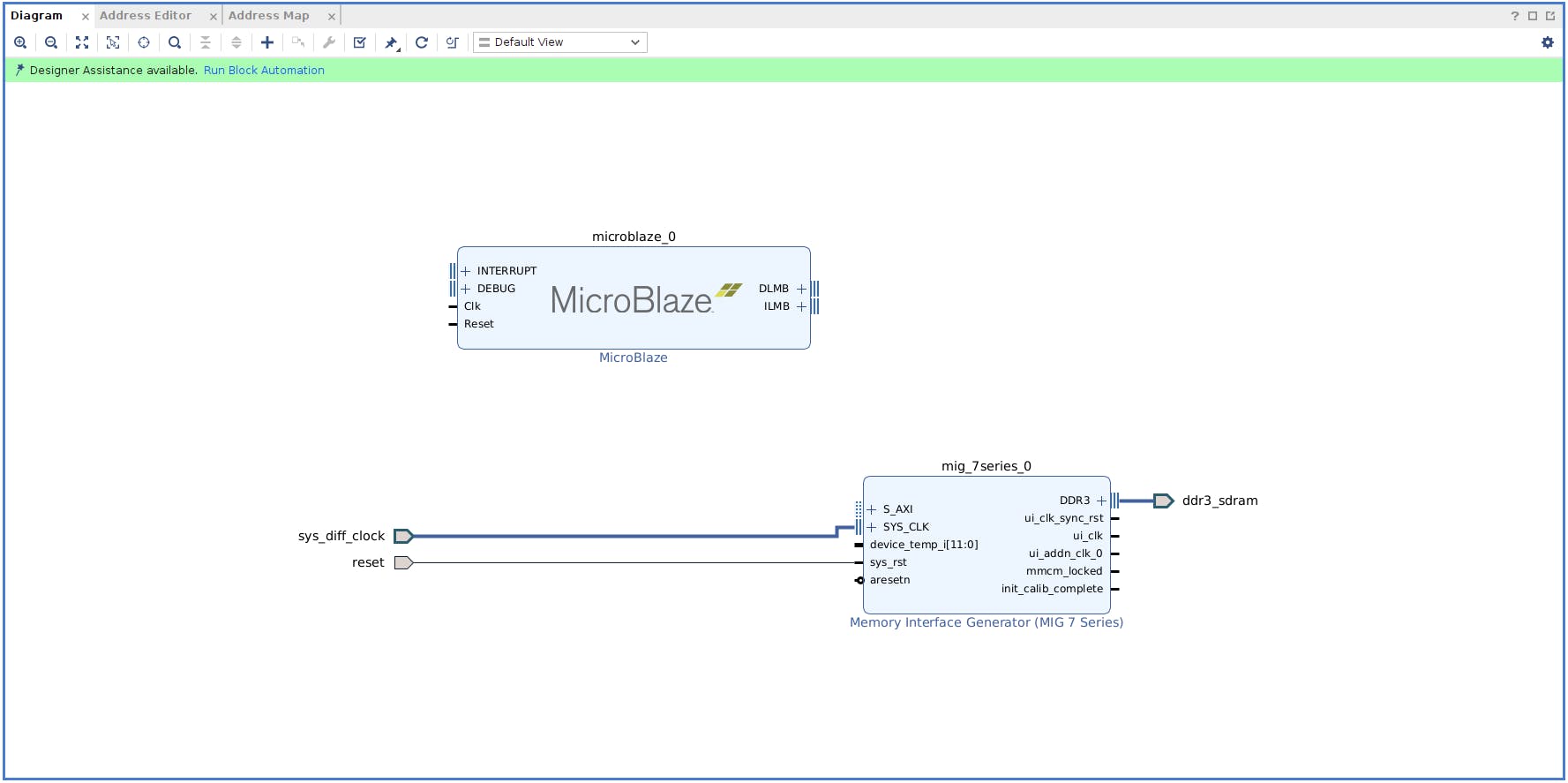

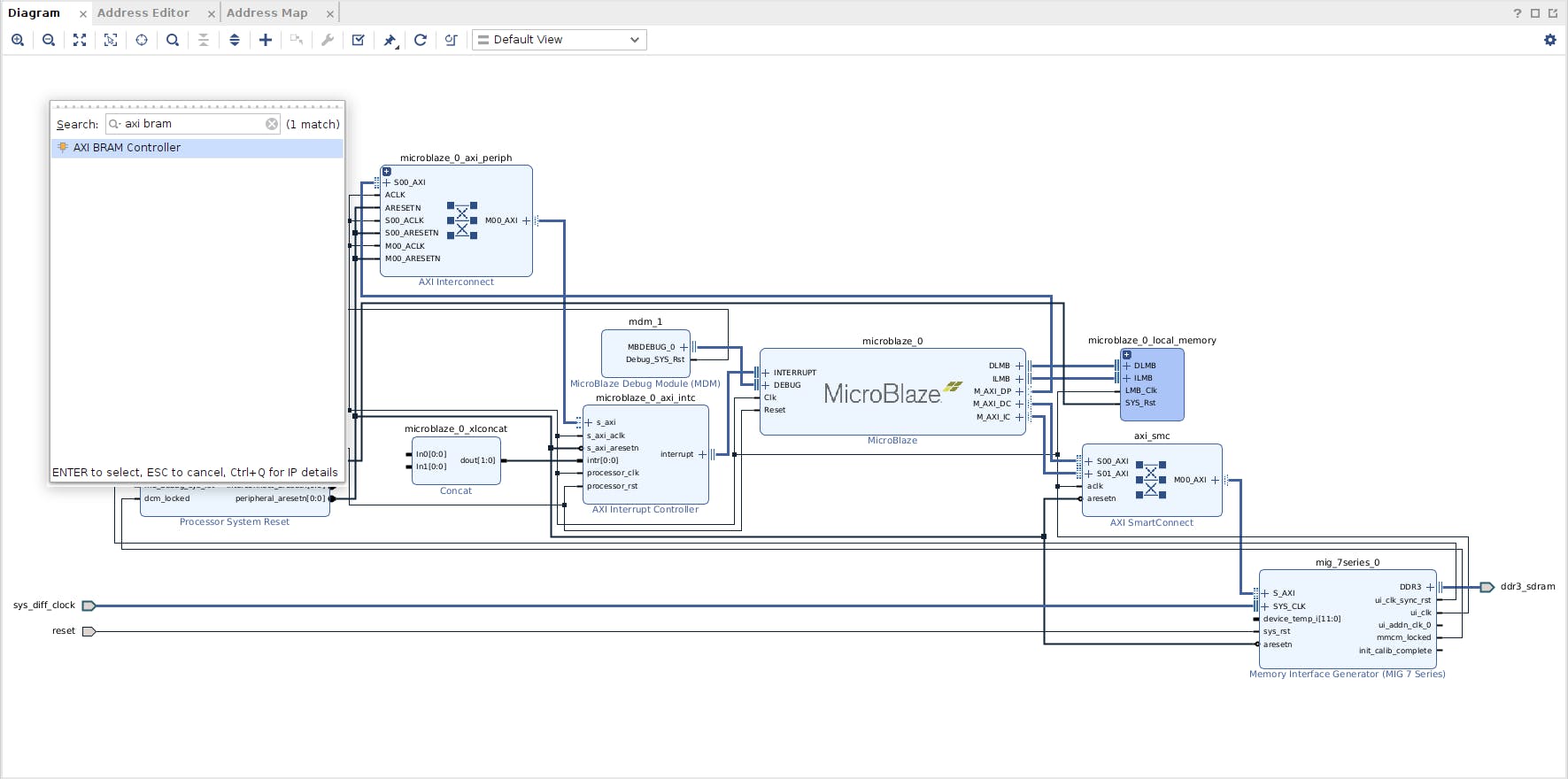

单击块设计窗口顶部的+按钮并键入microblaze以搜索软处理器 IP 块。在三个选项中,双击MicroBlaze将软处理器的核心添加到块设计中。

块自动化和连接自动化的选项将出现在块设计窗口的顶部。

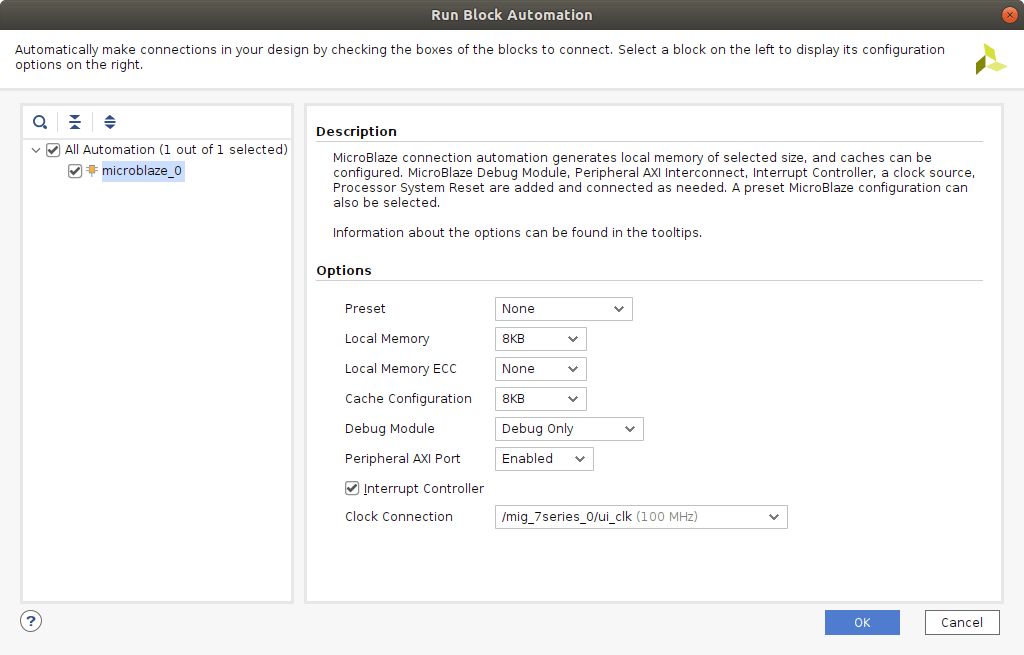

首先运行块自动化并选中该框以启用中断控制器。还将时钟连接更改为来自/mig_7series_0/ui_clk 。由于这个外部存储控制器是启动、运行和同步所需的最长时间,因此最好将其他所有东西(例如软处理器本身)放在它的下游。因此,MIG 的输出时钟被用作 MicroBlaze 的源时钟以及将在块设计中的 IP 的其余部分。

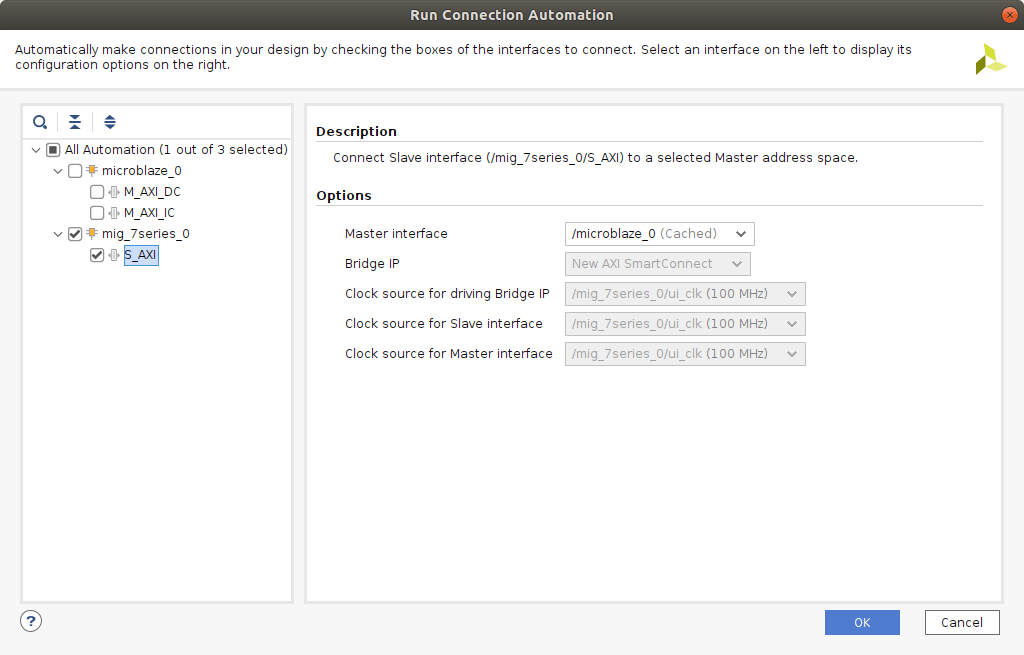

为 MicroBlaze运行Block Automation后,运行Connection Automation 。在运行连接自动化的可用选项中,仅选择MIG ( mig_7series_0 ) 的从 AXI ( S_AXI ) 的连接自动化。

再次单击块设计窗口顶部的+按钮,并将AXI BRAM 控制器添加到块设计中。运行 AXI BRAM 控制器的所有连接自动化,确保将S_AXI 主接口设置为/microblaze_0 (cached) 。

返回Board选项卡并右键单击Onboard PHY1并选择Connect Board Component ,然后从弹出窗口中选择选项AXI 1G/2.5G Ethernet Subsystem 。

运行生成的Block Automation,为Physical Interface Selection选择RGMII ,为AXI Streaming Interface选择DMA 。

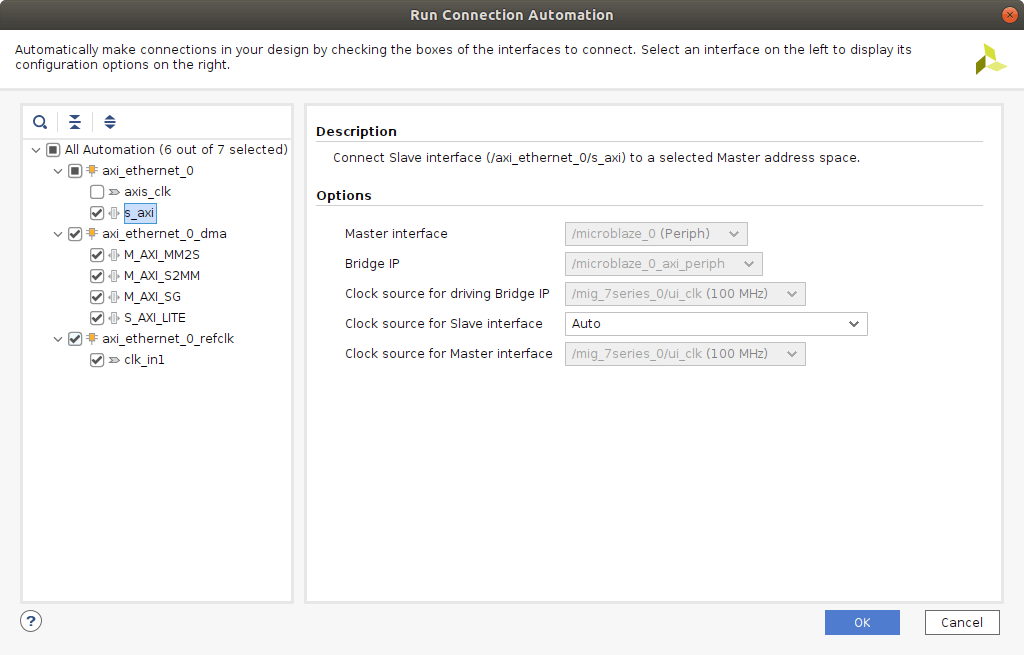

对于AXI 1G/2.5G以太网子系统的连接自动化,不要选择axis_clk (这将在下一步中手动连接)。要重置 Connection Automation,请进行以下选择:

对于axi_ethernet_0 :

- 选择时钟源为/mig_7series_0/ui_clk的S_AXI

对于axi_ethernet_0_dma :

- 选择源为/mig_7series_0/S_AXI的M_AXI_MM2S 、M_AXI_S2MM和M_AXI_SG 。

- 选择源为/microblaze_0 ( Periph ) 的 S_AXI_LITE

对于axi_ethernet_0_refclk :

- 选择源为/mig_7series_0/ui_clk的clk_in1

运行此 Connection Automation 后,返回并手动将axi_ethernet_0的axis_clk连接到axi_ethernet_0_refclk的clk_ou1

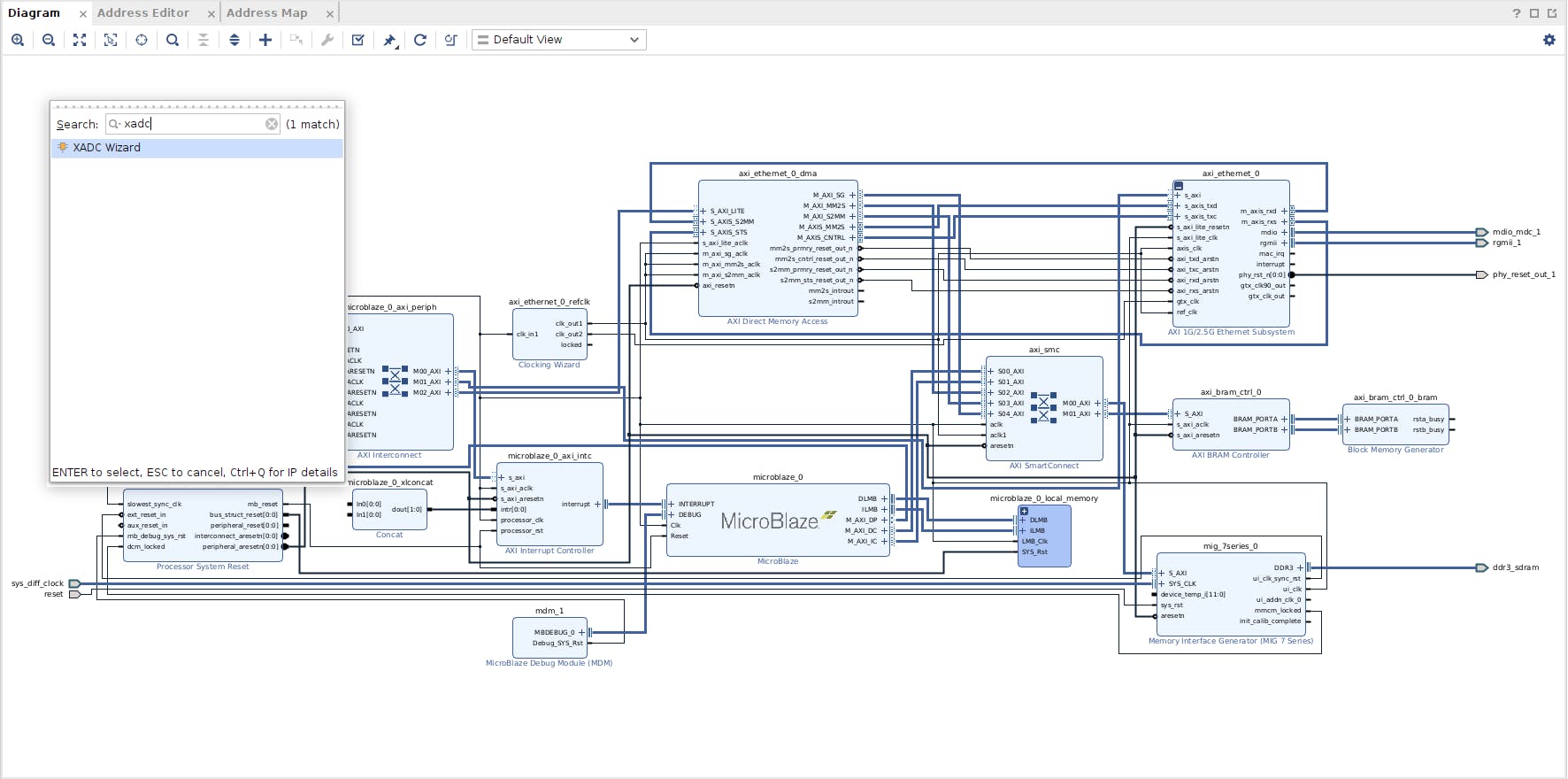

接下来,单击模块设计窗口顶部的+按钮,并将XADC向导添加到模块设计中。运行生成的连接自动化,将其源设置为/microblaze_0 (Periph)

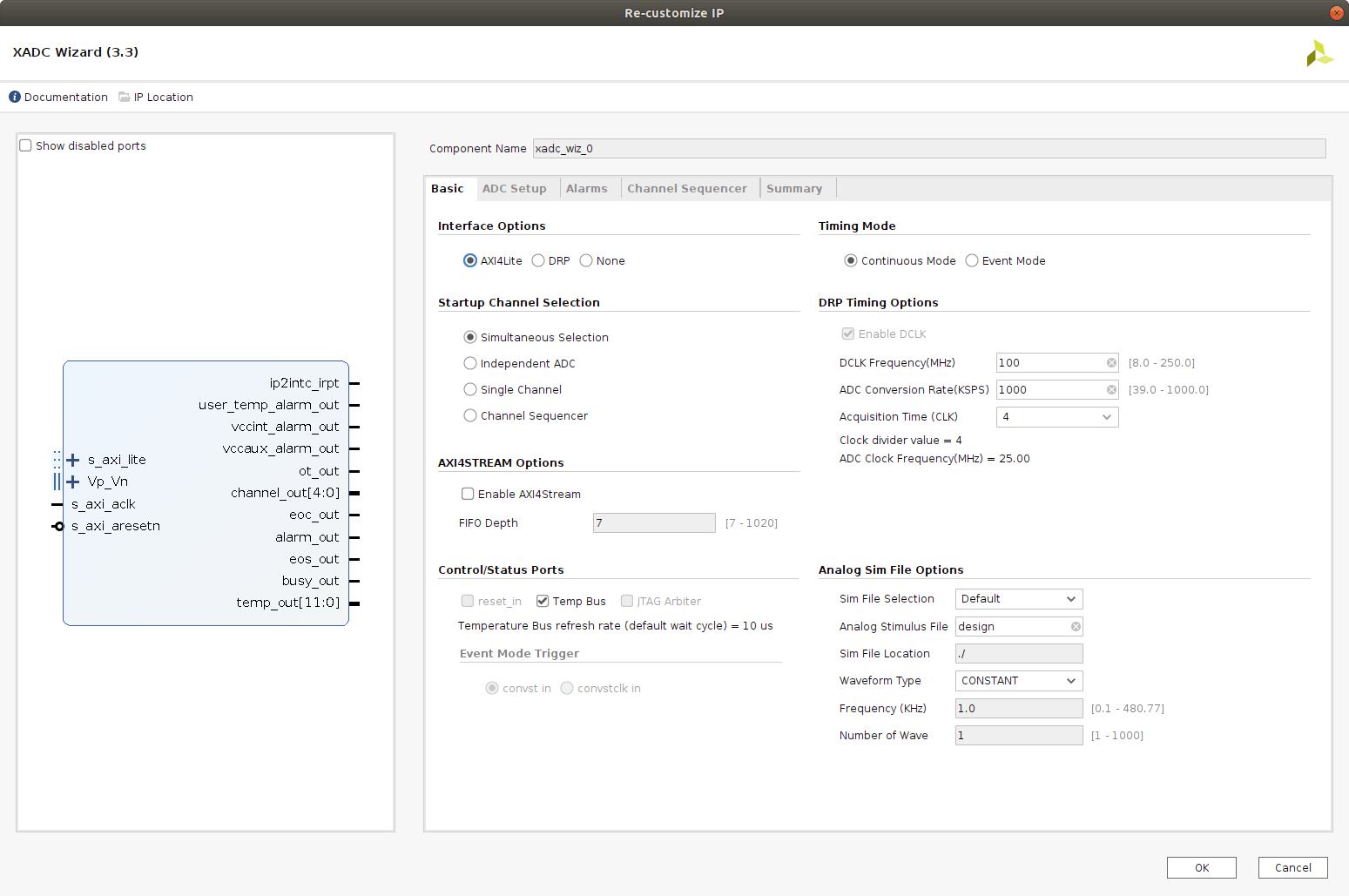

双击XADC Wizard IP 以打开其自定义窗口并在指定选项卡下进行以下更改:

- 基本:将启动通道选择更改为同时选择并在控制/状态端口下启用临时总线

- 通道定序器:启用vauxp0/vauxn0 通道启用

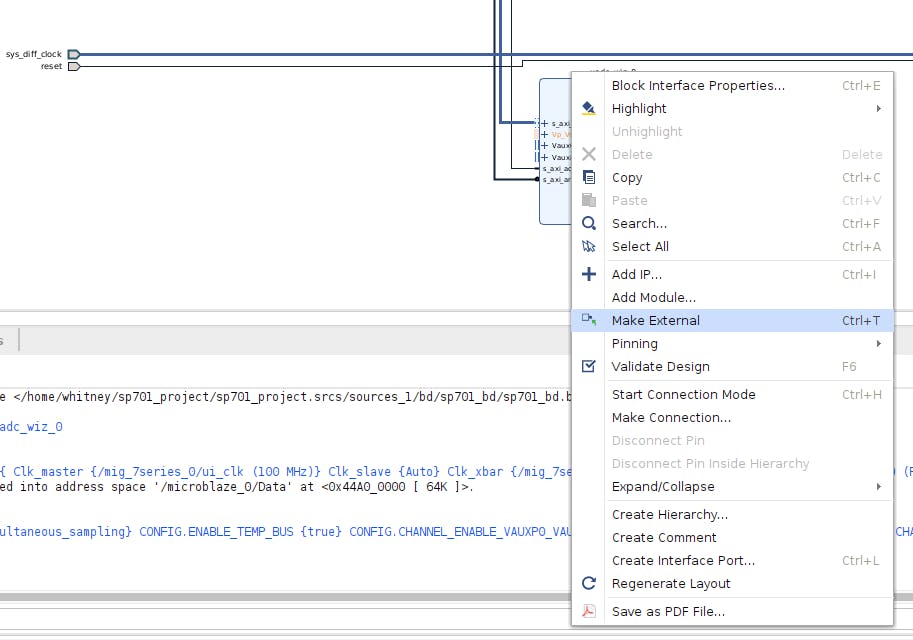

单击确定应用并关闭自定义窗口。右键单击XADC Wizard IP 块的Vp_Vn端口,然后选择Make External选项。对Vaux0和Vaux8执行相同的操作。这个Make External选项将信号拉到设计的顶层,这样它就可以连接到 FPGA 芯片的封装引脚。

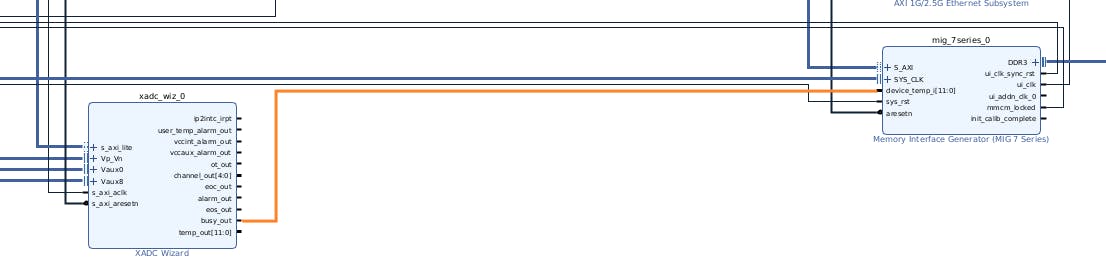

最后手动将XADC Wizard的temp_out[11:0]连接到Memory Interface Generator的device_temp_i[11:0] 。

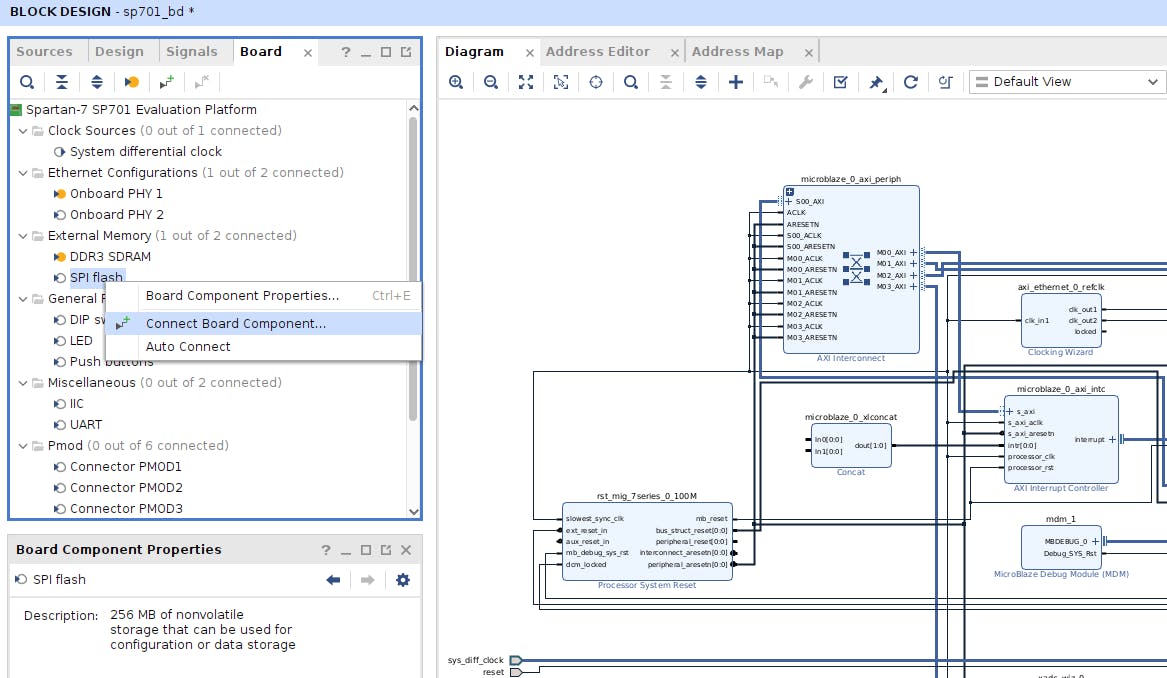

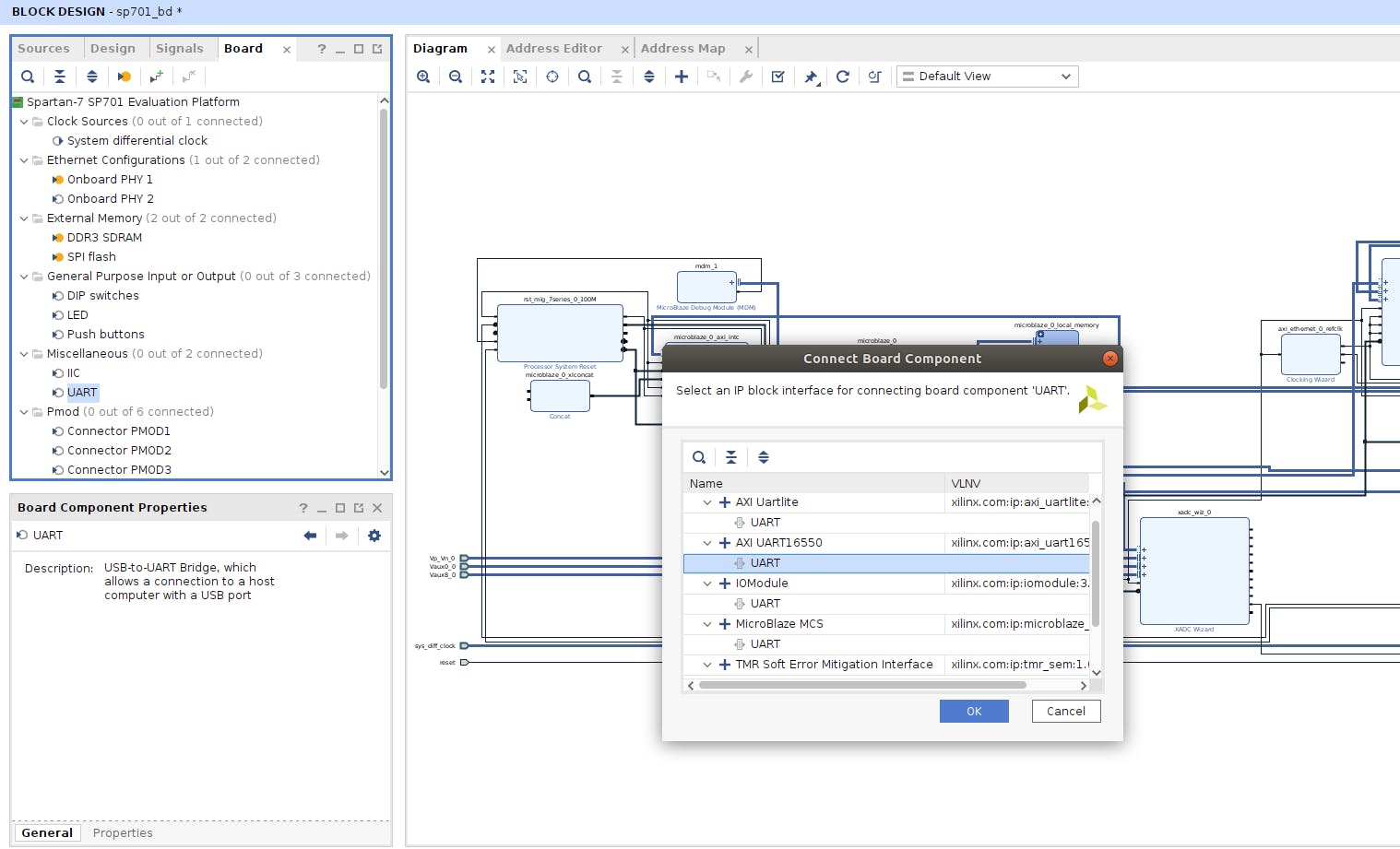

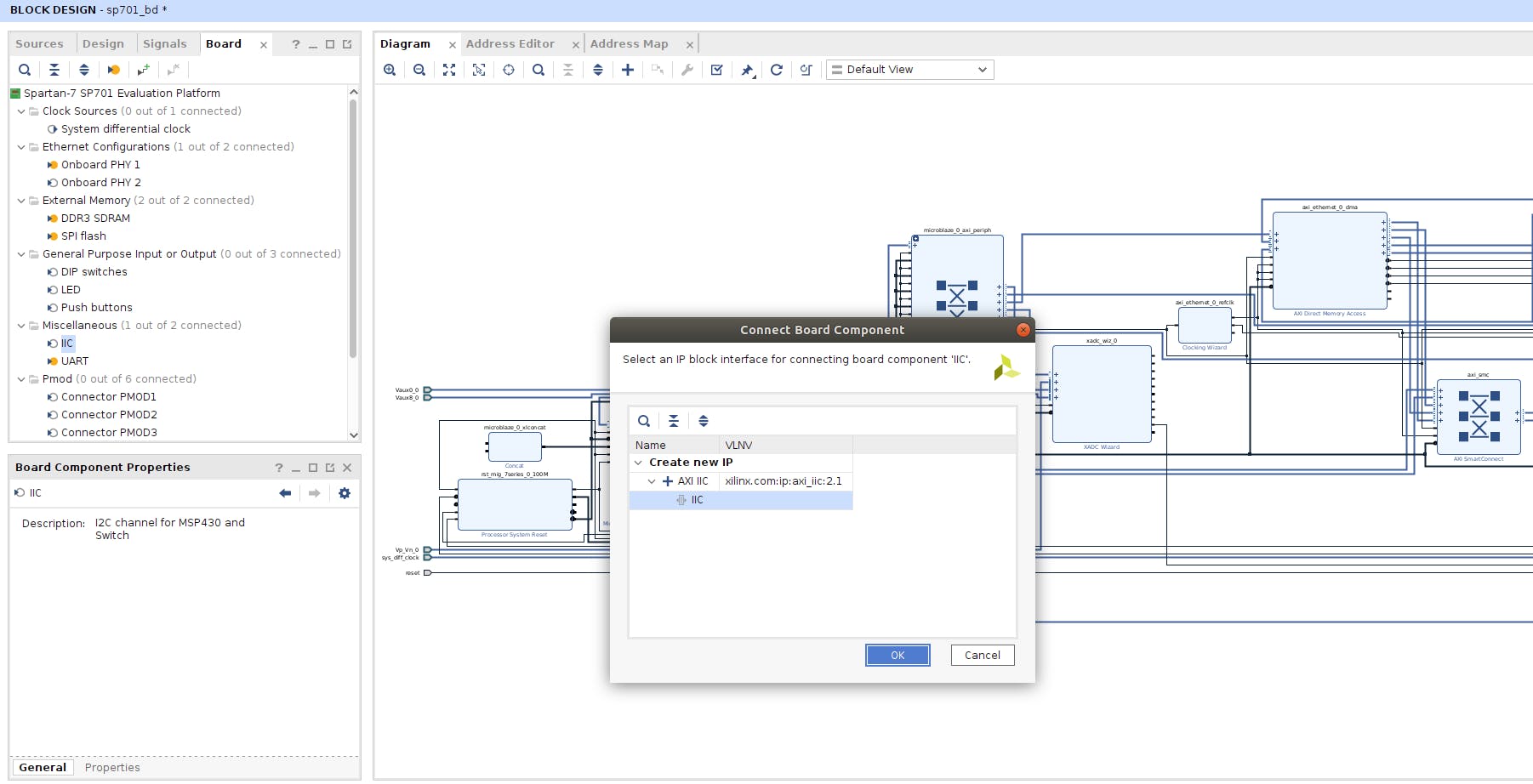

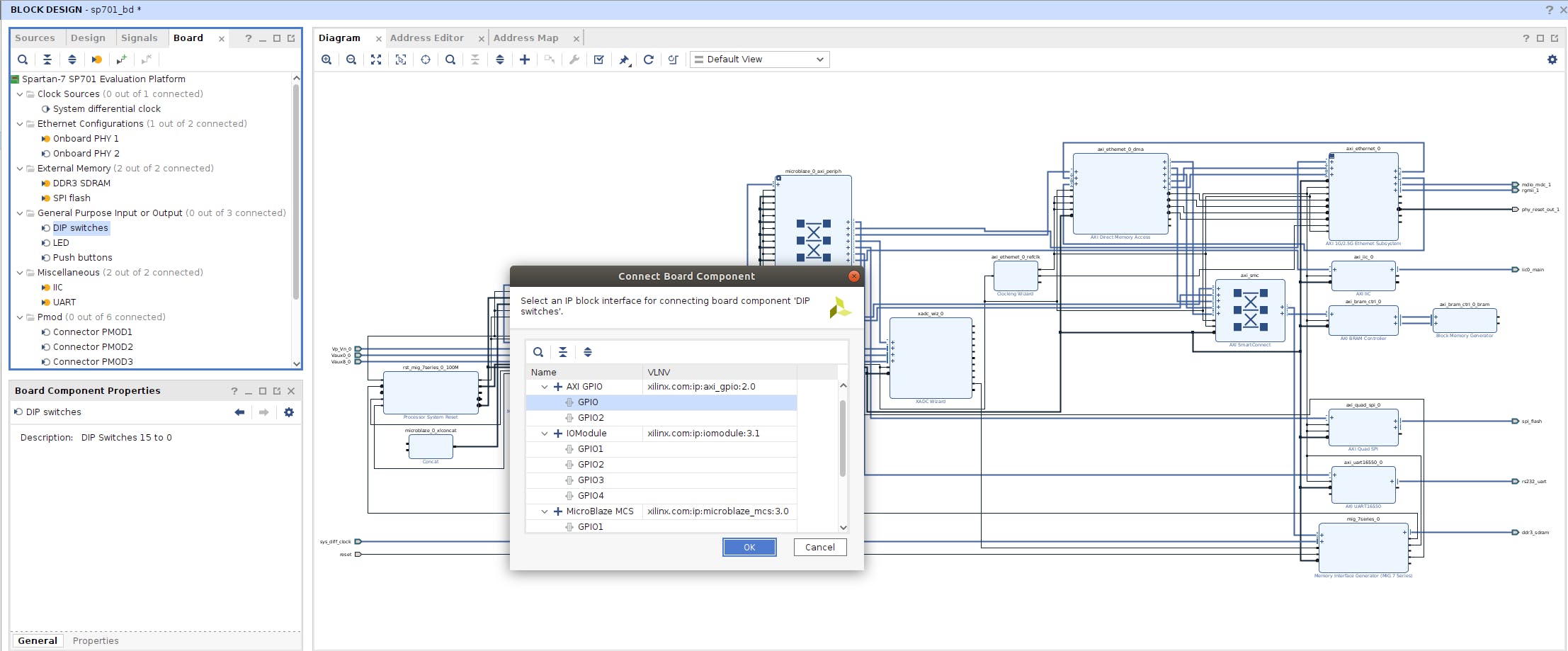

至此,设计中最复杂的部分就完成了。现在可以添加其余的外围设备。返回到 Board 选项卡,右键单击以下每个外围设备,选择Connect Board Component ,然后为每个相应的 IP 选择以下内容:

- SPI Flash :选择SPI_0并运行生成的 Connection Automation,时钟源为/mig_7series_0/ui_clk 。

- UART:选择AXI UART16550并运行生成的 Connection Automation,时钟源为/mig_7series_0/ui_clk 。

- IIC :选择IIC并运行生成的 Connection Automation,时钟源为/mig_7series_0/ui_clk 。

- DIP 开关、按钮和LED :选择GPIO并运行生成的 Connection Automation,时钟源为/mig_7series_0/ui_clk 。

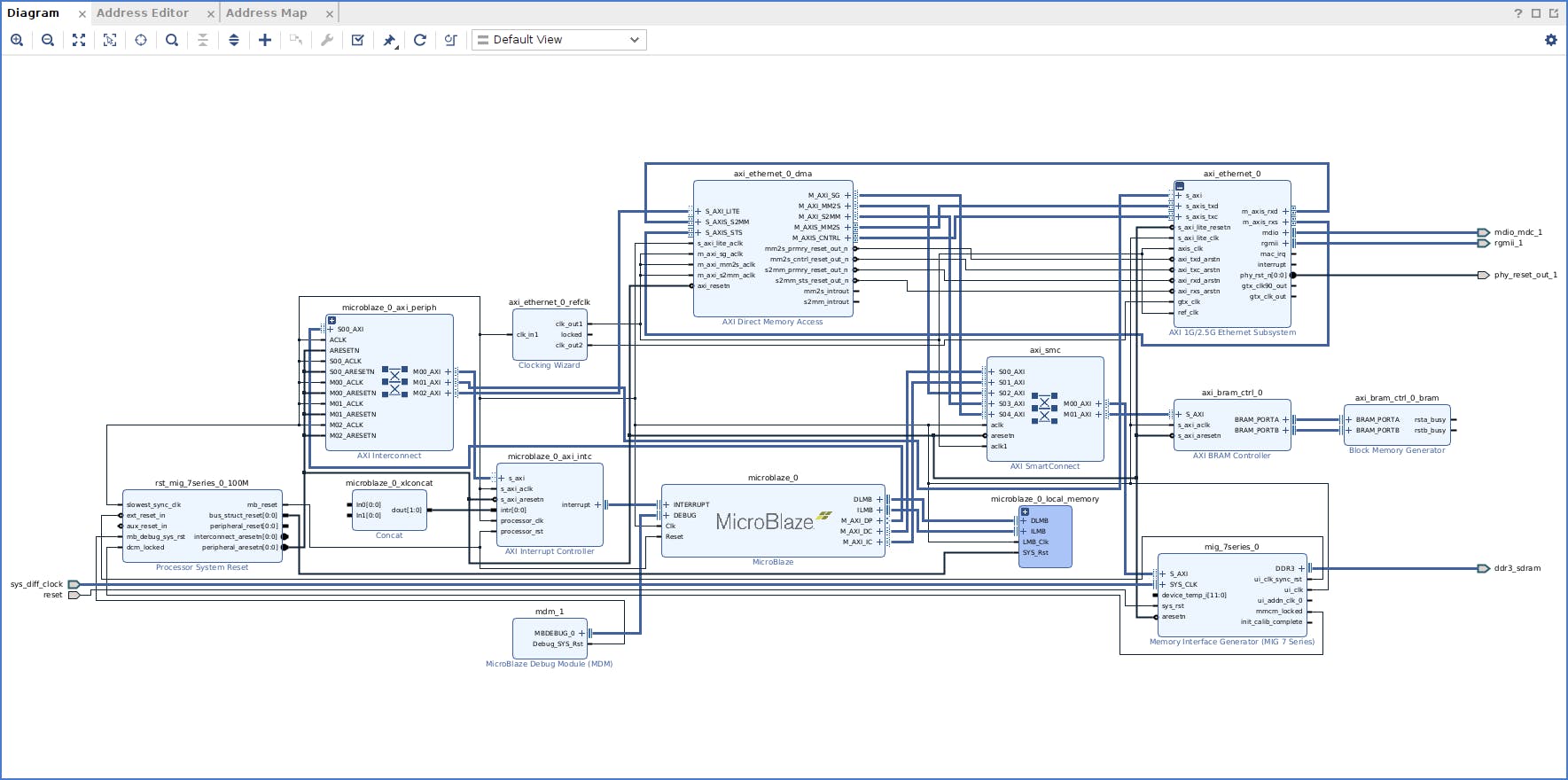

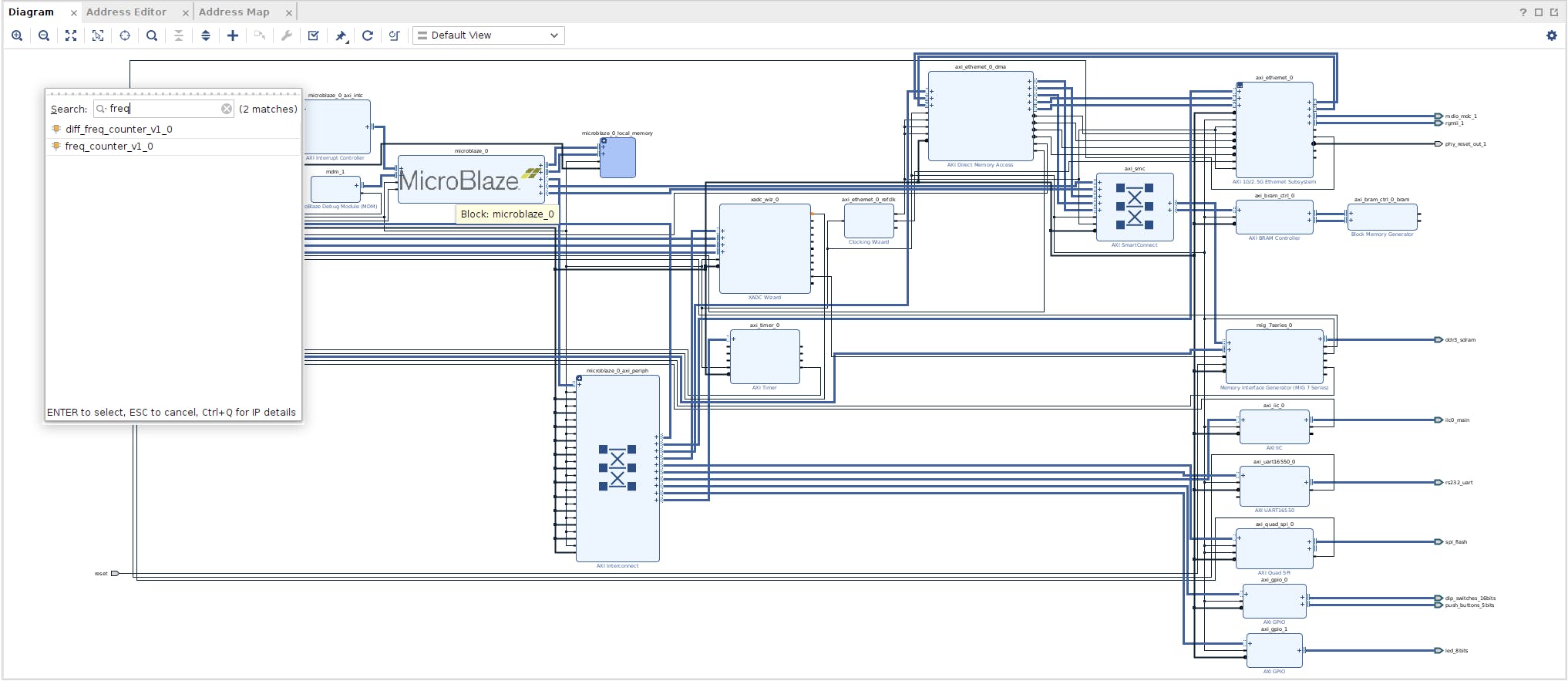

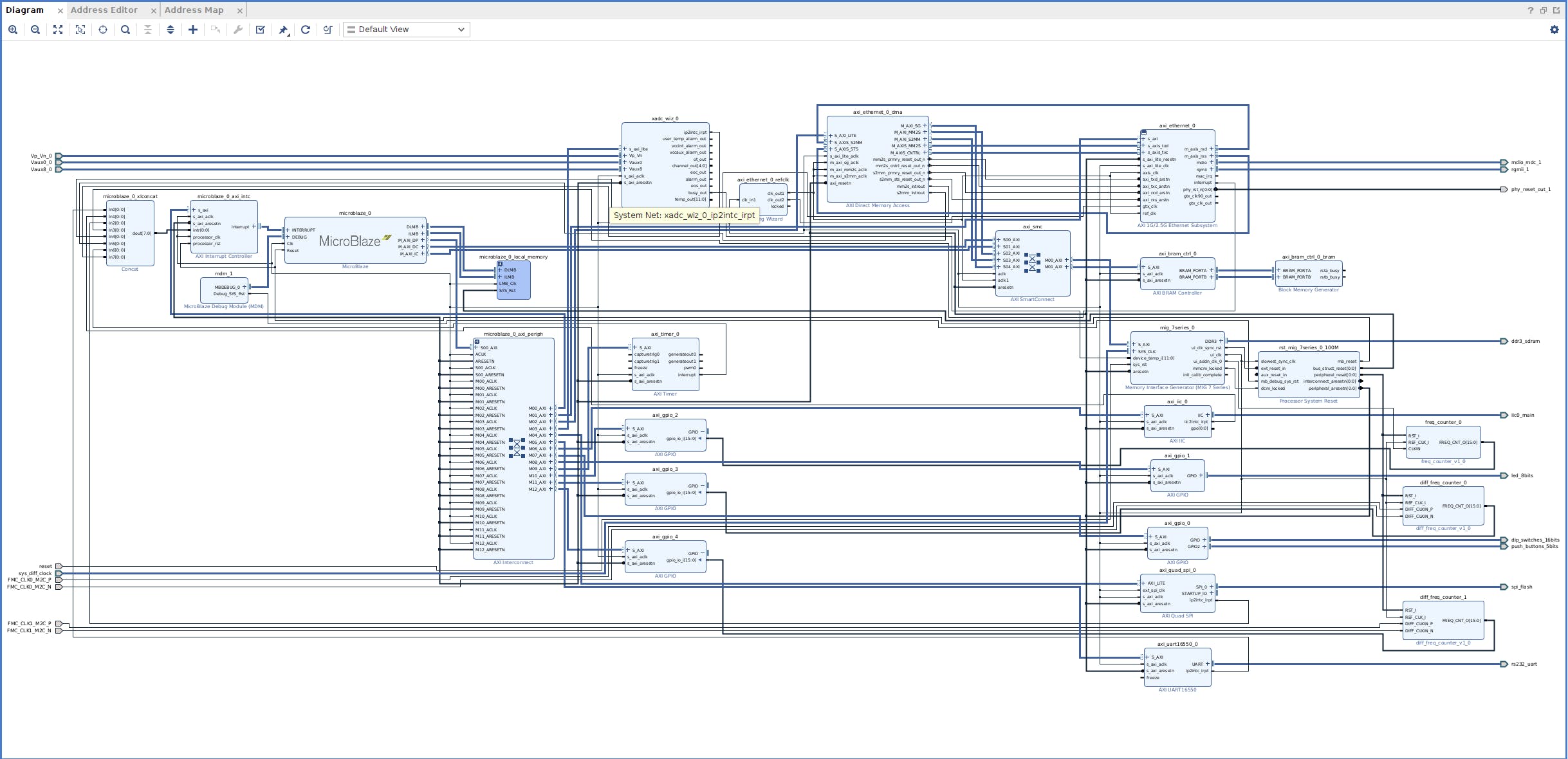

产生以下块设计:

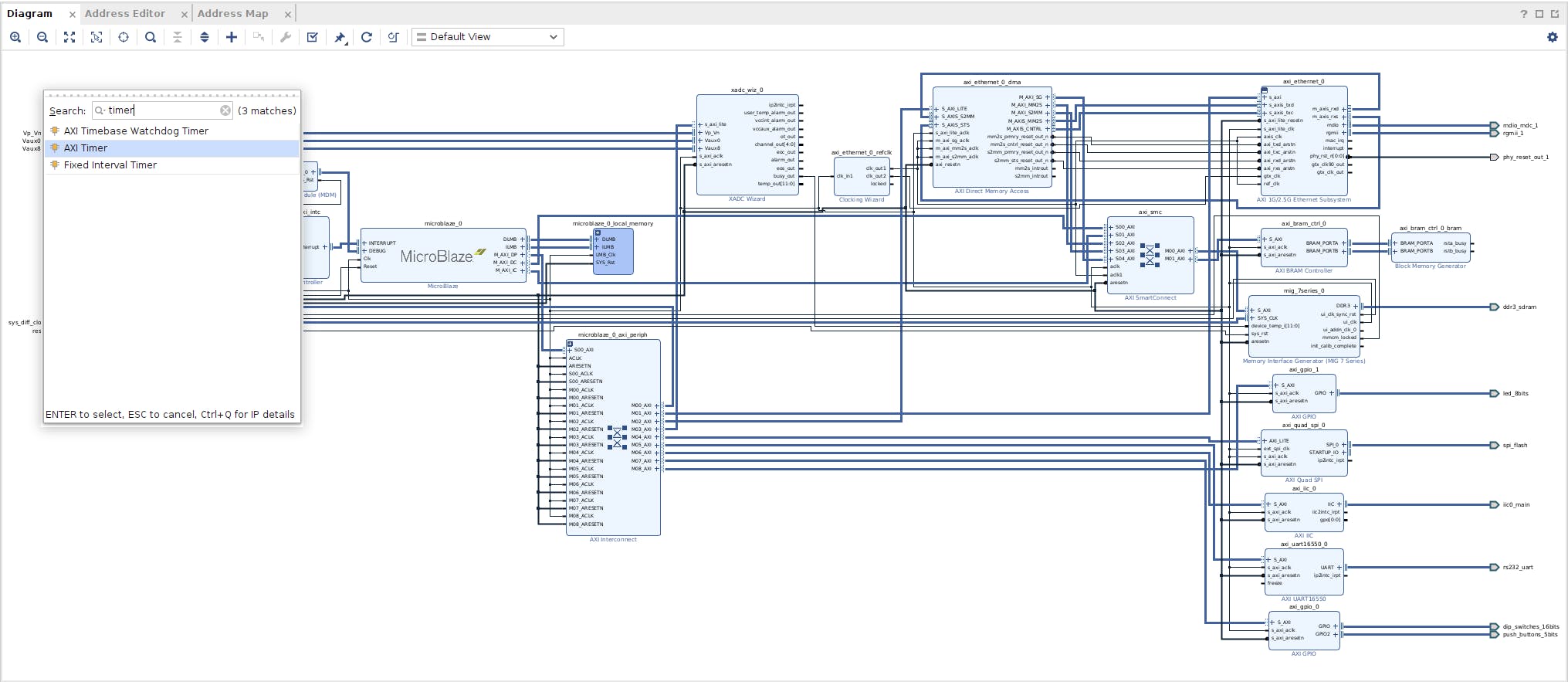

单击模块设计窗口顶部的+按钮并将AXI Timer IP 添加到模块设计,再次运行生成的连接自动化,时钟源为/mig_7series_0/ui_clk 。

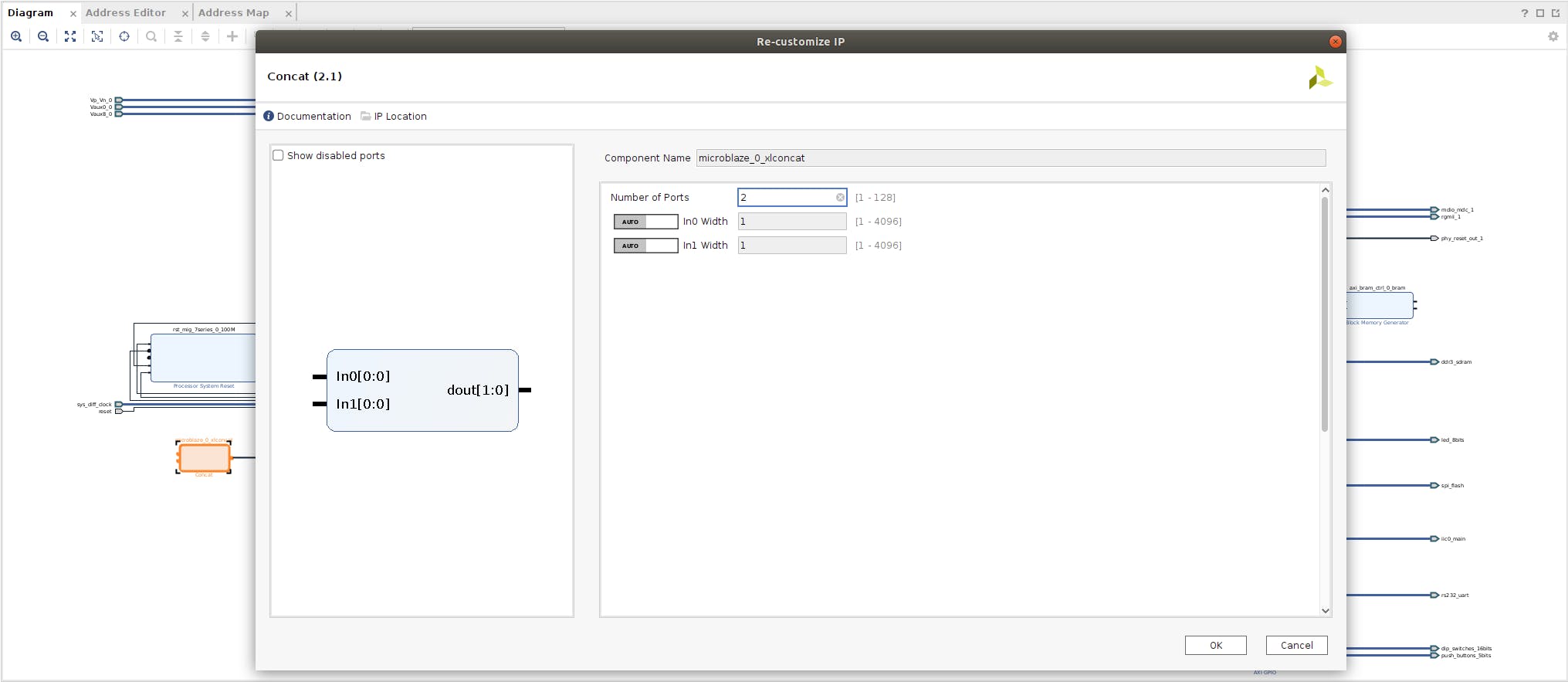

有一个concat IP 块为AXI 中断控制器IP的中断输入端口供电。默认情况下,此 concat 仅配置为接收两个输入,但总共有 8 个中断信号需要通过 AXI 中断控制器馈送到 MicroBlaze 软处理器。双击 concat IP 打开其配置窗口并将其端口数从2更改为8 ,然后单击OK 。

按以下顺序连接中断输出:

- In0 :AXI UART16550 ip2intc_irpt

- In1 :AXI IIC ip2intc_irpt

- In2 :AXI Quad SPI ip2intc_irpt

- In3 :AXI 1G/2.5G 以太网子系统中断

- In4 :AXI 直接内存访问mm2s_introut

- In5 :AXI 直接内存访问s2mm_introut

- In6 :AXI 定时器中断

- In7 :XADC 向导ip2intc_irpt

有一些自定义频率计数器 IP 可用于各种应用。我已将它们附在下面,您需要将它们放在本地目录中,然后将该目录指定为 Vivado 项目中的存储库。

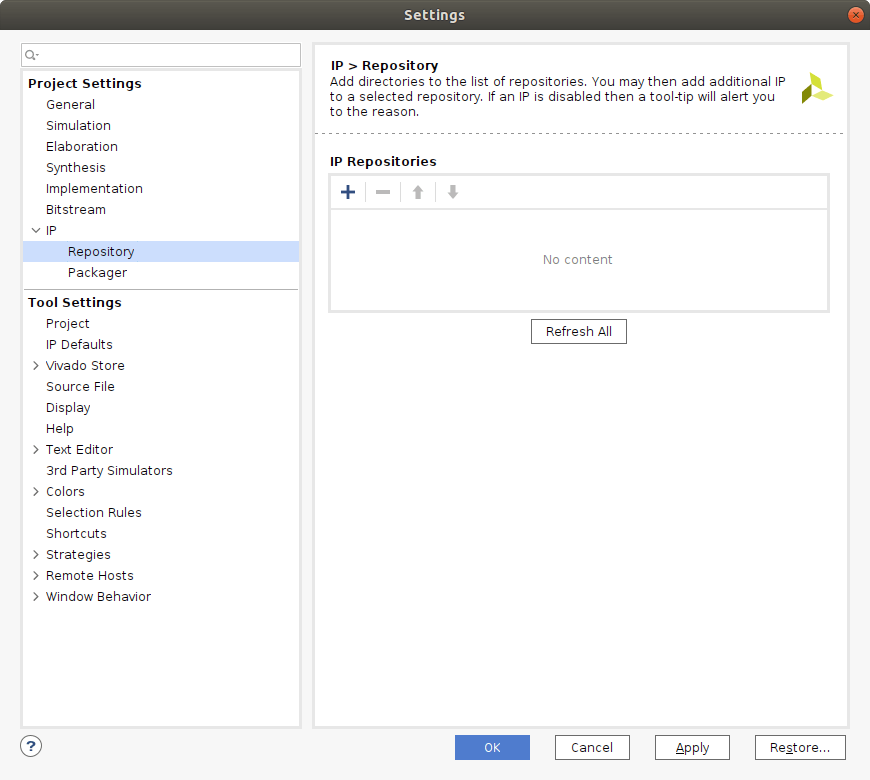

将 IP 文件夹复制到所需的本地目录后,从Flow Navigator窗口中选择Settings 。选择IP > Repository ,然后单击+按钮并指向 IP 文件夹所在的本地目录。Vivado 将弹出一个窗口,显示它在目录中检测到的 IP。单击确定。

单击应用,然后单击确定。

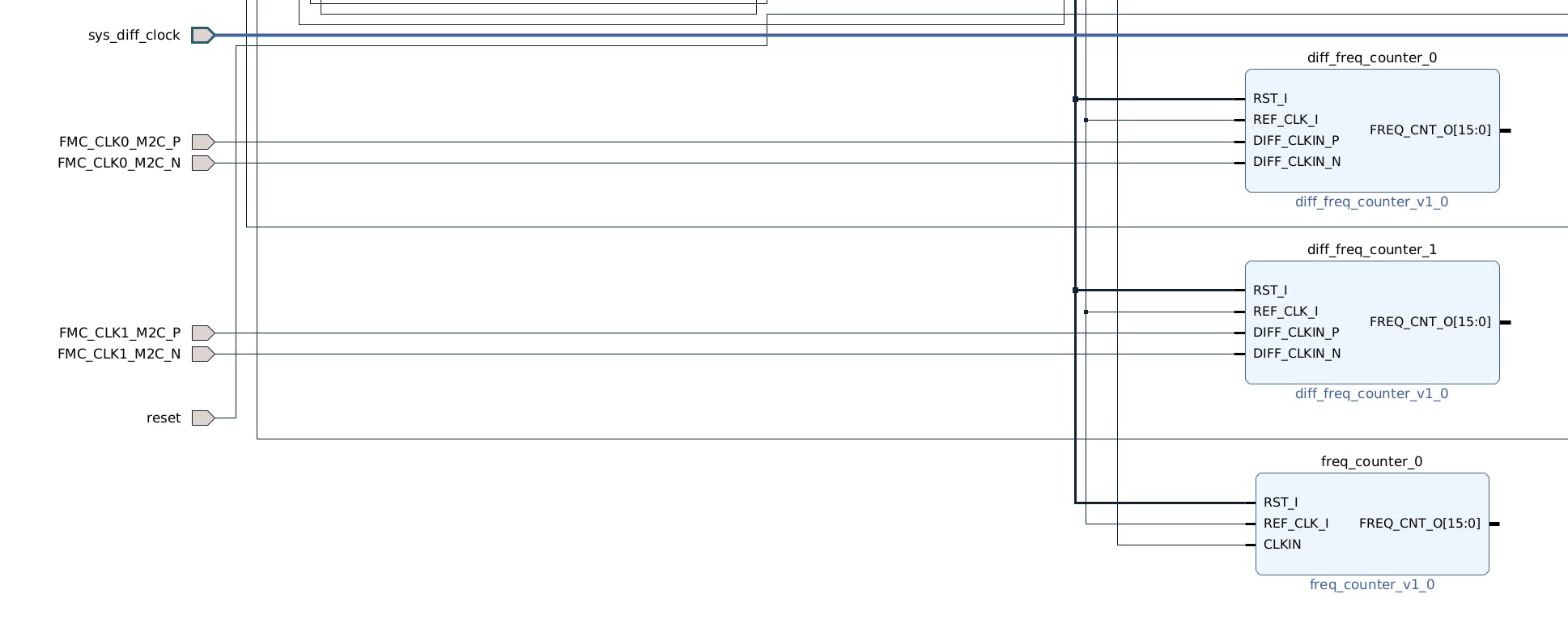

在模块设计窗口中,单击+按钮并添加一个freq_counter_v1 IP 模块和两个diff_freq_counter_v1 IP 模块。将每个的 RST_I连接到rst_mig_7series_0_100M的peripheral_reset ,将每个的REF_CLK_I连接到mig_7series_0的ui_clk 。

将freq_counter_v1_0的CLKIN连接到mig_7series_0的ui_addn_clk_0 。

右键单击diff_freq_counter_v1_0的DIFF_CLKIN_P和DIFF_CLKIN_N并选择 Make External。然后分别重命名端口FMC_CLK0_M2C_P和FMC_CLK0_M2C_N 。

对diff_freq_counter_v1_1执行相同操作,只是将其端口分别重命名为FMC_CLK1_M2C_P和FMC_CLK1_M2C_N 。

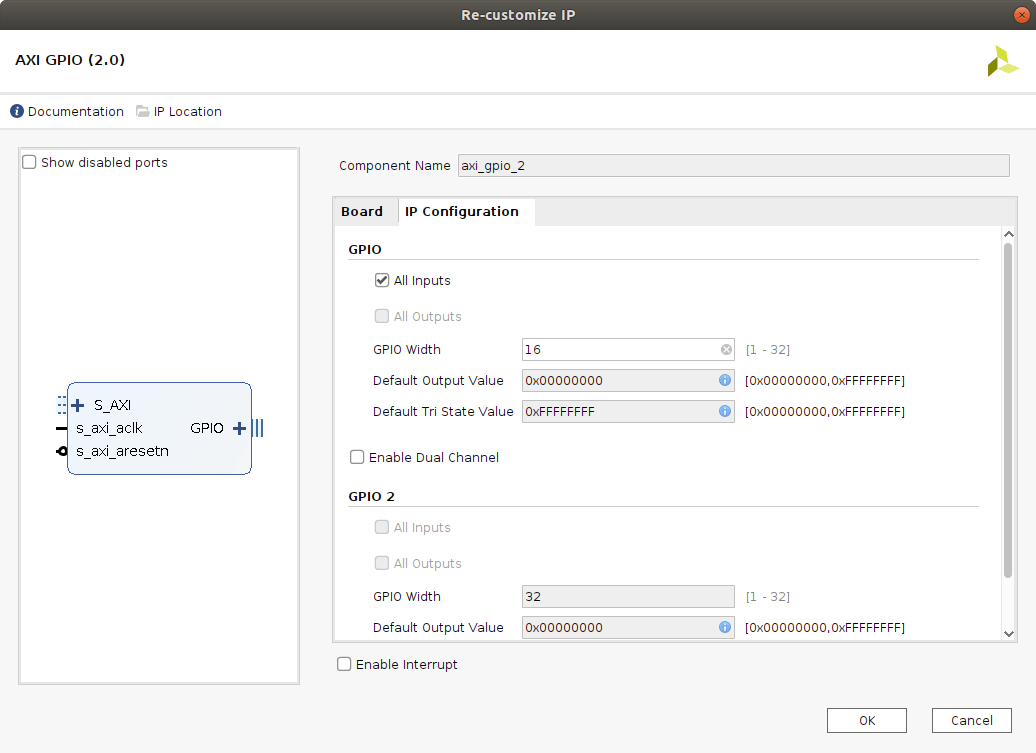

然后添加 3 个AXI GPIO IP 块,其中一个通道为 16 位所有输入。仅为S_AXI接口运行生成的连接自动化,时钟源为/mig_7series_0/ui_clk 。不要在Connection Automation 中为AXI GPIO IP选择GPIO选项。

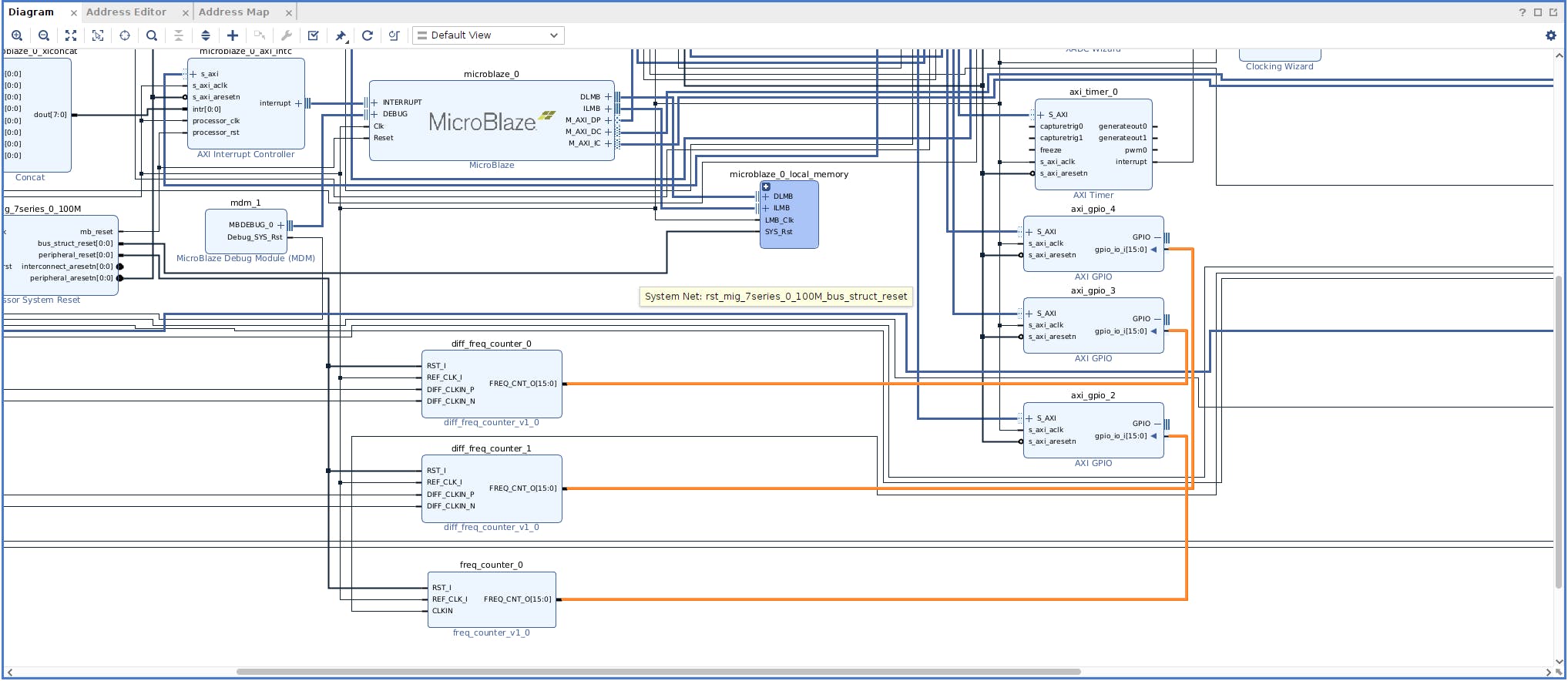

将freq_counter_v1_0的FREQ_CNT_O[15:0]连接到刚刚创建的 3 个 AXI GPIO 块之一的gpio_io_i[15:0] 。

然后从diff_freq_counter_v1_0和diff_freq_counter_v1_1连接FREQ_CNT_O[15:0]并将它们连接到其他两个AXI GPIO块的gpio_io_i[15:0] 。

至此,SP701 这个包罗万象的模块设计就完成了。一旦我达到这一点(我通常在添加 IP 块的每个实例之后执行此操作)就是使用Regenerate Layout工具使块设计更易于查看。单击块设计窗口顶部的圆形箭头图标以重新生成块设计中的布局。

最终设计:

创建任何块设计的最后一步是对其进行验证,以确认它没有任何严重的警告或错误。单击块设计窗口顶部的复选框图标,然后等待验证弹出窗口出现结果:

单击确定并保存块设计。

然后返回“源”选项卡。此时,模块设计需要通过顶层 HDL 文件在整个项目中进行实例化,您可以告诉 Vivado 自动生成该文件。

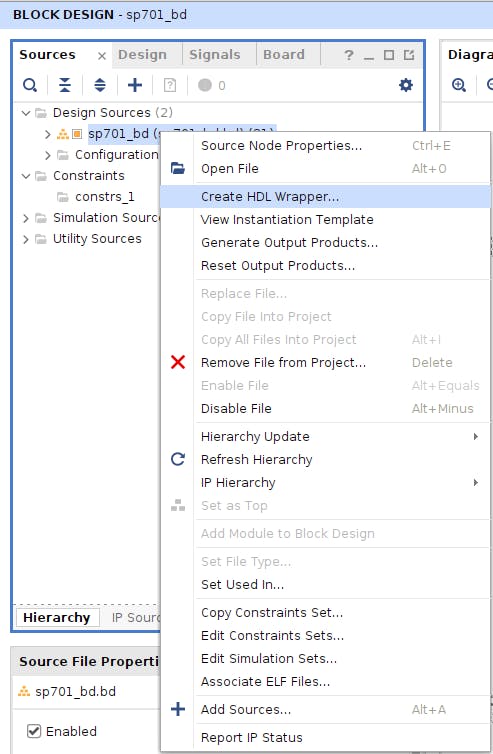

HDL 包装器

右键单击 Sources 选项卡中的模块设计 (.bd) 文件并选择Create HDL Wrapper...让 Vivado 自动生成它。

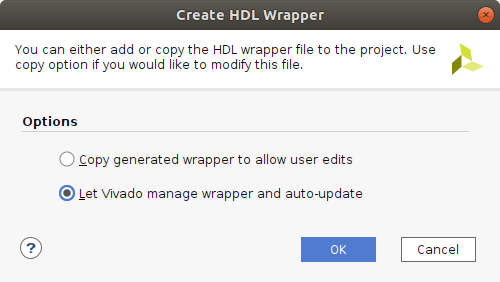

在弹出窗口中,选择默认选项以允许 Vivado 自动管理 HDL 封装文件。

约束

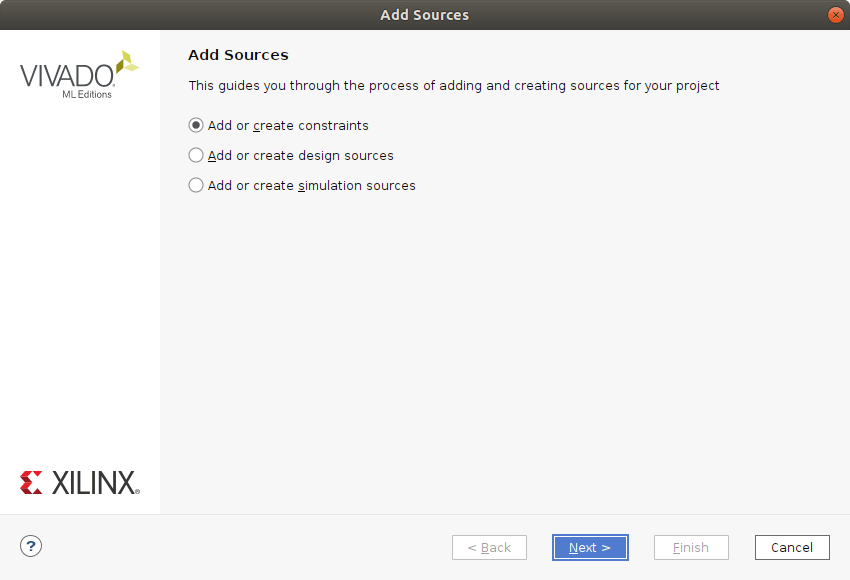

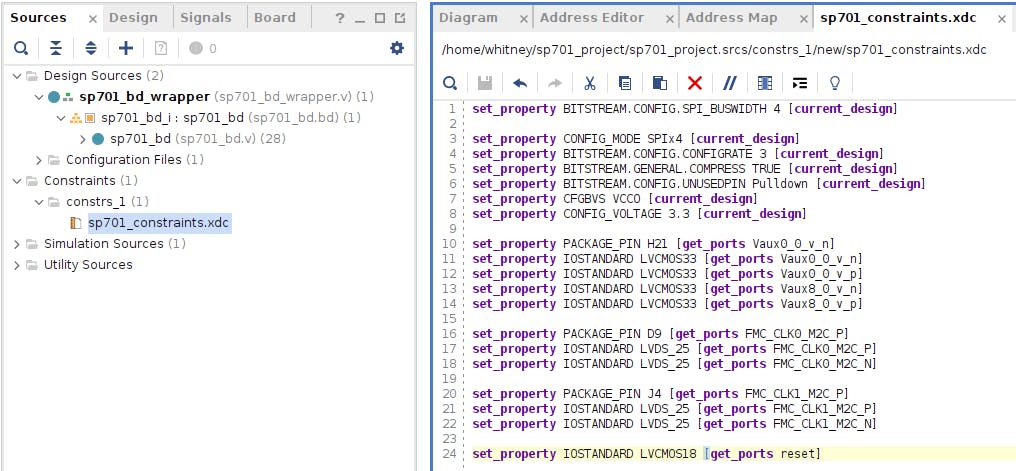

完成模块设计和顶层封装文件后,要添加的最后一项是指定到 Spartan-7 FPGA 封装引脚的信号路由的约束文件。

从Flow Navigator窗口中选择添加源。选择添加或创建约束选项,并在项目本地创建一个新的约束文件。

为 SP701 评估板添加以下约束:

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 3 [current_design]

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.UNUSEDPIN Pulldown [current_design]

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property PACKAGE_PIN H21 [get_ports Vaux0_0_v_n]

set_property IOSTANDARD LVCMOS33 [get_ports Vaux0_0_v_n]

set_property IOSTANDARD LVCMOS33 [get_ports Vaux0_0_v_p]

set_property IOSTANDARD LVCMOS33 [get_ports Vaux8_0_v_n]

set_property IOSTANDARD LVCMOS33 [get_ports Vaux8_0_v_p]

set_property PACKAGE_PIN D9 [get_ports FMC_CLK0_M2C_P]

set_property IOSTANDARD LVDS_25 [get_ports FMC_CLK0_M2C_P]

set_property IOSTANDARD LVDS_25 [get_ports FMC_CLK0_M2C_N]

set_property PACKAGE_PIN J4 [get_ports FMC_CLK1_M2C_P]

set_property IOSTANDARD LVDS_25 [get_ports FMC_CLK1_M2C_P]

set_property IOSTANDARD LVDS_25 [get_ports FMC_CLK1_M2C_N]

set_property IOSTANDARD LVCMOS18 [get_ports reset]

这些限制还包括 QSPI 闪存芯片的电路配置。

生成比特流

Vivado 遵循综合的标准 FPGA 开发流程,然后是布局布线(在 Vivado 中称为实现),最后是比特流生成。每个步骤都出现在 Flow Navigator 窗口中以手动运行。值得注意的是,如果您尝试在综合之前运行实现,Vivado 将在启动实现运行之前自动执行综合运行。

我在 Vivado 2021.x 版本中发现了一个有趣的怪癖,有时(但并非总是)如果您单独运行每个步骤(即您手动单击“运行综合”、“运行实现”和“生成比特流”,则会出现严重警告弹出说找不到目标FPGA的板定义文件。

这是一个完全“绒毛”的警告,对项目没有功能影响(板定义文件没有实际问题),但我觉得它非常烦人。幸运的是,有一个超级简单的解决方法,如果您始终选择“生成比特流”并让 Vivado 自动重新运行综合和实现,则永远不会弹出此严重警告。我只发现这可能发生在 Linux 上的 Vivado 2021.x 版本中,所以如果它没有出现在您面前,请忽略这个小插曲。

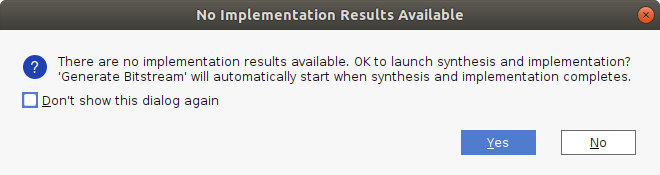

无论如何,由于我选择“生成比特流”之前没有进行综合或实现运行,Vivado 会通知我并要求继续:

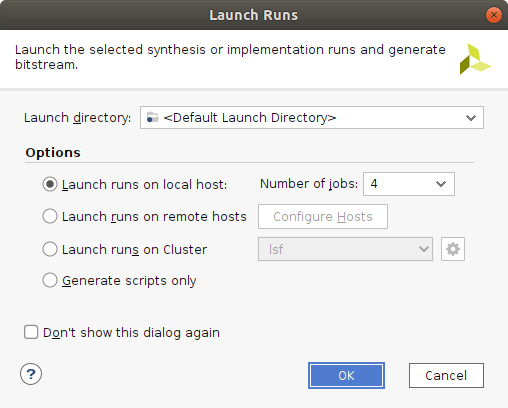

单击“是”后,Vivado 将为我提供一些关于如何利用主机 PC 资源的选项。我通常总是将这些选项设置为默认值。

我有一个带有 32GB RAM 的 Intel i9 处理器,从开始合成到完成此设计的比特流生成大约需要 10 分钟。

出口硬件

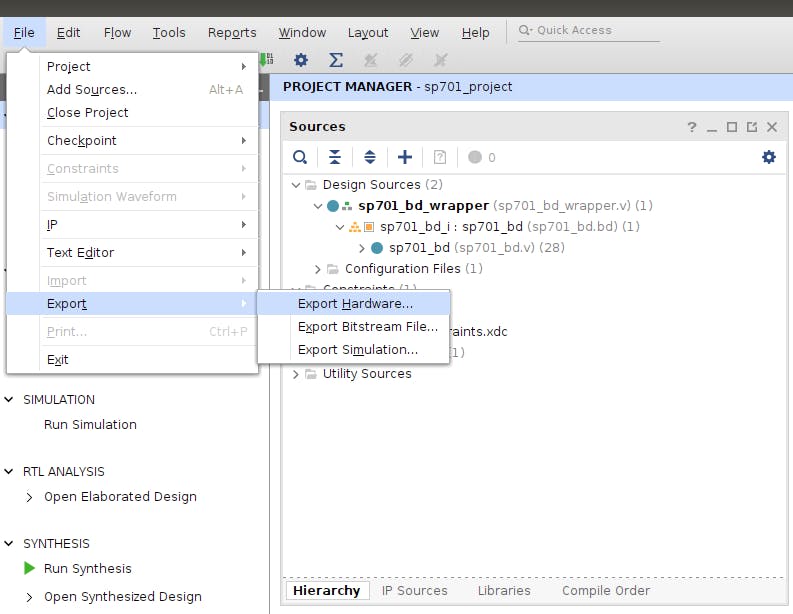

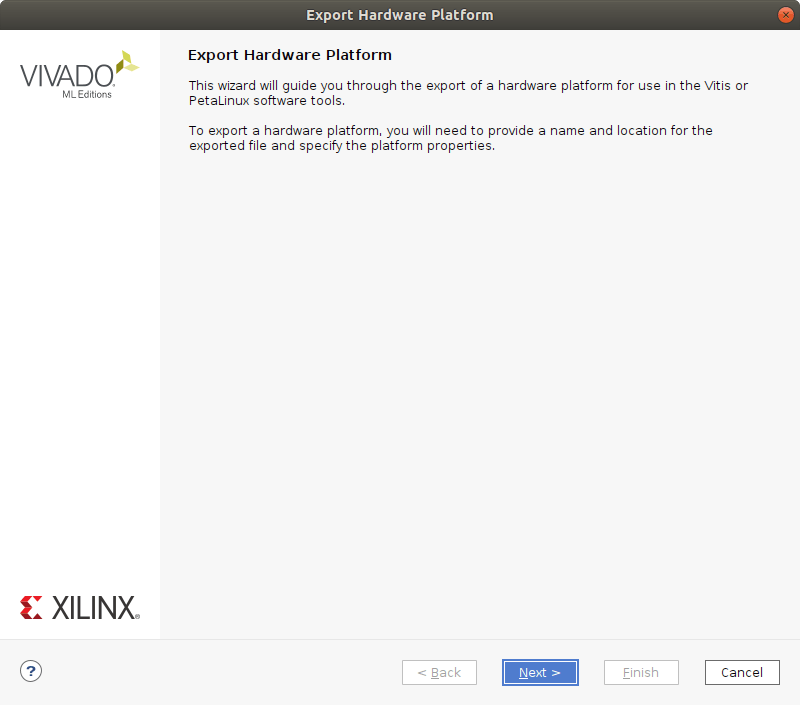

成功生成比特流后,需要导出硬件平台以在 Vitis 和/或 PetaLinux 中使用,以便在 MicroBlaze 软处理器上运行代码的软件开发。

选择文件>导出>导出硬件...

选择将比特流包含在导出的硬件平台中,然后选择所需的输出目录。

我个人喜欢将其导出到 Vivado 项目目录的顶层,以便将所有内容放在一个位置。

这就是 Vivado 中 SP701 硬件设计的全部内容。我将在这篇文章之后提供基于此硬件设计在 Vitis 中创建 lwIP 回显服务器的指南。

- SP701评估套件快速入门指南 0次下载

- SP701评估板用户指南 0次下载

- SP701上的lwIP入门 0次下载

- OMAP-L138+Spartan-6 FPGA开发板规格书

- AXU2CG FPGA XLINX开发板底板原理图 26次下载

- 黑金Spartan6开发板的Verilog教程详细说明 63次下载

- Spartan-6 FPGA的配置教程说明 25次下载

- Xilinx FPGA开发板SP605的电路原理图免费下载 23次下载

- xinlinx-Spartan6开发板原理图 81次下载

- Artix-7 FPGA AC701开发板-板载Debug Checklist 100次下载

- 基于Spartan3火龙刀系列FPGA开发板制作的VGA实验例程 8次下载

- Xilinx SPARTAN-3E入门开发板实例 43次下载

- spartan 3E 开发板的安装指导 8次下载

- Spartan-3E 原理图和入门套件 10次下载

- IDS1-XC3S400开发板用户手册 47次下载

- fpga开发板是什么?fpga开发板有哪些? 566次阅读

- fpga开发板使用教程 111次阅读

- fpga开发板与linux开发板区别 388次阅读

- FPGA学习入门从点灯开始 199次阅读

- 如何使用代码控制开发板 3048次阅读

- 微雪电子FPGAXILINX XC3S250E开发板简介 2807次阅读

- digilentSpartan-7开源创客开发板介绍 2874次阅读

- digilent Spartan-3E FPGA训练板介绍 2399次阅读

- digilent Spartan-3E起步板介绍 2929次阅读

- 星翼电子:新起点FPGA开发板硬件资源描述 3473次阅读

- Scarab Hardware公司的mini Spartan6+开发板介绍 3505次阅读

- 新手入门应如何选择ARM开发板_选择开发板的注意事项 4.2w次阅读

- 经验分享:如何选购FPGA开发板 5322次阅读

- FPGA开发板使用和配置方式 6207次阅读

- Spartan-6 FPGA 的 ISE 工具快速入门视频 6724次阅读

下载排行

本周

- 1山景DSP芯片AP8248A2数据手册

- 1.06 MB | 532次下载 | 免费

- 2RK3399完整板原理图(支持平板,盒子VR)

- 3.28 MB | 339次下载 | 免费

- 3TC358743XBG评估板参考手册

- 1.36 MB | 330次下载 | 免费

- 4DFM软件使用教程

- 0.84 MB | 295次下载 | 免费

- 5元宇宙深度解析—未来的未来-风口还是泡沫

- 6.40 MB | 227次下载 | 免费

- 6迪文DGUS开发指南

- 31.67 MB | 194次下载 | 免费

- 7元宇宙底层硬件系列报告

- 13.42 MB | 182次下载 | 免费

- 8FP5207XR-G1中文应用手册

- 1.09 MB | 178次下载 | 免费

本月

- 1OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 2555集成电路应用800例(新编版)

- 0.00 MB | 33566次下载 | 免费

- 3接口电路图大全

- 未知 | 30323次下载 | 免费

- 4开关电源设计实例指南

- 未知 | 21549次下载 | 免费

- 5电气工程师手册免费下载(新编第二版pdf电子书)

- 0.00 MB | 15349次下载 | 免费

- 6数字电路基础pdf(下载)

- 未知 | 13750次下载 | 免费

- 7电子制作实例集锦 下载

- 未知 | 8113次下载 | 免费

- 8《LED驱动电路设计》 温德尔著

- 0.00 MB | 6656次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935054次下载 | 免费

- 2protel99se软件下载(可英文版转中文版)

- 78.1 MB | 537798次下载 | 免费

- 3MATLAB 7.1 下载 (含软件介绍)

- 未知 | 420027次下载 | 免费

- 4OrCAD10.5下载OrCAD10.5中文版软件

- 0.00 MB | 234315次下载 | 免费

- 5Altium DXP2002下载入口

- 未知 | 233046次下载 | 免费

- 6电路仿真软件multisim 10.0免费下载

- 340992 | 191187次下载 | 免费

- 7十天学会AVR单片机与C语言视频教程 下载

- 158M | 183279次下载 | 免费

- 8proe5.0野火版下载(中文版免费下载)

- 未知 | 138040次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论