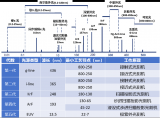

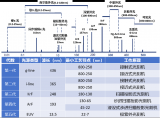

光刻机经历了5代产品发展,每次改进和创新都显著提升了光刻机所能实现的最小工艺节点。按照使用光源依次从g-line、i-line发展到KrF、ArF和EUV;按照工作原理依次从接触接近式光刻机发展到浸没步进式投影光刻机和极紫外式光刻机。

2024-03-21 11:31:41 34

34

制造集成电路的大多数工艺区域要求100级(空气中每立方米内直径大于等于0.5μm的尘埃粒子总数不超过约3500)洁净室,在光刻区域,洁净室要求10级或更高。

2024-03-20 12:36:00 54

54

是德科技与Intel Foundry的这次合作,无疑在半导体和集成电路设计领域引起了广泛的关注。双方成功验证了支持Intel 18A工艺技术的电磁仿真软件,为设计工程师们提供了更加先进和高效的设计工具。

2024-03-08 10:30:37 274

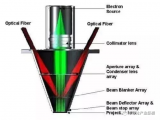

274 UMS的CHA3688aQDG是款三级自偏置宽带单片低噪声放大器单片电路。

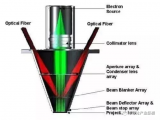

CHA3688aQDG选用 pHEMT 工艺技术、0.25μm 栅极尺寸、横穿基板的通孔、空气桥和电子束栅极光刻工艺生产

2024-03-06 15:46:20

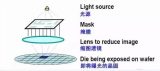

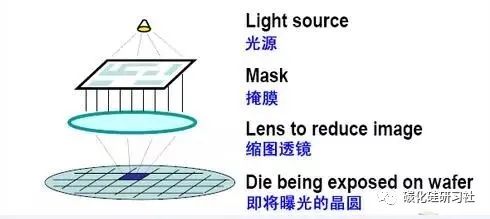

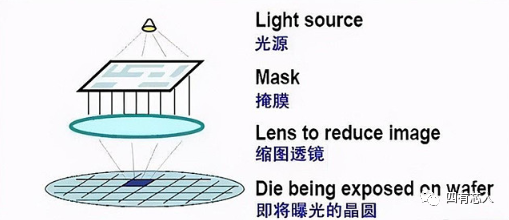

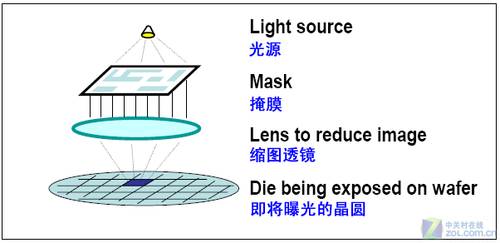

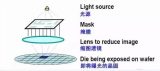

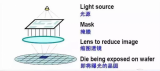

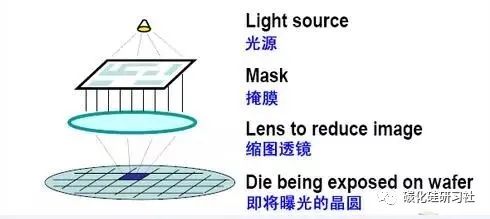

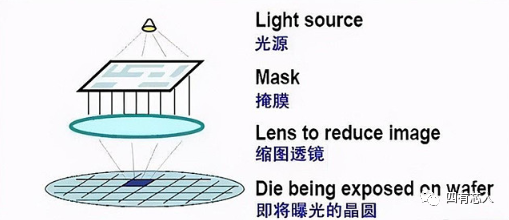

利用光刻机发出的光通过具有图形的光罩对涂有光刻胶的薄片曝光,光刻胶见光后会发生性质变化,从而使光罩上得图形复印到薄片上,从而使薄片具有电子线路图的作用。

2024-03-06 14:28:50 62

62

设计工程师现在可以使用 RFPro 对 Intel 18A 半导体工艺技术中的电路进行电磁仿真

2024-02-27 14:29:15 133

133 梯队的厂商们还在成熟工艺上稳扎稳打。 早在两年前,我们还会将28nm视作成熟工艺以及先进工艺的分水岭。但随着3nm的推出,以及即将到来的2nm,成熟工艺的定义已经发生了变化,分水岭已然换成了T2和T3晶圆厂不愿投入的7nm/8nm工艺

2024-02-21 00:17:00 2598

2598

在熊本县菊阳町,台积电、索尼和日本电装联合开发了一个12英寸晶圆加工基地,该基地应用12nm、16nm和22nm至28nm技术,预计月底建成。此外,其量产时间已定为2024年第四期。

2024-01-30 09:38:35 332

332 目前,台积电已完成与日本的一项联合建设晶圆厂协议,预计在今年2月24日举行投产庆典。日本的这处晶圆厂使用12nm、16nm、22nm及28nm等先进制程工艺,自启动以来进展顺利,引来业界广泛关注。

2024-01-29 14:00:42 178

178 例如,尽管iPhone 15 Pro已发布四个月,A17 Pro仍在使用台积电专有的3nm工艺。根据MacRumors的报告,这一趋势似乎仍将延续至2nm工艺。

2024-01-26 09:48:34 202

202 这座晶圆厂于2022年4月开始新建,大楼主结构已完工,且办公室部分区域也在今年8月启用。将生产N28 28nm级工艺芯片,这是日本目前最先进的半导体工艺。22ULP工艺也会在这里生产,但注意它不是22nm,而是28nm的一个变种,专用于超低功耗设备。

2024-01-03 15:53:27 433

433 据悉,2024年台积电的第二代3nm工艺(称为N3E)有望得到更广泛运用。此前只有苹果有能力订购第一代N3B高端晶圆。经过解决工艺难题及提升产量后,台积电推出经济实惠的3nm版型,吸引更多企业采用。

2024-01-03 14:15:17 279

279 用光作为画笔在微纳米世界中作画。

2023-12-28 16:00:08 169

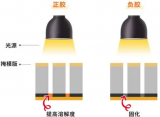

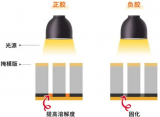

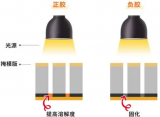

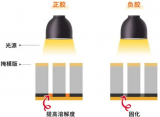

169 所谓的“光刻胶”,即是在紫外线、电子束等辐射下,其溶解度会产生变化的耐腐蚀薄膜材料。作为光刻工艺中的关键要素,广泛应用于晶圆和分立器件的精细图案制作中。其品种繁多,此次涨价涉及的KrF 光刻胶则属高级别光刻胶,将成为各厂商关注的焦点。

2023-12-28 11:14:34 379

379 掩模版(Photomask)又称光罩、光掩模、光刻掩模版、掩膜版、掩膜板等,是光刻工艺中关键部件之一,是下游行业产品制造过程中的图形“底片”转移用的高精密工具

2023-12-25 11:41:13 5385

5385

英特尔的Intel 20A和Intel 18A工艺已经开始流片,意味着量产阶段已经不远。而2nm工艺和1.8nm工艺的先进程度无疑已经超过了三星和台积电的3nm工艺。

2023-12-20 17:28:52 799

799 光照条件的设置、掩模版设计以及光刻胶工艺等因素对分辨率的影响都反映在k₁因子中,k₁因子也常被用于评估光刻工艺的难度,ASML认为其物理极限在0.25,k₁体现了各家晶圆厂运用光刻技术的水平。

2023-12-18 10:53:05 326

326

芯片的7nm工艺我们经常能听到,但是7nm是否真的意味着芯片的尺寸只有7nm呢?让我们一起来看看吧!

2023-12-07 11:45:31 1591

1591

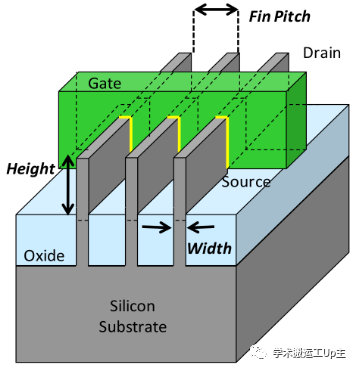

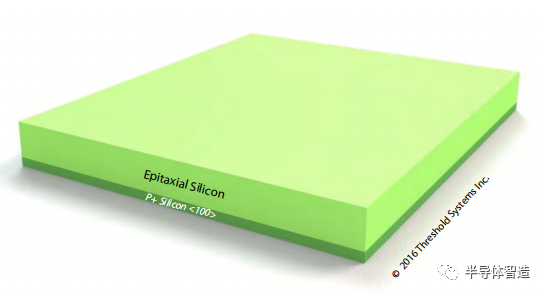

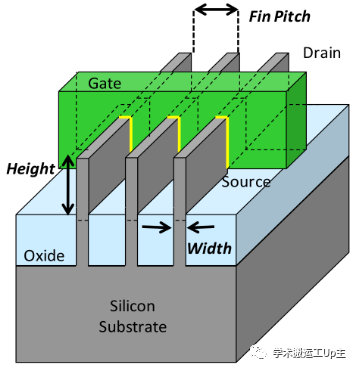

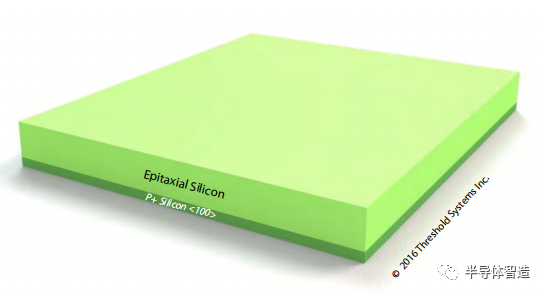

引入不同的气态化学物质进行的,这些化学物质通过与基材反应来改变表面。IC最小特征的形成被称为前端制造工艺(FEOL),本文将集中简要介绍这部分,将按照如下图所示的 22 nm 技术节点制造 FinFET 的工艺流程,解释了 FEOL 制造过程中最重要的工艺步骤。

2023-12-06 18:17:33 1122

1122

另外一种工艺方法是整个板子上都镀铜,感光膜以外的部分仅仅是锡或铅锡抗蚀层。这种工艺称为“全板镀铜工艺“。与图形电镀相比,全板镀铜的缺点是板面各处都要镀两次铜而且蚀刻时还必须都把它们腐蚀掉。

2023-12-06 15:03:45 260

260 W刻蚀工艺中使用SF6作为主刻步气体,并通过加入N2以增加对光刻胶的选择比,加入O2减少碳沉积。在W回刻工艺中分为两步,第一步是快速均匀地刻掉大部分W,第二步则降低刻蚀速率减弱负载效应,避免产生凹坑,并使用对TiN有高选择比的化学气体进行刻蚀。

2023-12-06 09:38:53 1527

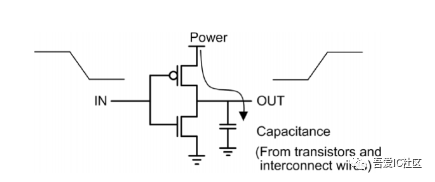

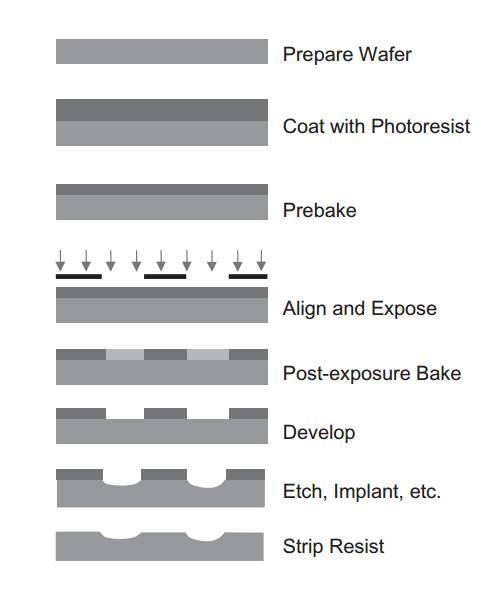

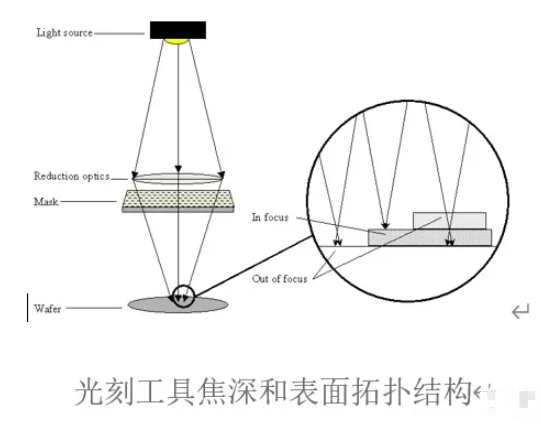

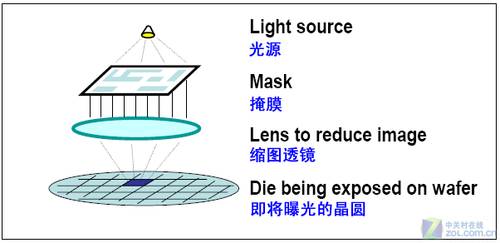

1527 光刻工艺就是把芯片制作所需要的线路与功能做出来。利用光刻机发出的光通过具有图形的光罩对涂有光刻胶的薄片曝光,光刻胶见光后会发生性质变化,从而使光罩上得图形复印到薄片上,从而使薄片具有电子线路图的作用

2023-12-04 09:17:24 1334

1334

[半导体前端工艺:第三篇] 光刻——半导体电路的绘制

2023-11-29 11:25:52 242

242

KrF光刻胶是指利用248nm KrF光源进行光刻的光刻胶。248nmKrF光刻技术已广 泛应用于0.13μm工艺的生产中,主要应用于150 , 200和300mm的硅晶圆生产中。

2023-11-29 10:28:50 283

283

今天分享另一篇网上流传很广的22nm 平面 process flow. 有兴趣的可以与上一篇22nm gate last FinFET process flow 进行对比学习。 言归正传,接下来介绍平面工艺最后一个节点22nm process flow。

2023-11-28 10:45:51 4232

4232

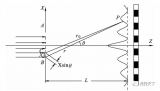

在超大规模集成电路中,为了实现NA=1.35,波长193nm处分辨率达到 45nm的目标,需要对影响光刻照明均匀性的误差源进行详细分析最终确定公差范围。

2023-11-27 10:35:51 385

385

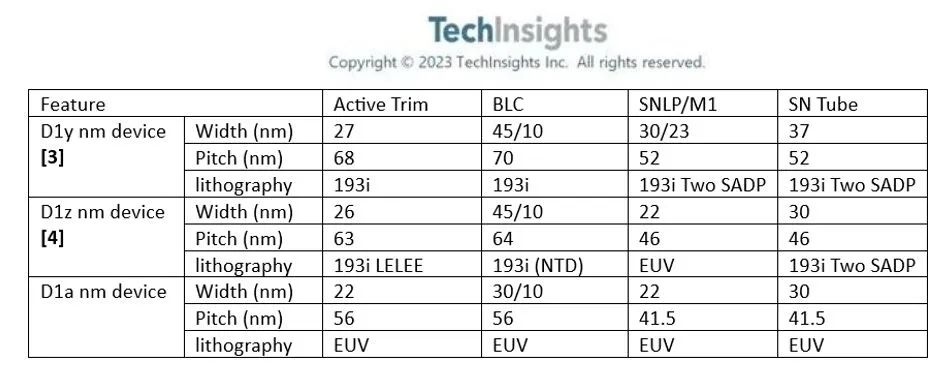

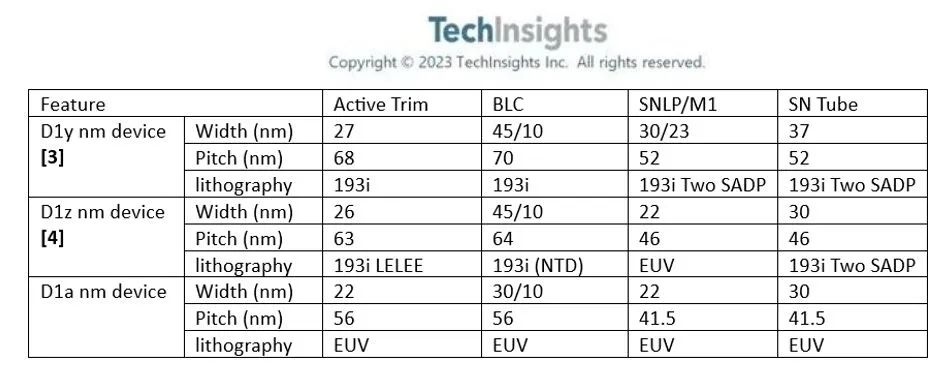

三星D1a nm LPDDR5X器件的EUV光刻工艺

2023-11-23 18:13:02 579

579

前两代M1和M2系列芯片均采用5nm制程工艺,而M3系列芯片的发布,标志着苹果Mac电脑正式进入3nm时代。 3nm利用先进的EUV(极紫外光刻)技术,可制造极小的晶体管,一根头发的横截面就能容纳两百万个晶体管。苹果用这些晶体管来优化新款芯片的每个组件。

2023-11-07 12:39:13 310

310

Bumping工艺是一种先进的封装工艺,而Sputter是Bumping工艺的第一道工序,其重要程度可想而知。Sputter的膜厚直接影响Bumping的质量,所以必须控制好Sputter的膜厚及均匀性是非常关键。

2023-10-23 11:18:18 475

475

FinFET立体晶体管技术是Intel 22nm率先引用的,这些年一直是半导体制造工艺的根基,接下来在Intel 20A、台积电2nm、三星3nm上,都将转向全环绕立体栅极晶体管。

2023-10-23 11:15:08 279

279

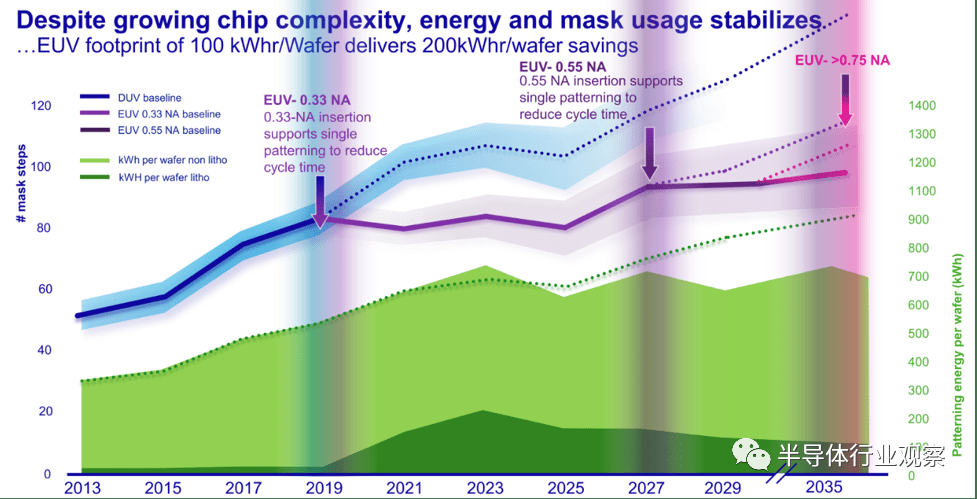

当制程节点演进到5nm时,DUV和多重曝光技术的组合也难以满足量产需求了,EUV光刻机就成为前道工序的必需品了,没有它,很难制造出符合应用需求的5nm芯片,即使不用EUV能制造出一些5nm芯片,其整个生产线的良率也非常低,无法形成大规模的商业化生产。

2023-10-13 14:45:03 834

834

光刻胶作为影响光刻效果核心要素之一,是电子产业的关键材料。光刻胶由溶剂、光引发剂和成膜树脂三种主要成分组成,是一种具有光化学敏感性的混合液体。其利用光化学反应,经曝光、显影等光刻工艺,将所需要的微细图形从掩模版转移到待加工基片上,是用于微细加工技术的关键性电子化学品。

2023-10-09 14:34:49 1671

1671

,一板多用,满足多方位的开发需求。

盘古22K开发板详情

盘古22K开发板(MES22GP)是基于紫光同创40nm工艺的Logos系列PGL22G芯片的一套全新的国产FPGA开发套件。开发板电源采用

2023-09-21 18:16:52

的大部分时间里,用于制造芯片的工艺节点的名称是由晶体管栅极长度的最小特征尺寸(以纳米为单位)或最小线宽来指定的。350nm工艺节点就是一个例子。

2023-09-19 15:48:43 4475

4475

一站式PCBA智造厂家今天为大家讲讲pcb打样蚀刻工艺注意事项有哪些?PCB打样蚀刻工艺注意事项。PCB打样中,在铜箔部分预镀一层铅锡防腐层,保留在板外层,即电路的图形部分,然后是其余的铜箔被化学方法腐蚀,称为蚀刻。

2023-09-18 11:06:30 669

669 的架构,常见的有x86和x64。

指令集:如SSE、AVX等,用于拓展CPU的功能。

微架构:如NetBurst、K10等,表示CPU内部的具体实现。

制造工艺:如22nm、14nm等,表示CPU制造过程中的最小尺寸。

查看CPU处理器参数可以通过Intel官网或CPU-Z等工具实现。

2023-09-05 16:42:49

半导体制造工艺之光刻工艺详解

2023-08-24 10:38:54 1221

1221

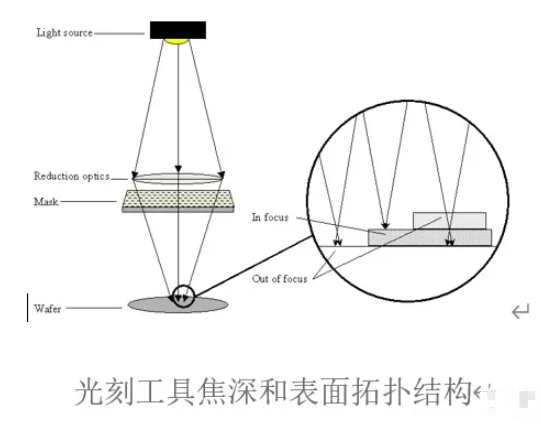

光刻是半导体芯片生产流程中最复杂、最关键的工艺步骤,耗时长、成本高。半导体芯片生产的难点和关键点在于将电路图从掩模上转移至硅片上,这一过程通过光刻来实现, 光刻的工艺水平直接决定芯片的制程水平和性能水平。

2023-08-23 10:47:53 1573

1573

个 GPU 核心 @ 750mhz 14nm工艺节点 GPU 产生 187.2 GFLOPs 配备 2x4GB 内存,处理器已有 7 年历史,但核心功能运行情况相对良好。 MGU22H 使用 Snapdragon SA8155P 和 2x8GB Micron LPDDR4 RAM

2023-08-21 11:42:03 769

769

在半导体制程中,移除残余材料的“减法工艺”不止“刻蚀”一种,引入其他材料的“加法工艺”也非“沉积”一种。比如,光刻工艺中的光刻胶涂敷,其实也是在基底上形成各种薄膜;又如氧化工艺中晶圆(硅)氧化,也需要在基底表面添加各种新材料。那为什么唯独要强调“沉积”工艺呢?

2023-08-17 15:33:27 370

370

PCB蚀刻工艺中的“水池效应”现象,通常发生在顶部,这种现象会导致大尺寸PCB整个板面具有不同的蚀刻质量。

2023-08-10 18:25:43 1012

1012 根据外媒报道,据称台积电新的3nm制造工艺的次品率约为30%。不过根据独家条款,该公司仅向苹果收取良品芯片的费用!

2023-08-08 15:59:27 780

780 光刻是一种图像复制技术,是集成电路工艺中至关重要的一项工艺。简单地说,光刻类似照相复制方法,即将掩膜版上的图形精确地复制到涂在硅片表面的光刻胶或其他掩蔽膜上面,然后在光刻胶或其他掩蔽膜的保护下对硅片进行离子注入、刻蚀、金属蒸镀等。

2023-08-07 17:52:53 1478

1478

无论是14nm还是10nm,Intel这些年的新工艺都有一个通性:刚诞生的时候性能平平,高频率都上不去,只能用于笔记本移动端(分别对应5代酷睿、10代酷睿),后期才不断成熟,比如到了13代酷睿就达到史无前例的6GHz。

2023-08-07 09:55:57 734

734

Intel将在下半年发布的Meteor Lake酷睿Ultra处理器将首次使用Intel 4制造工艺,也就是之前的7nm,但是Intel认为它能达到4nm级别的水平,所以改了名字。

2023-08-01 09:41:50 561

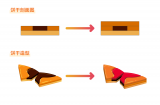

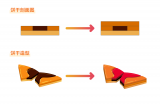

561 当谈到该创新工艺时,不可避免地要与传统的光刻工艺体系进行对比。光刻工艺体系是一种减法工艺:首先要在衬底表面沉积一层材料,例如铜;然后在材料层表面涂布一层光刻胶;接着将光刻胶图形化曝光并显影,形成有图案的光刻覆盖区域

2023-07-29 11:01:50 835

835

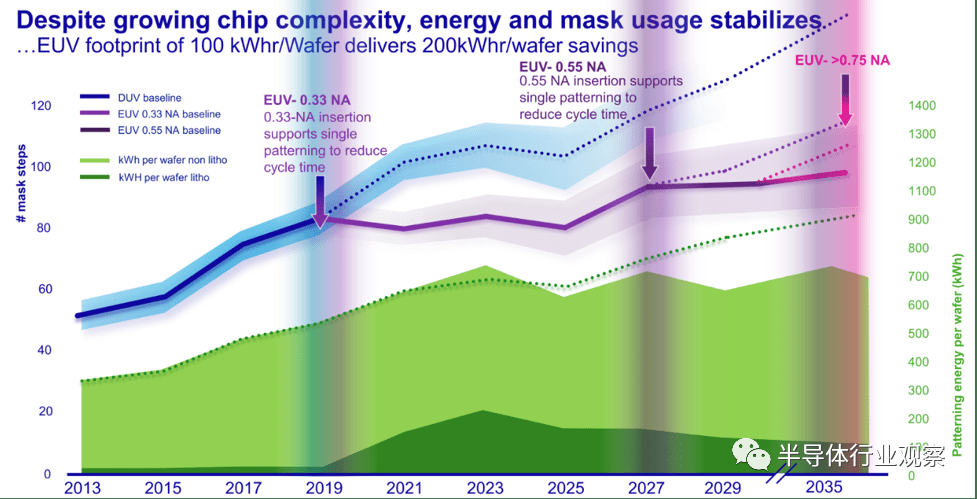

半导体技术的未来通常是通过光刻设备的镜头来看待的,尽管高度挑战性的技术问题几乎永无休止,但光刻设备仍继续为未来的工艺节点提供更好的分辨率。

2023-07-28 17:41:16 1130

1130

近几年,芯片产业越来越火热,一些行业内的术语大家也听得比较多了。那么工艺节点、制程是什么,"7nm" 、"5nm"又是指什么?

2023-07-28 17:34:33 5639

5639

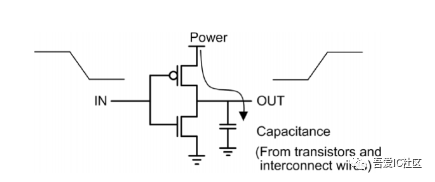

金属-氧化物半导体场效应晶体管(MOSFET)的革命,让我们可以在相同面积的晶圆上同时制造出更多晶体管。

2023-07-27 15:24:51 609

609

RK3568四核64位Cortex-A55处理器,采用全新ARM v8.2-A架构主频最高可达2.0GHz,效能有大幅提升;采用22nm先进工艺,具有低功耗高性能的特点

2023-07-18 09:47:29 511

511

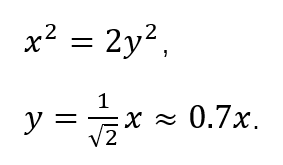

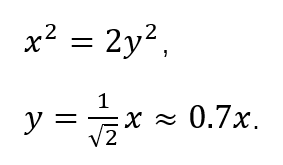

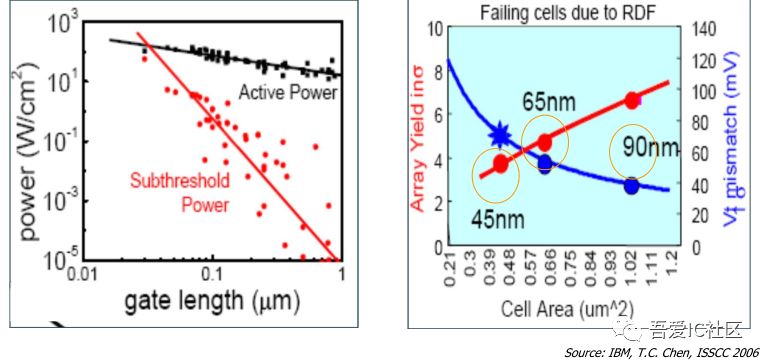

泄漏功率仍然是HKMG(High-K Metal Gate)一个主要问题。从下图看出,在28nm的High-K Metal Gate Stack中,leakage power仍然在总功耗中占据主导地位。

2023-07-12 16:24:23 2882

2882

RK3568是瑞芯微出品的一款定位中高端的通用型SoC,采用22nm先进制程工艺,集成4核 arm 架构 A55 处理器和 Mali G52 2EE 图形处理器,支持4K解码和1080P编码。

2023-07-07 17:35:32 704

704

GK-1000光刻掩膜版测温仪,光刻机曝光光学系统测温仪光刻机是一种用于微纳米加工的设备,主要用于制造集成电路、光电子器件、MEMS(微机电系统)等微细结构。光刻机是一种光学投影技术,通过将光线通过

2023-07-07 11:46:07

外,学生还就感兴趣的课题做深入调研。师生共同讨论调研报告,实现教学互动。调研的内容涉及光刻工艺、光刻成像理论、SMO、OPC和DTCO技术。

2023-06-30 10:06:02 261

261

在半导体制程中,移除残余材料的“减法工艺”不止“刻蚀”一种,引入其他材料的“加法工艺”也非“沉积”一种。比如,光刻工艺中的光刻胶涂敷,其实也是在基底上形成各种薄膜;又如氧化工艺中晶圆(硅)氧化,也需要在基底表面添加各种新材料。那为什么唯独要强调“沉积”工艺呢?

2023-06-29 16:58:37 404

404

随着工艺节点的不断发展(现在普遍是28nm,22nm,16nm,14nm,甚至有的都在做7nm),芯片的性能需求越来越高,规模也越来越大

2023-06-29 15:24:11 1741

1741

外,学生还就感兴趣的课题做深入调研。师生共同讨论调研报告,实现教学互动。调研的内容涉及光刻工艺、光刻成像理论、SMO、OPC和DTCO技术。

2023-06-29 10:02:17 327

327

分别为18.46%、14.49%、18.66%。在制程方面,安凯微主流产品采用40nm 和 22nm 工艺制程,且已经开始12nm FinFET 工艺设计的研发工作。

2023-06-28 15:55:19 828

828

开箱大吉#紫光同创PGL22G关键特性评估板@盘古22K开发板 开箱教程来啦!详细教程手把手来教啦!#紫光盘古系列开发板@盘古22K开发板 基于紫光同创40nm工艺的FPGA主控芯片(Logos系列

2023-06-28 10:46:17

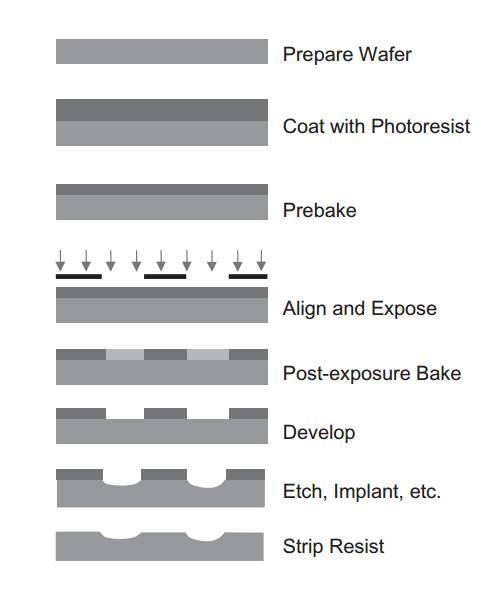

在之前的文章里,我们介绍了晶圆制造、氧化过程和集成电路的部分发展史。现在,让我们继续了解光刻工艺,通过该过程将电子电路图形转移到晶圆上。光刻过程与使用胶片相机拍照非常相似。但是具体是怎么实现的呢?

2023-06-28 10:07:47 2427

2427

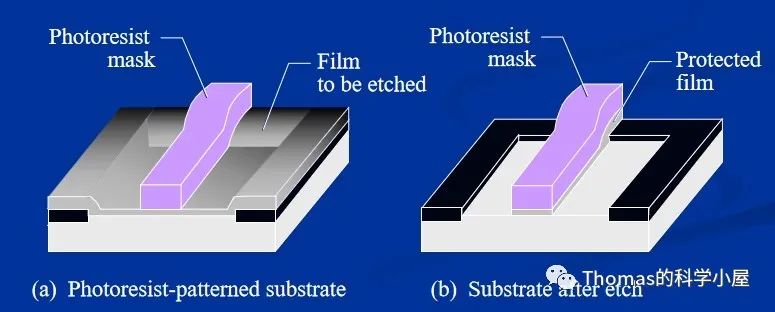

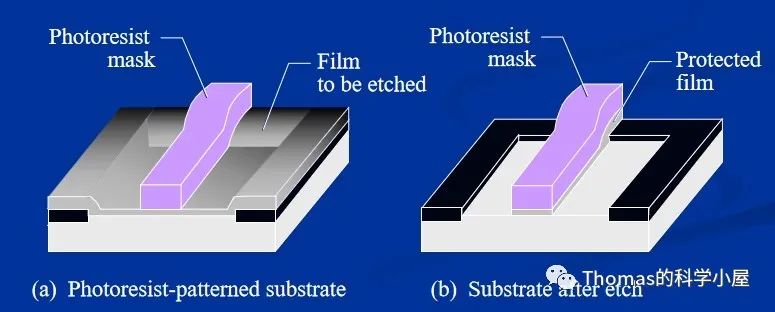

在上一篇文章,我们介绍了光刻工艺,即利用光罩(掩膜)把设计好的电路图形绘制在涂覆了光刻胶的晶圆表面上。下一步,将在晶圆上进行刻蚀工艺,以去除不必要的材料,只保留所需的图形。

2023-06-28 10:04:58 843

843

外,学生还就感兴趣的课题做深入调研。师生共同讨论调研报告,实现教学互动。调研的内容涉及光刻工艺、光刻成像理论、SMO、OPC和DTCO技术。

2023-06-26 17:00:19 765

765

如今,光刻技术已成为一项容错率极低的大产业。全球领先的荷兰公司 ASML 也是欧洲市值最大的科技公司。它的光刻工具依赖于世界上最平坦的镜子、最强大的商用激光器之一以及比太阳表面爆炸还高的热度,在硅上刻出微小的形状,尺寸仅为几纳米。

2023-06-26 16:59:16 569

569 Dimension, CD)小型化(2D视角),刻蚀工艺从湿法刻蚀转为干法刻蚀,因此所需的设备和工艺更加复杂。由于积极采用3D单元堆叠方法,刻蚀工艺的核心性能指数出现波动,从而刻蚀工艺与光刻工艺成为半导体制造的重要工艺流程之一。

2023-06-26 09:20:10 816

816

尽管英特尔的第14代酷睿尚未发布,但第15代酷睿(代号Arrow Lake)已经曝光。新的酷睿系列产品将改为酷睿Ultra系列,并使用台积电的3nm工艺,预计会有显著的性能提升。

2023-06-20 17:48:57 1100

1100 外,学生还就感兴趣的课题做深入调研。师生共同讨论调研报告,实现教学互动。调研的内容涉及光刻工艺、光刻成像理论、SMO、OPC和DTCO技术。

2023-06-20 10:51:43 335

335

近日,湖南大学段辉高教授团队通过开发基于“光刻胶全干法转印”技术的新型光刻工艺,用于柔性及不规则(曲面、悬空)衬底上柔性电子器件的原位和高保形制造,为高精度、高可靠性和高稳定性柔性电子器件的制造提供

2023-06-17 10:19:38 507

507

跪求新唐NM1200和NM1330详细的数据手册

2023-06-15 08:57:31

外,学生还就感兴趣的课题做深入调研。师生共同讨论调研报告,实现教学互动。调研的内容涉及光刻工艺、光刻成像理论、SMO、OPC和DTCO技术。

2023-06-14 10:16:38 226

226

外,学生还就感兴趣的课题做深入调研。师生共同讨论调研报告,实现教学互动。调研的内容涉及光刻工艺、光刻成像理论、SMO、OPC和DTCO技术。 考虑到这些内容也是目前业界关注的实用技术,征得教师和学生的同意,本公众号将陆

2023-06-13 16:24:08 226

226

【视频】盘古Logos系列PGL22G关键特性评估板@盘古22K开发板#紫光同创FPGA开发板#基于紫光同创40nm工艺的FPGA主控芯片(Logos系列: PGL22G-MBG324),挂载

2023-06-12 17:38:43

外,学生还就感兴趣的课题做深入调研。师生共同讨论调研报告,实现教学互动。调研的内容涉及光刻工艺、光刻成像理论、SMO、OPC和DTCO技术。

2023-06-12 11:19:55 562

562

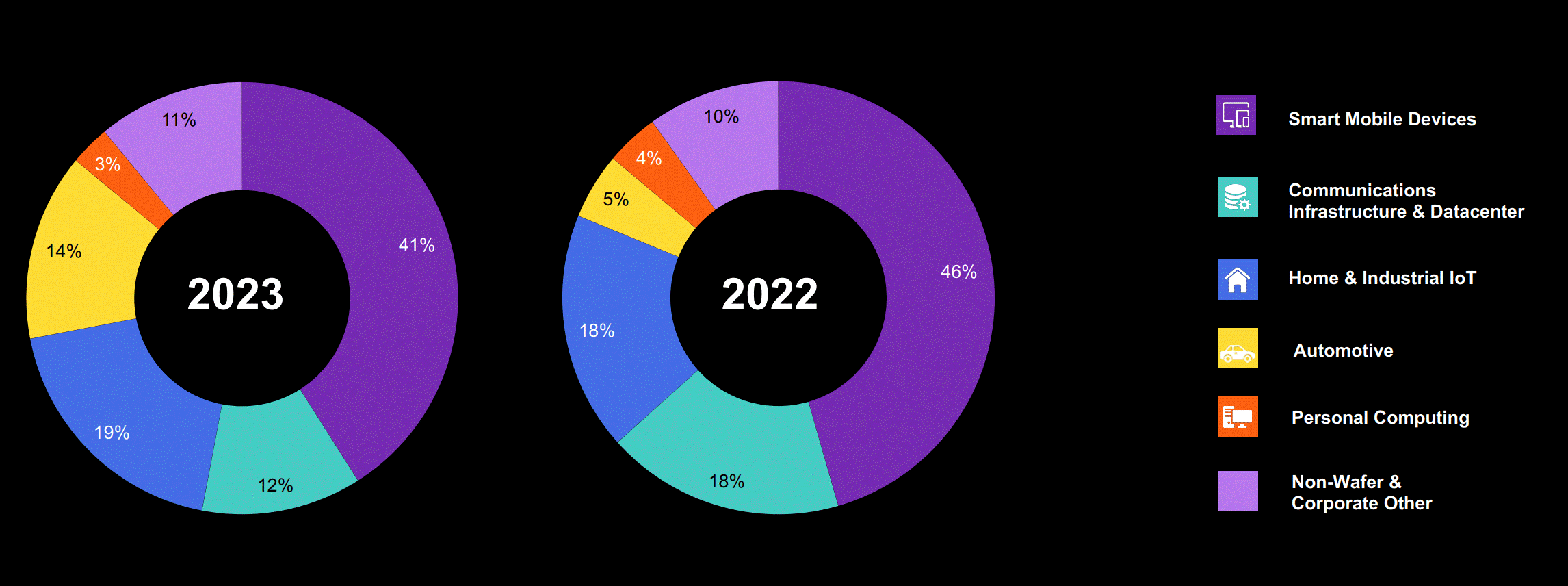

光刻机可分为前道光刻机和后道光刻机。光刻机既可以用在前道工艺,也可以用在后道工艺,前道光刻机用于芯片的制造,曝光工艺极其复杂,后道光刻机主要用于封装测试,实现高性能的先进封装,技术难度相对较小。

2023-06-09 10:49:20 5857

5857

光刻工艺后,在硅片或晶圆上形成了光刻胶的图形,下一步就是刻蚀。

2023-06-08 10:52:35 3304

3304

中芯国际,作为当前我国技术最为先进,工艺最为成熟的芯片半导体代工厂商,堪称是当下国内半导体行业“全村的希望”。尽管面临着技术的限制和先进光刻机设备的禁运,中芯国际却依然在自主研发与创新

2023-06-06 15:34:21 17913

17913 在探讨半导体行业时,我们经常会听到两个概念:晶圆尺寸和工艺节点。本文将为您解析8寸晶圆以及5nm工艺这两个重要的概念。

2023-06-06 10:44:00 1420

1420

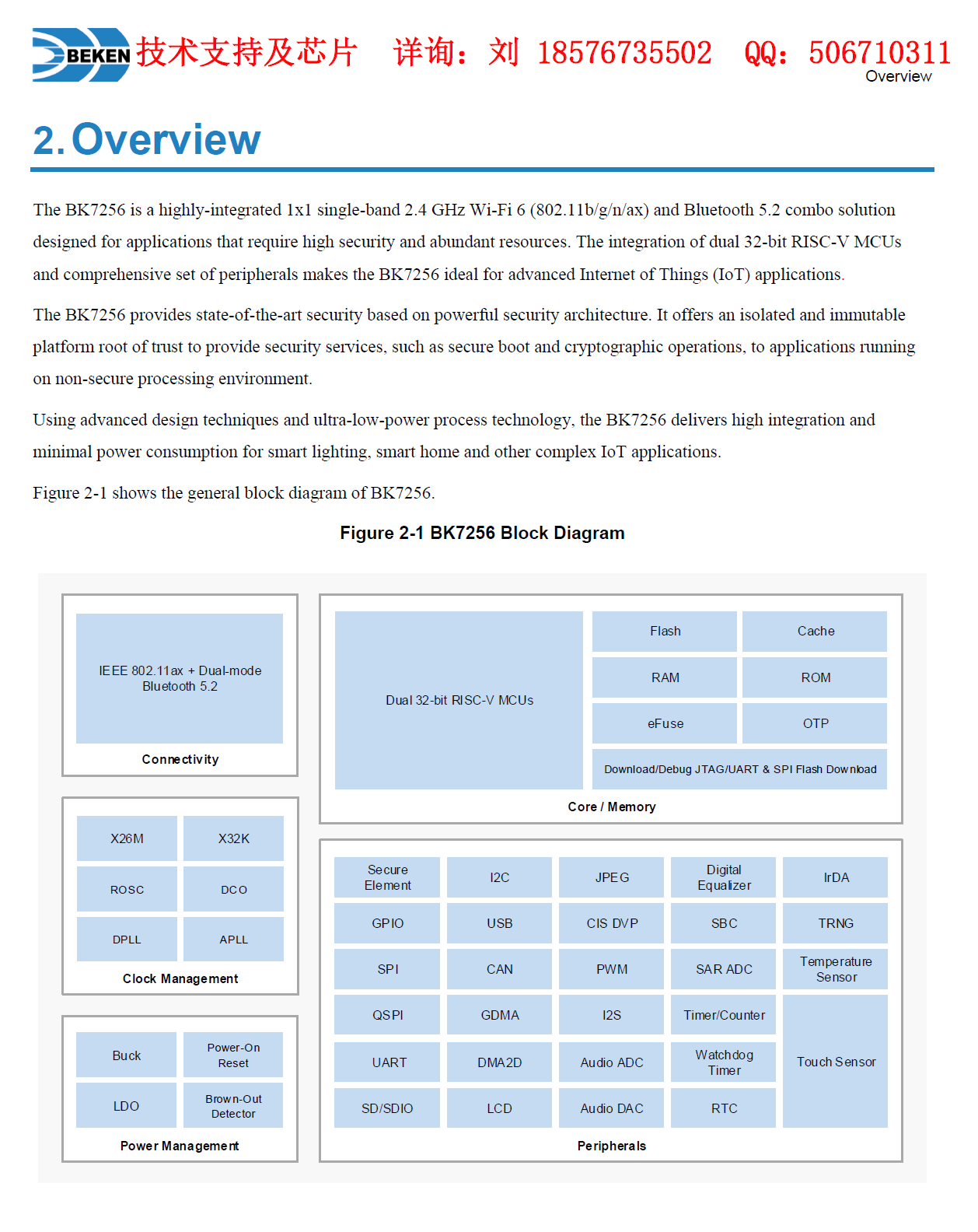

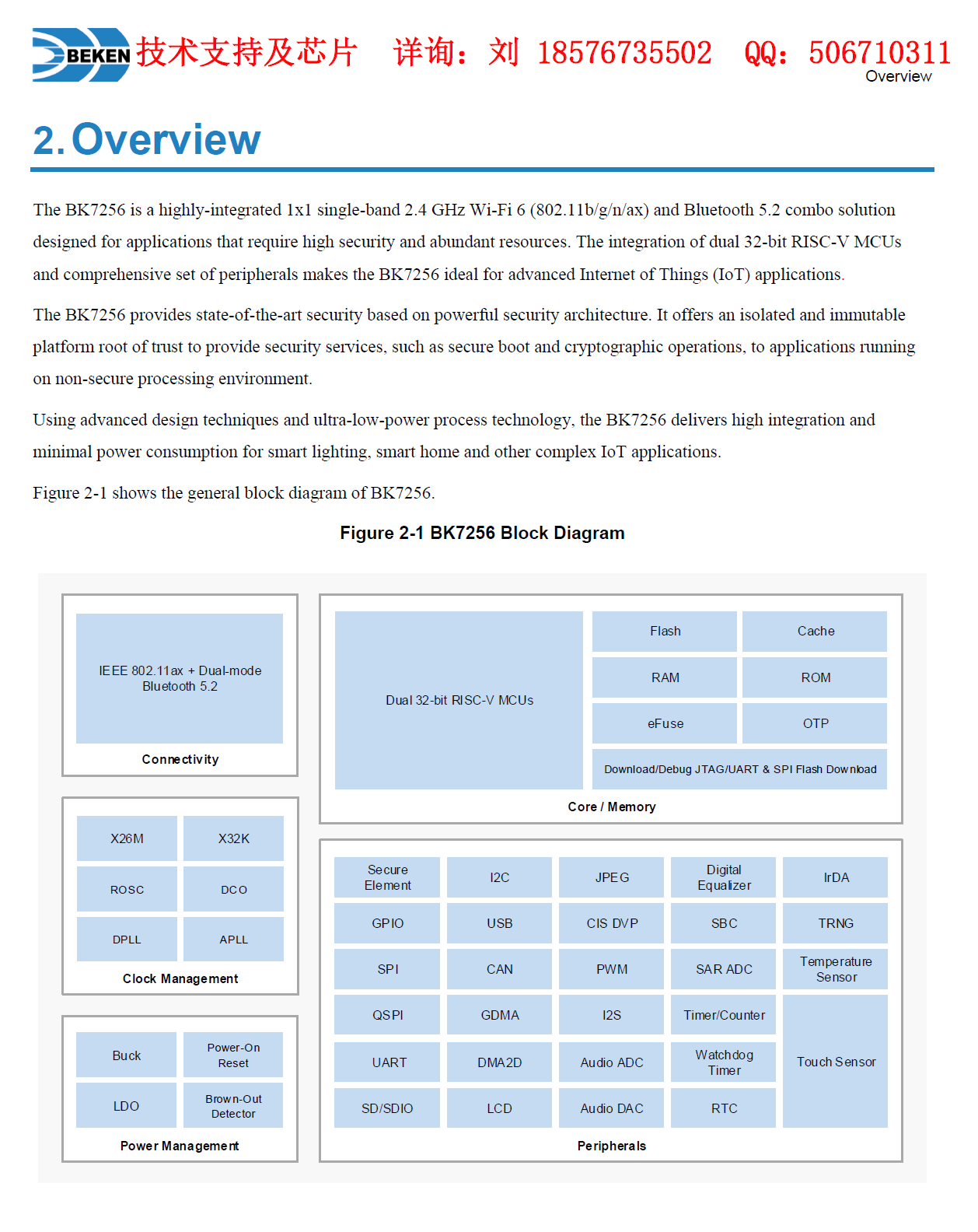

BK7256是一颗采用22nm工艺制程,高度集成wifi+ble的低功耗音视频芯片,可用于实时远程音视频传输和iot智能中控驱屏应用

2023-06-06 09:47:58 1572

1572

通常,光刻是作为特性良好的模块的一部分执行的,其中包括晶圆表面制备、光刻胶沉积、掩模和晶圆的对准、曝光、显影和适当的抗蚀剂调节。光刻工艺步骤需要按顺序进行表征,以确保模块末端剩余的抗蚀剂是掩模的最佳图像,并具有所需的侧壁轮廓。

2023-06-02 16:30:25 418

418

直接镀铜陶瓷基板(Direct Plating Copper, DPC)是在陶瓷薄膜工艺加工基础上发展起来的陶瓷电路加工工艺。以氮化铝/氧化铝陶瓷作为线路的基板,采用溅镀工艺于基板表面复合金属层,并以电镀和光刻工艺形成电路。

2023-05-31 10:32:02 1587

1587

瑞芯微RK3568芯片是一款定位中高端的通用型SOC,采用22nm制程工艺,搭载一颗四核Cortex-A55处理器和Mali G52 2EE 图形处理器。RK3568 支持4K 解码和 1080P

2023-05-29 11:09:01

14nm、10nm、4……Intel近几年的制造工艺,每次首秀都不太顺利,频率和性能不达标,只能用于移动版,优化个一两年才能上桌面,然后性能又非常好。

2023-05-24 11:33:42 985

985

处理器采用22nm工艺,主频高达2.0GHz;支持蓝牙、Wi-Fi、音频、视频和摄像头等功能,拥有丰富的扩展接口,支持多种视频输入输出接口,配置双千兆自适应RJ45以太网口,可满足NVR、工业网关等多网口

2023-05-16 14:56:42

光刻胶可以通过光化学反应,经曝光、显影等光刻工序将所需要的微细图形从光罩(掩模版)转移到待加工基片上。依据使用场景,这里的待加工基片可以是集成电路材料,显示面板材料或者印刷电路板。

2023-05-11 16:10:49 2772

2772

Intel将于6月11日至16日举办的VLSI Symposium 2023研讨会上,首次展示PowerVia技术。有关信息显示,Intel的20A工艺将引入PowerVia背部供电和RibbonFET全环绕栅极晶体管等全新技术。

2023-05-10 15:07:51 345

345

1300NM

金属封装工艺是指采用金属外壳作为封装壳体或底座,在其内部安装芯片或基板并进行键合连接,外引线通过金属-玻璃(或陶瓷)组装工艺穿过金属外壳,将内部元件的功能引出、外部电源信号等输人的一种电子

2023-05-09 11:23:07

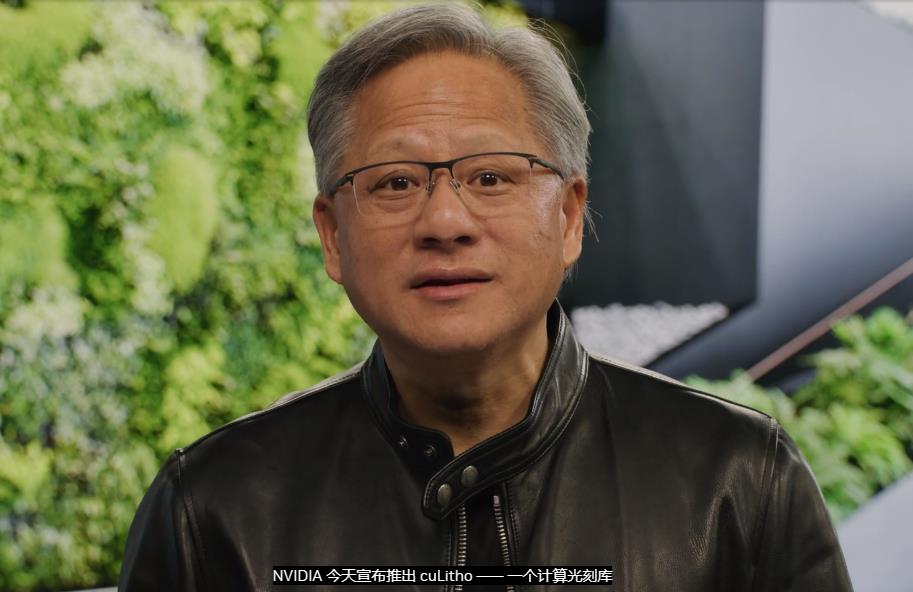

使用尖端工艺技术生产芯片需要比以往更强大的计算能力。为了满足2nm及更先进制程的需求,NVIDIA正在推出其cuLitho软件库

2023-04-26 10:06:52 595

595 现代工艺技术将晶圆厂设备要求推向极限,需要实现突破其物理极限的高分辨率,这正是计算光刻技术发挥作用的地方。计算光刻就是为芯片生产制作光掩模的技术,它结合来自ASML设备和测试晶圆的关键数据,是一个模拟生产过程的算法。

2023-04-26 10:05:29 918

918 根据维基百科的定义,光刻是半导体器件制造工艺中的一个重要步骤,该步骤利用曝光和显影在光刻胶层上刻画几何图形结构,然后通过刻蚀工艺将光掩模上的图形转移到所在衬底上。这里所说的衬底不仅包含硅晶圆,还可以是其他金属层、介质层,例如玻璃、SOS中的蓝宝石。

2023-04-25 11:11:33 1242

1242

光刻技术简单来讲,就是将掩膜版图形曝光至硅片的过程,是大规模集成电路的基础。目前市场上主流技术是193nm沉浸式光刻技术,CPU所谓30nm工艺或者22nm工艺指的就是采用该技术获得的电路尺寸。

2023-04-25 11:02:32 2261

2261

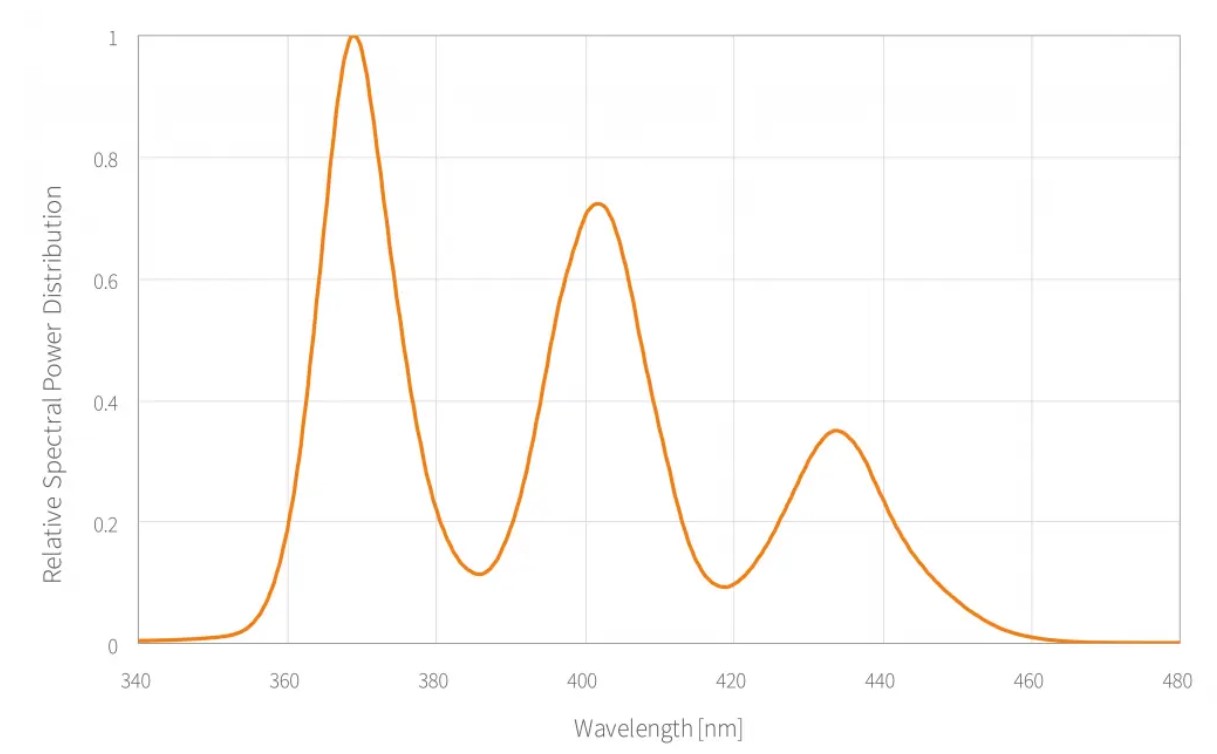

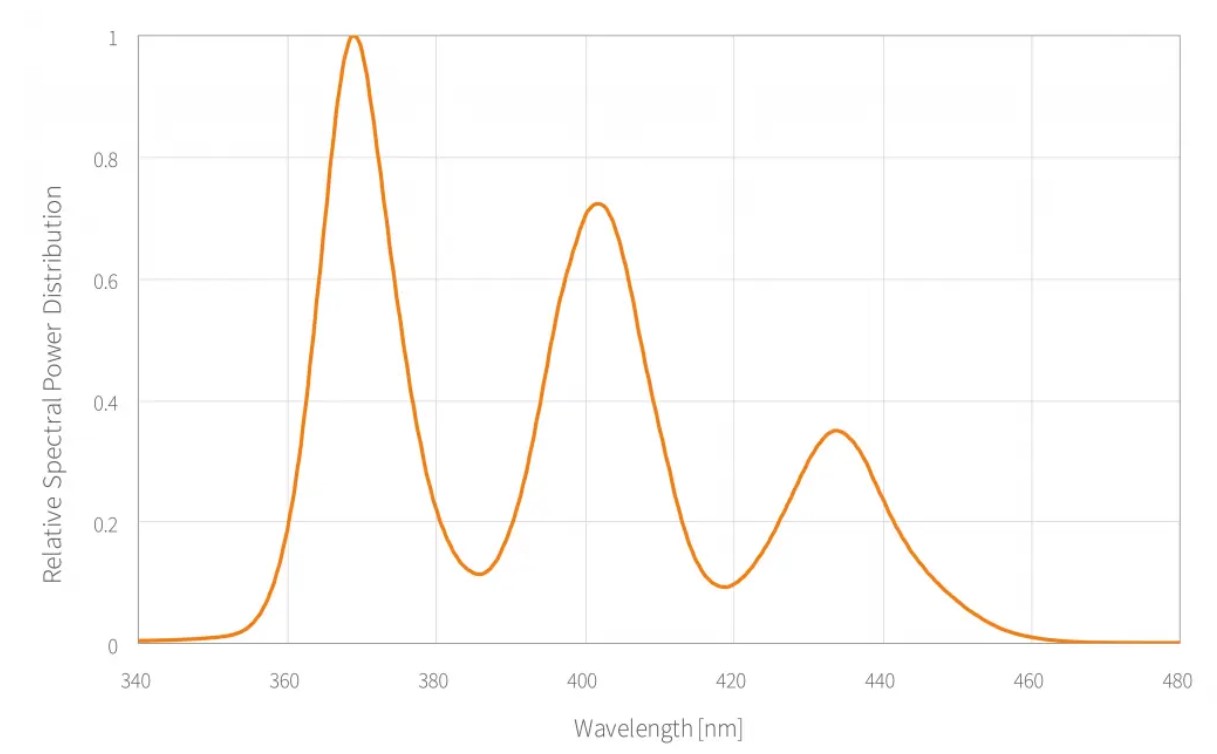

半导体行业借助紫外光谱范围(i 线:365 nm、h线:405 nm和g线:436 nm)中的高功率辐射在各种光刻、曝光和显影工艺中创建复杂的微观结构

2023-04-24 11:23:28 1480

1480

那时集成电路也刚刚发明不久,光刻工艺还在微米级别,工艺步骤也比现在简单很多美国是走在世界前列的。在那个对工艺要求并不高的年代,很多半导体公司通常自己用镜头设计光刻工具,光刻机在当时甚至不如照相机的结构复杂。

2023-04-20 09:22:33 1314

1314 此次采用全新22nm工艺生产的首颗MCU,扩展了瑞萨广受欢迎的基于32位Arm Cortex-M内核的RA产品家族。该新型无线MCU支持低功耗蓝牙5.3 (BLE),并集成了软件定义无线电(SDR)。

2023-04-14 11:08:23 628

628 搞定2nm工艺需要至少3方面的突破,一个是技术,一个是资金,一个是市场,在技术上日本是指望跟美国的IBM公司合作,后者前两年就演示过2nm工艺,但IBM的2nm工艺还停留在实验室级别,距离量产要很远。

2023-04-14 10:24:55 507

507 新的High NA EUV 光刻胶不能在封闭的研究环境中开发,必须通过精心设计的底层、新型硬掩模和高选择性蚀刻工艺进行优化以获得最佳性能。为了迎接这一挑战,imec 最近开发了一个新的工具箱来匹配光刻胶和底层的属性。

2023-04-13 11:52:12 1164

1164 瑞萨电子今日宣布推出基于 22nm 制程的首颗微控制器(MCU)。通过采用先进工艺技术,提供卓越性能,并通过降低内核电压来有效降低功耗。先进的工艺技术还提供更丰富的集成度(比如 RF 等),能够在更小的裸片面积上实现相同的功能,从而实现了外设和存储的更高集成度。

2023-04-12 10:07:19 454

454 此前该公司指出,公司已建成年产5吨ArF干式光刻胶生产线、年产20吨ArF浸没式光刻胶生产线及年产45吨的光刻胶配套高纯试剂生产线,具备ArF光刻胶及配套关键组分材料的生产能力,目前公司送样验证的产品均由该自建产线产出。

2023-04-11 09:25:32 920

920 下图显示了Intel的第6代晶体管(6T)SRAM尺寸缩小时间表,以及多晶硅栅刻蚀技术后从90nm到22nm技术节点6TSRAM单元的SEM图像俯视视图。可以看出,SRAM的布局从65nm节点已发生

2023-04-03 09:39:40 2451

2451 光刻是将设计好的电路图从掩膜版转印到晶圆表面的光刻胶上,通过曝光、显影将目标图形印刻到特定材料上的技术。光刻工艺包括三个核心流程:涂胶、对准和曝光以及光刻胶显影,整个过程涉及光刻机,涂胶显影机、量测设备以及清洗设备等多种核心设备,其中价值量最大且技术壁垒最高的部分就是光刻机。

2023-03-25 09:32:39 4948

4948 为2nm及更先进芯片的生产提供更强大的助力。 计算光刻是芯片设计和制造领域中最大的计算工作负载,每年消耗数百亿CPU小时。而NVIDIA cuLitho计算光刻库利用GPU技术实现计算光刻,可以极大的降低功耗、节省时间。 目前台积电、光刻机制造商阿斯麦,以及EDA巨头新思科技都已经导入

2023-03-23 18:55:37 7488

7488

电子发烧友App

电子发烧友App

评论