引言:氮化镓作为第三代宽禁带半导体材料的代表之一,因其优越的性能,例如高电子迁移率、高电子饱和速 率、耐高温及高热导率等优点吸引了越来越多的关注,也正是因为这些优点,垂直氮化镓功率晶体管在未来的电 力电子领域中具有很大的发展和广泛的应用前景.本文列出氮化镓材料和其他半导体材料主要的物理参数、氮化 镓单晶制备及其外延生长的主要方法,阐述了氮化镓功率器件在目前环境下的优势.针对器件结构,列出了横向器 件本身存在的问题和垂直器件的优点,解释了垂直器件为何能够成为未来功率器件的主流结构.在此基础上,详细 介绍了垂直电流孔径氮化镓晶体管、垂直氮化镓沟槽金属氧化物半导体场效应晶体管、基于原位氧化氮化镓夹 层的垂直沟槽金属氧化物半导体场效应晶体管和垂直氮化镓鳍式场效应晶体管的结构、工作原理、研究进展及 所存在的一些问题,并将文中所提及的垂直氮化镓功率晶体管的性能参数按器件种类和时间顺序进行归纳,为未 来氮化镓功率晶体管的发展提出了大致的方向.针对集成电路系统,归纳了氮化镓功率器件在驱动芯片方面的特 殊要求和关键技术.最后,针对当下的市场环境,列举了垂直氮化镓功率晶体管在中、低压范围内比较热门且发展 前景较好的应用场景。

电力电子技术是一项使用电力电子器件将电能进 行转换并加以控制的技术,其核心就是功率半导体器 件,它可以快速高效地完成弱电对强电的控制,是保证 设备正常使用的关键技术.功率器件可分为两类:一类 是以功率二极管、晶闸管、绝缘双极型晶体管为主的 双功率半导体器件;另一类是以垂直双扩散金属氧化 物晶体管(vertical double diffusion power metal oxide semiconductor, VDMOS)为代表的功率金属氧化物半导 体(metal oxide semiconductor, MOS)器件为主的单极功 率半导体器件.自1958年以来,硅基金属氧化物半导体 场效应晶体管就一直在全球微电子行业占据主导地位,并应用于各种电子设备当中.随着5G技术、汽车、无 线通信、航天航空等技术的高速发展,电气化程度的 提高对耐高温、耐高压、高频及大功率的性能有着迫 切需求,例如在汽车领域,内部各设备所需的电压范围 为600~1500 V,而传统的硅基器件以及横向晶体管(如高电子迁移率晶体管, high electron mobility transistor, HEMT)都存在一些问题,如材料性能不足以满足一 些特殊场景或器件结构所带来的弊端,导致它们都无 法承担这一重任。

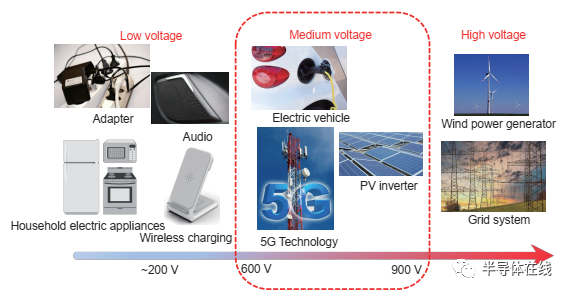

功率半导体器件的进步,核心就是半导体材料的 发展.氮化镓(GaN)作为第三代宽禁带半导体的代表之 一,拥有着宽禁带、高击穿场强、高热导率和高电子 漂移速率等优点,制备出的氮化镓器件导通电阻小、电子迁移率高、热导性好,而且在散热、能耗、体积 等方面也有着很大的优势,不仅能够极大地提升新兴 电力电子器件的性能,还能达到节省能源的效果.如图1所示,氮化镓材料在低、中、高压下都有着很多的应 用场景,适用范围十分广泛.加入三代半交流群,加VX:tuoke08。近年来,不管是同质外延,还是异质外延,氮化镓外延层的碳背景浓度和位错密 度都在逐渐降低,氮化镓自支撑衬底的成本逐渐下降,质量逐渐提高,为制备氮化镓垂直器件打下了坚实的基础。

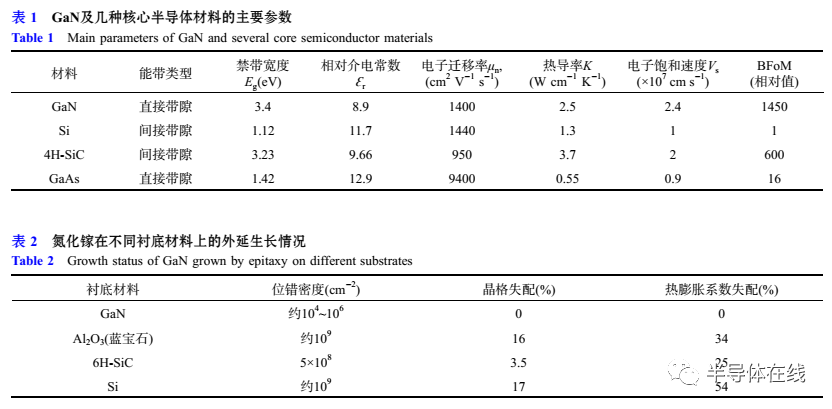

图 1 (网络版彩色)氮化镓功率器件的应用情况本文总结氮化镓材料与其他半导体材料的主要物 理参数及氮化镓外延生长的主流方法,主要介绍目前 氮化镓电流孔径垂直晶体管、垂直氮化镓沟槽金属氧 化物半导体场效应晶体管、基于原位氧化物氮化镓夹 层的垂直沟槽金属氧化物半导体场效应晶体管以及氮 化镓垂直鳍式功率晶体管的发展状况,概括了氮化镓 驱动集成电路(integrated circuit, IC)的关键技术,列出 了氮化镓功率晶体管的一些实际应用场景。1氮化镓材料及其制备方法 1.1氮化镓材料应用于功率器件的优势 电力电子器件的蓬勃发展与半导体材料的发展息 息相关.硅材料的出现使得电子器件领域发生了巨大 的变化.随着单晶硅生产工艺的发展,硅材料很快就占 据了半导体集成电路的主要市场,广泛应用于各个领 域当中,即便是今天,硅在半导体材料领域依然占有很 高的份额.随着功率器件的发展,硅基电力电子器件的 性能逐渐逼近材料极限,很难有更大的突破.第二代半 导体砷化镓(GaAs)具有更高的电子迁移率和饱和电子 速度等优势,稍微缓解了这一现象,但是由于GaAs材料 的禁带宽度、热导率、击穿场强及制作成本与硅(Si)材料相比并没有太大的优势,导致其在高压高频率领 域中得不到广泛的应用.因此,以GaN为代表的第三代 半导体横空出世,掀起了研究GaN基器件的热潮.表1列出了GaN与其他半导体材料的主要参数。从表1可以看出, GaN是直接间隙半导体,其禁带 宽度达到3.4 eV,与Si、碳化硅(4H-SiC)和GaAs相比, GaN在击穿场强、热导率和电子饱和速度等方面有着 更大的优势.同时, GaN的功率品质因数(Baliga figure of merit, BFoM)比其他材料大得多,这也就意味着GaN基器件能够更好地在高温、高压和高频率的环境下 工作。

图 1 (网络版彩色)氮化镓功率器件的应用情况本文总结氮化镓材料与其他半导体材料的主要物 理参数及氮化镓外延生长的主流方法,主要介绍目前 氮化镓电流孔径垂直晶体管、垂直氮化镓沟槽金属氧 化物半导体场效应晶体管、基于原位氧化物氮化镓夹 层的垂直沟槽金属氧化物半导体场效应晶体管以及氮 化镓垂直鳍式功率晶体管的发展状况,概括了氮化镓 驱动集成电路(integrated circuit, IC)的关键技术,列出 了氮化镓功率晶体管的一些实际应用场景。1氮化镓材料及其制备方法 1.1氮化镓材料应用于功率器件的优势 电力电子器件的蓬勃发展与半导体材料的发展息 息相关.硅材料的出现使得电子器件领域发生了巨大 的变化.随着单晶硅生产工艺的发展,硅材料很快就占 据了半导体集成电路的主要市场,广泛应用于各个领 域当中,即便是今天,硅在半导体材料领域依然占有很 高的份额.随着功率器件的发展,硅基电力电子器件的 性能逐渐逼近材料极限,很难有更大的突破.第二代半 导体砷化镓(GaAs)具有更高的电子迁移率和饱和电子 速度等优势,稍微缓解了这一现象,但是由于GaAs材料 的禁带宽度、热导率、击穿场强及制作成本与硅(Si)材料相比并没有太大的优势,导致其在高压高频率领 域中得不到广泛的应用.因此,以GaN为代表的第三代 半导体横空出世,掀起了研究GaN基器件的热潮.表1列出了GaN与其他半导体材料的主要参数。从表1可以看出, GaN是直接间隙半导体,其禁带 宽度达到3.4 eV,与Si、碳化硅(4H-SiC)和GaAs相比, GaN在击穿场强、热导率和电子饱和速度等方面有着 更大的优势.同时, GaN的功率品质因数(Baliga figure of merit, BFoM)比其他材料大得多,这也就意味着GaN基器件能够更好地在高温、高压和高频率的环境下 工作。 1.2氮化镓衬底及其外延层的制备 在过去10年中,同质外延生长GaN的成本很高,为 降低器件的制造成本,采用了在Si、SiC和蓝宝石上异 质外延生长的方法,以上这些衬底相比单晶氮化镓衬 底具有更低的成本,因此在市场上应用广泛.但是,异 质外延生长的GaN内部存在着较大的晶格失配及热失 配等问题.表2给出了在不同衬底上外延生长GaN的缺 陷浓度、晶格失配和热失配情况.这些失配将会导致 外延层产生晶格扭曲,从而形成较高的位错密度,甚至 破裂等问题,会严重影响GaN基器件的性能和使用 寿命,这是目前GaN基器件的性能远低于其材料理论 极限的重要原因之一。高质量的GaN单晶材料是制备高性能器件的基础,也是根本保障.获得高质量GaN外延层的最佳方案就 是同质外延,即在块状GaN衬底上外延生长GaN层.目 前, GaN单晶材料的生长方式主要分为气相外延和液 相外延.其中,气相外延包括金属有机物化学气相沉积(metal organic chemical vapor deposition, MOCVD)、氢 化物气相外延(hydride vapor phase epitaxy, HVPE)及其 衍生方法,特点在于生产速率快、尺寸大,但晶体质量 有待提高,产品一致性较差.液相外延主要采用氨热法 和助溶剂法,其特点是可制备高纯度、高晶体质量且 重复性高的GaN单晶衬底,但是对设备的要求高,并且 生长速率较低.在商业应用中,较低成本HVPE应用最 广泛也最成熟,并且随着改良,与氨热法和钠助熔剂法 结合,生产的GaN单晶衬底的位错密度在不断降低,晶 圆尺寸在逐渐增大,制备成本也在不断地降低。HVPE生产出的GaN是未掺杂的,其载流子浓度只 有1016~1017cm−3,难以用于半导体器件的制备,需针 对不同的器件引入不同的掺杂剂,从而改变GaN的电 学性质.其中,浅施主掺杂剂有硅和锗,浅受主掺杂 剂有镁,深能级掺杂剂有铁和碳,可分别实现GaN的N型、P型和半绝缘电特性,再加上高纯半绝缘GaN的发展,可以有效提高器件的耐压能力,从而满足 各种器件的要求。

1.2氮化镓衬底及其外延层的制备 在过去10年中,同质外延生长GaN的成本很高,为 降低器件的制造成本,采用了在Si、SiC和蓝宝石上异 质外延生长的方法,以上这些衬底相比单晶氮化镓衬 底具有更低的成本,因此在市场上应用广泛.但是,异 质外延生长的GaN内部存在着较大的晶格失配及热失 配等问题.表2给出了在不同衬底上外延生长GaN的缺 陷浓度、晶格失配和热失配情况.这些失配将会导致 外延层产生晶格扭曲,从而形成较高的位错密度,甚至 破裂等问题,会严重影响GaN基器件的性能和使用 寿命,这是目前GaN基器件的性能远低于其材料理论 极限的重要原因之一。高质量的GaN单晶材料是制备高性能器件的基础,也是根本保障.获得高质量GaN外延层的最佳方案就 是同质外延,即在块状GaN衬底上外延生长GaN层.目 前, GaN单晶材料的生长方式主要分为气相外延和液 相外延.其中,气相外延包括金属有机物化学气相沉积(metal organic chemical vapor deposition, MOCVD)、氢 化物气相外延(hydride vapor phase epitaxy, HVPE)及其 衍生方法,特点在于生产速率快、尺寸大,但晶体质量 有待提高,产品一致性较差.液相外延主要采用氨热法 和助溶剂法,其特点是可制备高纯度、高晶体质量且 重复性高的GaN单晶衬底,但是对设备的要求高,并且 生长速率较低.在商业应用中,较低成本HVPE应用最 广泛也最成熟,并且随着改良,与氨热法和钠助熔剂法 结合,生产的GaN单晶衬底的位错密度在不断降低,晶 圆尺寸在逐渐增大,制备成本也在不断地降低。HVPE生产出的GaN是未掺杂的,其载流子浓度只 有1016~1017cm−3,难以用于半导体器件的制备,需针 对不同的器件引入不同的掺杂剂,从而改变GaN的电 学性质.其中,浅施主掺杂剂有硅和锗,浅受主掺杂 剂有镁,深能级掺杂剂有铁和碳,可分别实现GaN的N型、P型和半绝缘电特性,再加上高纯半绝缘GaN的发展,可以有效提高器件的耐压能力,从而满足 各种器件的要求。

2垂直氮化镓功率晶体管 按电流在器件内部的流动方向,目前GaN基器件 的结构可分为横向结构和垂直结构.横向器件(主要是HEMT)的内部电场分布不均匀,峰值电场会集中在漏 极和栅极边缘(电场集中效应),该处的电场强度大于GaN材料的临界击穿场强,导致器件提前击穿,难以发 挥GaN材料耐高压的优势.而且,击穿电压和栅极-漏极 的间距成正比,即要提高器件的耐压水平就必须增大 器件面积,这不仅增加了制作成本,还不利于后期的集 成;横向器件对缓冲层的厚度和晶体质量也有一定的 要求,增加了器件外延生长的生产成本和复杂性;再加 上表面陷阱态和电场拥挤的影响,很容易使器件产生 电流崩塌,从而达不到预计的电流值。垂直GaN器件的电流方向平行于GaN外延层的生 长方向,这种设计可以有效地提高器件的导通电流和 击穿电压.在不改变器件尺寸的情况下,增加GaN漂移 层的厚度即可提高器件的击穿电压.垂直器件无需考 虑表面陷阱对其的影响=,内部电场在远离表面的GaN层中达到峰值,提高了器件耐压水平的下限.最重要的是, GaN垂直功率器件具有雪崩能力,即存在雪崩 击穿,这是横向结构不可能有的,该优点提高了器件的 可靠性,避免了过度设计设备.下面分别介绍垂直结构 的氮化镓电流孔径晶体管、氮化镓沟槽金属氧化物半 导体场效应晶体管、基于原位氧化物氮化镓夹层的垂 直沟槽金属氧化物半导体场效应晶体管和氮化镓鳍式 晶体管的原理、结构及主要发展情况。

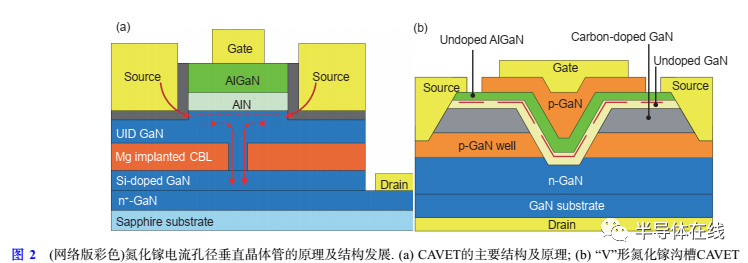

2.1氮化镓电流孔径垂直晶体管 电流孔径垂直晶体管(current aperture vertical electron transistor, CAVET)是横向拓扑和纵向拓扑的有效 结合,目的是发挥AlGaN/GaN异质结处二维电子气沟 道(two-dimensional electron gas, 2DEG)的高导电性以 及垂直结构所带来的优势.第一个用于高压应用的GaN基CAVET结构由Ben-Yaacov等人开发完成,其 结构与双扩散MOS(double diffused metal oxide semiconductor, DDMOS)结构类似,如图2(a)所示.其中,电 流阻挡层(current-blocking layer, CBL)是通过在GaN层 中掺杂Mg实现的,用来将电流限制在栅极下方的小孔 径区域.通过对栅极施加偏压从而控制2DEG的开启和 关断,不同于横向结构的HEMT,这种开关的优势是:在 电压阻断的情况下,高电场区将主要位于栅极下方,即 表面发生击穿的可能性下降,可提供更高的击穿电压.然而,由于CAVET的AlGaN/GaN沟道依赖于栅极调控,因此该器件通常处于常开状态。 为了提高开关速度和安全性,增强型(enhance mode, E-mode)器件是大功率设备的优先选择. Chowdhury等人通过使用Mg离子注入的GaN作为非 合金源的电流阻挡层,并在栅极金属化之前对栅极区 域进行10 min的CF4处理,制作了第一个增强型CAVET,其最大源漏电流为5.6×103A/cm2,实现了高达0.6 V的 阈值电压.在该器件的制备过程中,因为异质结层(AlGaN/GaN)是在M g掺电流阻挡层形成之后通过MOCVD再生长的, Mg离子的向上扩散使得器件的阈 值电压发生了明显的变化.于是, Chowdhury等人改 变了AlGaN/GaN层的生长方式,通过分子束外延(molecular beam epitaxy, MBE)进行再生长,制备出的器件在 源栅电压为–15 V条件下,击穿电压约为250 V,比导通 电阻为2.2 mΩ cm2。 为保持p-GaN的导电性, Yeluri等人通过掩埋导 电p-GaN层作为电流阻挡层.其中, p-GaN层通过MOCVD再生长,沟道则通过氨分子束外延来完成,制 备出的器件比导通电阻降至0.4 mΩ cm2,导通电流可达10.9 kA/cm2. Nie等人在原结构基础上增加了边缘终 端结构,并在栅极和AlGaN阻挡层之间新增一层pGaN,使其可以正常地关闭操作,制备出的晶体管表现 出大于2.3 A的饱和电流、1.5 kV的击穿电压、2.2 mΩ cm2的比导通电阻及1.0×109V2/cm2的品质因数(figure of merit, FOM). 2010年,松下公司制备了一种击穿电 压为1.7 kV,导通电阻为1.0 mΩ cm2的“V”形沟槽CAVET,如图2(b)所示,其中p-GaN/AlGaN/GaN三层在漂 移层上形成的“V”形槽上外延再生长.该沟道利用了半 极性面,降低了AlGaN/GaN界面处薄层载流子浓度,实 现了2.5 V的高阈值电压和稳定的开关操作.值得一提 的是,沟道下方的p-GaN阱层上形成了含碳掺杂的绝缘GaN层,该层能够抑制截止状态下源极和漏极之间的 穿通电流,实现了良好的截止状态特性,并在400 V/15 A条件下实现了快速开关。 Ji等人的器件制备流程与上述提及的类似,不同 点在于移除了栅极下方的p-GaN层,得到了阈值电压为20 V、击穿电压为225 V的常关型沟槽CAVET.在随后 的研究中,他们通过改善栅极沟槽蚀刻质量和采用 栅极电介质使击穿电压达到了880 V,比导通电阻为2.7 mΩ cm2,减少了栅极与漏极之间的泄漏.由于栅极采用 金属-绝缘层-半导体(metal insulation semiconductor, MIS)结构,阈值电压从20 V变为21 V. 2022年, Danielraj等人采用一种三角形(“▽”形)凹槽的GaN CAVET,实现了1513~1590 V的击穿电压及1.24 mΩ cm2的低导 通电阻,但因为该器件的栅极长度可缩放,其性能及可 靠性可能会受到电流崩塌、短沟道效应和漏电流的影 响,为了克服短沟道器件中关态漏电流的影响,在 其中掺入碳或镁用于补偿。GaN CAVET距离广泛地商业应用仍需要进一步的 发展,主要问题源于再生长工艺.相邻电流阻挡层之间 形成的孔径区域,其掺杂和尺寸大小控制导致制造工 艺相对复杂且难以控制,且因生长工艺所存在的问题,将导致器件的源极和漏极、栅极和漏极之间有着很高 的漏电流,难以大规模生产使用。

Ji等人的器件制备流程与上述提及的类似,不同 点在于移除了栅极下方的p-GaN层,得到了阈值电压为20 V、击穿电压为225 V的常关型沟槽CAVET.在随后 的研究中,他们通过改善栅极沟槽蚀刻质量和采用 栅极电介质使击穿电压达到了880 V,比导通电阻为2.7 mΩ cm2,减少了栅极与漏极之间的泄漏.由于栅极采用 金属-绝缘层-半导体(metal insulation semiconductor, MIS)结构,阈值电压从20 V变为21 V. 2022年, Danielraj等人采用一种三角形(“▽”形)凹槽的GaN CAVET,实现了1513~1590 V的击穿电压及1.24 mΩ cm2的低导 通电阻,但因为该器件的栅极长度可缩放,其性能及可 靠性可能会受到电流崩塌、短沟道效应和漏电流的影 响,为了克服短沟道器件中关态漏电流的影响,在 其中掺入碳或镁用于补偿。GaN CAVET距离广泛地商业应用仍需要进一步的 发展,主要问题源于再生长工艺.相邻电流阻挡层之间 形成的孔径区域,其掺杂和尺寸大小控制导致制造工 艺相对复杂且难以控制,且因生长工艺所存在的问题,将导致器件的源极和漏极、栅极和漏极之间有着很高 的漏电流,难以大规模生产使用。

2.2垂直氮化镓沟槽金属氧化物半导体场效应晶体管

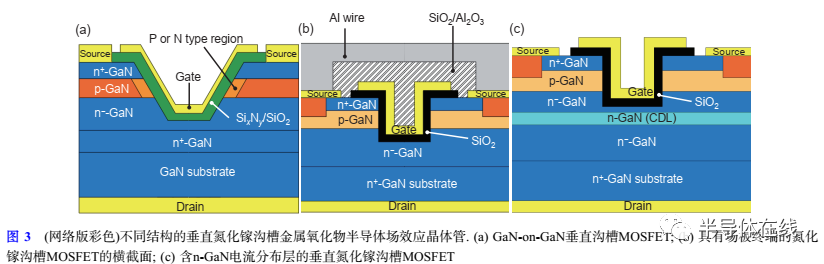

2007年,罗姆半导体集团(ROHM Semiconductor)通过MOCVD在蓝宝石衬底上外延生长GaN,并 在此基础上制造出了氮化镓沟槽金属氧化物半导体场 效应晶体管(GaN trench metal oxide semiconductor field effect transistor, GaN trench MOSFET).该器件显现出良 好的直流特性,导通电压为5.1 V,这是GaN trench MOSFET首次被报道.如图3(a)所示, 2008年,罗姆半导 体集团在GaN衬底上制备出首个完全垂直的MOSFET,与之前的研究相同,采用SiO2硬掩模进行遮 挡,在Cl2/SiCl4氛围中进行等离子体干法蚀刻工艺,形 成垂直栅极的沟槽结构,通过电子回旋共振(electron cyclotron resonance, ECR)等离子体在沟槽内连续沉积 氮化硅(SixNy)和二氧化硅(SiO2),以此组成的双层结构 作为栅极绝缘体.该器件的阈值电压为3.4 V,沟道迁移 率达到131 cm2/(V s),导通电阻低于10 mΩ cm2。干法蚀刻工艺会引发一些问题,它会导致沟槽表 面粗糙以及离子轰击造成损坏,影响沟道迁移率. 2008年,丰田中央研究所的Kodama等人针对这一问题发 展了新的沟槽结构制造方法:使用浓度为25%的四甲 基氢氧化铵(TMAH)作为蚀刻剂,通过湿法蚀刻获得光 滑的非极性( 1100 )平面. TMAH溶液与氢氧化钾(KOH)不同,它不会造成碱金属污染,可获得平滑的垂直侧 壁,从而提高沟道迁移率. He等人通过酸洗和后续NH4钝化获得了高质量的MOS界面,在4英寸(1 in =2.54 cm)的自支撑GaN晶圆片上制备出击穿高压高达1306 V、比导通电阻为1.93 mΩ cm2的大面积GaN Trench MOSFET,为以后大面积生长提供了更多的选择。为了进一步提高耐压, Oka等人在MOSFET的隔 离台面周围增加了场板结构,图3(b)为结构示意图.该 结构有效减缓了PN结边缘存在的电场拥挤效应,击穿 电压从775 V提高到1605 V,比导通电阻为12.1 mΩ cm2,仍需要改善. 2015年,他们减小n−-GaN的厚度,但 增加其掺杂浓度,降低p-GaN的厚度和掺杂浓度,通过 采用规则六角单元沟槽栅极布局来增加单位面积的栅极宽度,虽然击穿电压降低到1250 V,但是比导通电 阻从12.1 mΩ cm2大幅度地降低到1.8 mΩ cm2,并在保 证击穿电压超过1.2 kV的特性下,制造的尺寸为1.5 mm ×1.5 mm,并且支持高达23.2 A大电流的GaN Trench MOSFET.为了使器件能够在更高的电流中工作, Oka等人在n−-GaN中插入一层电流分布层(Current distribution layer, CDL),使正向电流密度提高了1.17倍,并制备出了能够在100 A电流下工作的3 mm×3 mm大 尺寸垂直沟槽GaN MOSFET,其横截面结构如图3(c)所 示.他们分别对有无CDL层的器件进行了电学测试,带CDL层的MOSFET性能表现更佳.该器件中的电流分 布层由轻薄的n型掺杂层组成,掺杂浓度为2×1016cm−3,并远离p-GaN沟道层,这样可避免p-GaN沟道引起的电 流分布层耗尽,在不影响击穿电压的情况下,使有效电 流在漂移层中扩散,更好地分配来自栅极沟槽底部的 电流,从而提高器件的最大工作电流。

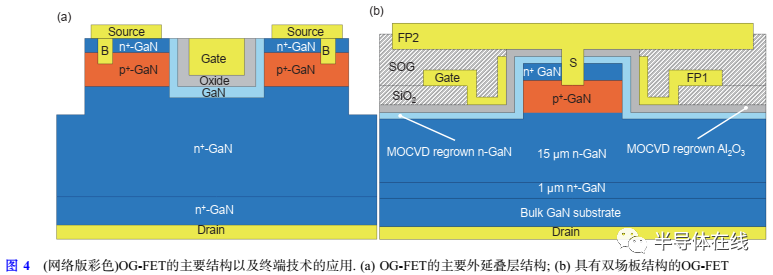

沟槽深度对器件的比导通电阻有着重要的影响,沟槽深度增加,由漂移层中耗尽区形成的势垒会削弱 对电流路径的影响.加宽沟槽下电流路径的宽度,会降 低导通电阻,但也会降低击穿电压,因此在器件结构 设计中需仔细考虑沟槽的深度. p-GaN层的参数在调节 垂直GaN MOSFET的阈值电压、比导通电阻和最大漏 极电流方面也起着重要的作用:降低p-GaN的掺杂浓度 可以使比导通电阻降低,但会导致最大漏极电流增 加、阈值电压降低; p-GaN的厚度和掺杂浓度的乘 积会影响器件的击穿机制,当其乘积足够高时,击穿机 制可变为雪崩击穿.根据这一特性, Liu等人通过优 化漂移层、p +-GaN层及沟槽栅极制备出了击穿电压为2783 V、比导通电阻为1.6 mΩ cm2的沟槽GaN MOS-FET。2.3基于原位氧化物氮化镓夹层的垂直沟槽金属氧化物半导体场效应晶体管 基于原位氧化物氮化镓夹层的垂直沟槽金属氧化物半导体场效应晶体管(in-situoxide GaN interlayerbased vertical trench MOSFET, GaN OG-FET)是基于传统沟槽MOSFET在结构上改进而来的.与传统的沟 槽MOSFET相比, OG-FET具有两个特征: (1)使用非故 意掺杂(unintentional doping, UID)的GaN中间层作为沟 道区域,减少了掺杂剂的库仑散射,增强了沟道电子迁 移率; (2)通过MOCVD原位生长氧化物,减缓了界面状 态,提高了栅极氧化物的可靠性.因为沟槽MOSFET的 沟道是由干法蚀刻形成的,在蚀刻过程中,侧壁上产生 的缺陷会导致反型沟道电子的场效应迁移率降低,从 而影响器件的性能. OG-FET的优势就是增强沟道电子 迁移率而不会损害正常的常关行为。加州大学的Gupta等人针对干法蚀刻带来的问 题,对“U”形MOSFET结构的形成提出了新的改进方法,通过MOCVD在栅介质和GaN之间生长一层薄的未掺 杂GaN中间层,随后在n-p-n沟槽结构上进行MOCVD电 介质沉积,如图4(a)所示.这使得器件的工作原理由pGaN产生反型层变成了非故意掺杂GaN(UID-GaN)的 积累,使得垂直沟槽GaN OG-FET中的漏极电流密度提 高.与传统沟槽栅极MOSFET相比,该器件的比导通电 阻降低至3.8 mΩ cm2,阈值电压为2 V,击穿电压为195 V. 2017年,他们利用低损伤栅极沟槽蚀刻和块状GaN衬底,制备出了击穿电压为990 V,导通电阻为2.6 mΩ cm2的OG-FET,并在没有终端的情况下实现了1.6 MV/cm的高击穿场强.同年,他们采用场板边缘终 端结构使击穿场强提高到2.0 MV/cm(~1000 V). Ji等人使用15 μm厚均匀掺杂的GaN漂移层,并采用双 场板新型结构,如图4(b)所示.该GaN OG-FET的沟道迁 移率为185 cm2/(V s),击穿电压为1435 V,比导通电阻 为2.2 mΩ cm2.他们在400 μm×500 μm的大面积上制 备了同样的器件,击穿电压高达900 V,导通电阻为4.1 Ω. 2018年,他们制备了可实现1 A高输出电流的大面积OG-FET。

UID-GaN中间层在经过MOCVD生长后,需要对pGaN掩埋层进行高温退火,用于激活p-GaN层,这个过 程产生了高热量预算,对器件几何形状的形成也会造 成限制.为了减少高热量的预算, Li等人通过分子束 外延(MBE)形成一层UID-GaN沟道,形成了与OG-FET类似的结构,该结构的击穿电压为600 V左右,导通电 阻为0.3 Ω cm2. MBE再生长省去了激活p-GaN这一步 骤,改善了p-GaN的再钝化问题,避免了后续的激活 步骤,并能够提升沟道迁移率.任何功率器件在工作时都会产生热量.在OG-FET内部,大部分热量都集中在沟槽和GaN夹层附近.在实 际应用时,由于电池单元的紧密排列,相互之间会产生 热串扰. Chatterjee等人通过分析OG-FET的内部电场 和发热分布,提出可通过增加各单元间的间距和阵列 纵横比,显著降低了OG-FET单元阵列的峰值温度。

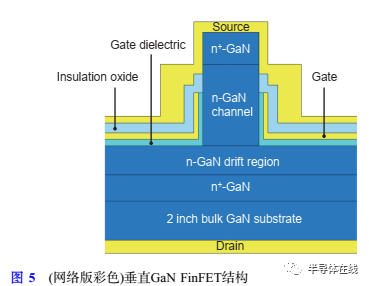

2.4垂直氮化镓鳍式场效应晶体管 传统的垂直沟槽GaN MOSFET已有着良好的性能 表现,但是在外延再生长以及p-GaN的需求方面,阻碍了垂直GaN功率晶体管的发展.不同于n-GaN, p-GaN具 有低的受主激活率以及较低的载流子迁移率, p-GaN的 外延再生长也很大程度地增加了器件制造的复杂性和 成本。1999年, Hu等人发明了鳍式场效应晶体管(fin field-effect transistor, FinFET),并在硅衬底上制备出一 种新型的自对准双栅硅-绝缘体(silicon-on-insulator, SOI)结构的纳米MOS器件,这种结构增大了栅极的控 制面积,提高了器件栅极的控制能力.随着近几年半导 体材料的发展,垂直GaN FinFET应运而生.相对于传统 的沟槽MOSFETs, GaN FinFET的优势是只需要n-GaN,不需要p-GaN层来提供正常关断操作和关断状态下的 阻断. FinFET的栅极由鳍侧壁的电介质和栅极金属组 成,因为栅极金属和GaN之间的功函数差异,耗尽了鳍 片内的电荷载流子,从而提供了常关操作。对于FinFET,鳍的宽度需足够窄(<500 nm)以用于 完全耗尽,这种结构会降低器件的电流能力.麻省理工 学院的Sun等人结合了干法、湿法蚀刻,制备出了平 滑的垂直鳍片,在GaN衬底上制备出具有亚微米级鳍 状通道的GaN FinFET结构,如图5所示,鳍宽度为450 nm.该器件具有1 V的阈值电压、0.36 mΩ cm2的 比导通电阻及800 V击穿电压,且在积累层中获得了150 cm2/(V s)的高电子迁移率.值得注意的是,不同于 沟槽MOSFET通过电子的反转来工作, FinFET通过电 子的积累来运行. Zhang等人在此基础上进一步优化 了鳍的宽度,将其降低至220 nm左右,获得了1200 V的 高击穿电压和0.2 mΩ cm2低比导通电阻,并制备出具有10 A的电流能力和800 V击穿电压的大功率器件. 2018年, Zhang等人在0.45 mm2的大面积上制备出5 A的 电流能力及1200 V耐压的垂直功率FinFET,其比导通 电阻为2.1 mΩ cm2,阈值电压为1.3 V.与商用0.9~ 1.2 kV的Si和SiC功率晶体管相比,该器件表现出低的 输入电容(CISS)、输出电容(COSS)、栅极电荷(QG)、栅 极至漏极电荷(QGD)和反向恢复电荷(Qrr),以及高频开 关能力和优异的开关品质因数(FOMs)。

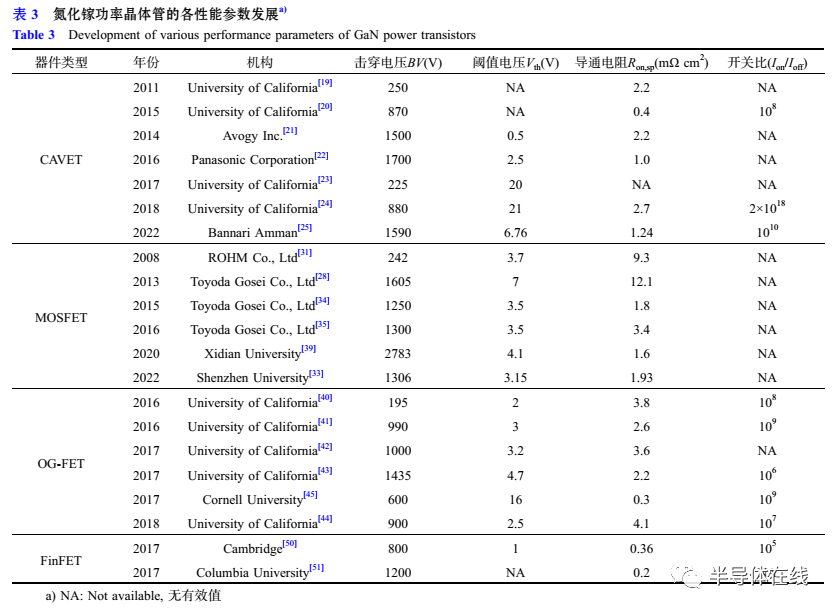

但是,缺少了p-GaN层来调节电场峰值,这些FinFET会发生不可逆转的击穿现象.有研究提出,在漂移 层中插入一层p基区来改善这类现象,但仍处于模拟 阶段,尚未制备出实际的器件.与其他垂直器件相比, FinFET鳍的制造和宽度控制增加了工艺的复杂性,制 备成本较高; FinFET的阈值电压相对较低(~1 V),因此 为确保设备能够安全操作而不发生故障,对栅极驱动 器的设计有较高的要求.近年来, FinFET和基于垂直np-n叠层的纳米丝(nanowire, NW)结构都实现了稳定的 常关操作,同时在3D叠层中集成p型层(基于纳米 线或基于鳍式结构),使得器件在栅极施加应力的情况下仍能实现稳定常关操作。2.5总结与展望 表3列出了文中所提及的氮化镓功率晶体管的参 数.早期的GaN功率器件朝着高耐压、低导通电阻的 方向发展,不过随着近几年来集成电路的高速发展以 及GaN功率晶体管在中低压范围内的应用逐渐变多,为了顺应市场发展与应用,对器件的阈值电压(threshold voltage,Vt )与开关比(Ion/Ioff)也有着一定的要求,尤 其是电路及其集成系统的性能与Vt的大小和一致性有 着密切的关系.随着未来芯片集成度越来越高,较高的 阈值电压有利于提高电子元件的抗干扰能力.开关比 是指器件开启和关断的电流大小比值,反映器件对电 流的调控能力.针对未来GaN功率晶体管,可以从以下 几个方面继续努力: (1)由于GaN功率晶体管的实际应 用将主要集中在200及600~900 V的电压范围内,高耐 压的需求将显得不那么强烈,而是往低导通电阻、较 高的阈值电压及高开关比发展; (2)研究GaN功率晶体 管在集成电路中的分布和优化布局,减少高密度的器 件布局之间所带来的不良影响; (3)使用更好的散热布 局和散热材料,尤其是产热量较高的位置,从而进一步 提高功率晶体管的性能和稳定工作时间.以上问题的 解决都可以有效地提高器件的安全性和可靠性,使得 器件或设备具有更长的使用寿命,从而更好地应用在 各个领域当中。

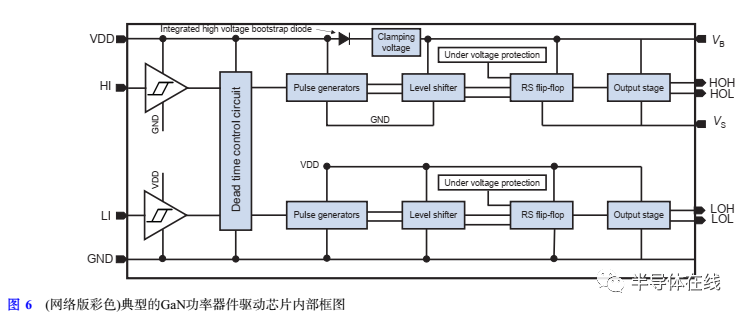

3氮化镓驱动IC 图6为典型的GaN功率器件驱动芯片的内部电路 框图. GaN功率器件栅极驱动芯片可以接收来自中央 处理器(central processing unit, CPU)、微控制单元(microcontroller unit, MCU)等外部芯片的控制信号,并输 出控制信号来控制GaN功率器件.与硅基MOSFET栅极 驱动芯片技术相比, GaN功率器件的栅极驱动电路有 以下3个要求: (1) GaN功率器件的开关频率比现有硅基器件高10~100倍,芯片内部高低压电路之间的隔离 区对信号传输电路的延迟要求极为严格.因此,需要设 计超高速隔离区信号传输技术和芯片架构. (2) GaN功 率器件的栅极电压通常不超过6 V,对应的驱动电压范 围较窄.因此,驱动电路的输出驱动电压应具有更高的 精度和更高的抗干扰能力. (3) GaN功率器件的运行没 有体二极管的反向恢复过程,但在死区时间内会有额 外的效率损失,需准确设置死区时间.对上述提及的3个要求, GaN功率器件驱动芯片的 关键技术分别对应为: (1)为匹配GaN功率器件的高频 特性,诞生了低延迟高压电平移位技术; (2)针对GaN基 器件栅极易击穿的特点,提出了栅级过压保护技术; (3)为了减少GaN功率器件反向传导时存在的较大损耗,提出了自适应死区技术。

3.1高压电平移位技术 高压电平移位技术主要有: (1)电阻负载的电平移 位模式是最传统的电平移位方式,需要RC滤波电路来 提高瞬时噪声抑制的能力. (2)采用四管电容负载电 平移位电路,其基本原理是在瞬时噪声信号到来时使 用共模检测电路的输出信号来屏蔽输入信号. (3) VI-V电平移位技术,是Fairchild采用的核心技术,通过 将电平移位支路的输出电压转化为电流信号,然后进 行共模比较,最后转化为电压信号输出,可有效抑制共 模噪声的干扰。3.2栅极过压保护技术 为实现输出级钳位,避免GaN器件栅源电压过大 而损坏,主流的栅极过压保护技术有: (1)齐纳钳位技 术,这是一种结构相对简单的钳位技术.利用其反向 传导齐纳钳位原理,将高压侧电源电压钳位在能够安 全驱动E-mode GaN功率器件的电压范围内,用于实现E-mode GaN驱动芯片高侧可靠性供电功能. (2)高压侧 输出级电压预调节技术,该技术是在集成自举之后,增 加了一个低压差线性稳压器(low dropout regulator, LDO)来稳定GaN功率器件栅极电压,该方案可有效地 控制驱动芯片的输出电压. (3)通过高压侧过压比较 电路来控制集成自举供电,实现低功耗的输出级钳位 技术.它是通过实时监测输出电压的大小,控制集成自 举供电通路的通断,从而达到输出级钳位的目的。

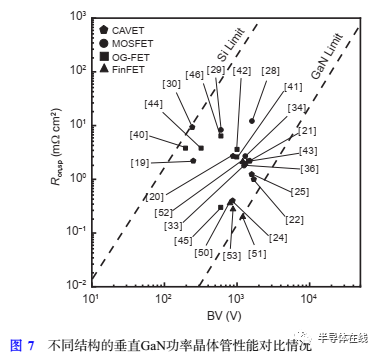

3.3自适应死区技术 自适应死区技术主要分为3种形式: (1)采用VS电 压检测的方式来判断功率管的开/关,通过高压二极管 检测VS端的负压,可以运用于上管关闭后,下管开通前 的死区控制; (2)采用高低压侧栅级电压检测的方式,高低压侧栅极信号相互影响,当低压侧GaN器件栅信 号为高时,不开启高压侧功率管,反之亦然. (3)通 过检测GaN功率器件开关瞬间的栅漏电荷变化量来控 制死区时间,这需要灵敏度较高的检测单元。4总结与应用 GaN作为第三代宽禁带半导体,有着相较于前两 代半导体更优越的性能. GaN基晶体管的出现解决了Si基晶体管所面临的很多问题.本文叙述了GaN材料参 数、GaN单晶衬底及其外延生长的方法,对比了横向器件和垂直器件并解释了选择垂直结构的原因,同时 介绍了CAVET、Trench GaN MOSFET、OG-FET和GaN FinFET的发展情况以及氮化镓驱动IC的关键技 术.图7汇总了文中所提到的晶体管对击穿电压(breakdown voltage,BV)/比导通电阻(Ron,sp)的情况,可以发 现,这些器件不仅比Si基功率器件性能更好,同时也在 逐渐接近GaN材料极限发展.垂直GaN三极管可以应用 在很多领域当中,尤其是中、低压的场景下.下面主要 介绍几种目前比较热门的方向。

(1)充电器及适配器.不同于十几年前电脑的适配 器及手机的“5 V×1 A”,目前市场上很多电子产品都使 用了快充技术,小至45 W,大至250 W,再加上人们对便 捷性的追求,大功率密度、高工作温度和小体积等成 为了目前充电器的发展目标.与目前普遍的Si基充电 器相比, GaN基充电器在满足功率密度的条件下可以 实现更好的散热、更高的工温度和更小的体积.目前 市场上已经出现了GaN充电器的“身影”,不仅体积比 传统手机、电脑充电器小得多,在充电速度和散热方 面也有着非常不错的表现。(2)无线通信技术.随着5G技术的发展,通信设备 对大功率、高频率、高速度的性能需求更加急切, GaN材料本身就已经具有这些物理性能,且GaN功率晶 体管在满足以上要求的情况下,在散热、体积及功耗 方面也有着较大的优势,可进一步提升电子产品的性 能,获得更好的通信体验。(3)无线充电器.无线充电目前也是一项热门且快 速发展的技术,各家手机厂商的旗舰机几乎都适配了 无线充电技术,甚至在电动汽车上也有它的“身影”.无 线充电的频率大致在100 kHz~6.78 MHz范围内,这对 充电设备在温度控制、转换频率和大功率等方面有着 较高的要求,尤其是给电动汽车这种大型工具进行无 线充电,对充电设备的要求会更高。 (4)汽车应用. GaN功率器件的发展,最大的受益者 之一便是汽车的电气系统,主要应用在车载充电器(onboard charger, OBC)、DC-DC转换器、电机驱动器和 激光雷达.目前汽车电池的电压范围为600~1500 V,对 器件有高耐压、大电流和快速开关的要求,而垂直GaN晶体管的发展使得汽车电气系统具有更简单灵活 的设计和更高的性能。 (5)大规模集成电路.目前的硅基器件已经逼近Si材料的理论极限,对高压高频大功率的需求却在不断 增加,硅基器件在体积和散热方面有很多的问题,不利 于后续大规模集成电路的发展.而GaN材料不仅在物 理性能上比硅材料更有优势,在相同性能的情况下,制备出的晶体管体积可以大幅度减小,配合使用小型 散热器,可以大幅度解决集成电路在体积和散热方面 上的问题,并拥有更高的开关频率,可提高设备的性能。来源:科学通报作者:李博1†, 尹越2†, 阳志超3, 刘新科1*, 李京波4*

-

集成电路

+关注

关注

5320文章

10719浏览量

353300 -

晶体管

+关注

关注

76文章

9045浏览量

135161 -

氮化镓

+关注

关注

53文章

1500浏览量

114866

发布评论请先 登录

相关推荐

氮化镓功率晶体管及其集成电路的发展状况

氮化镓功率晶体管及其集成电路的发展状况

评论