虹科KPA EtherCAT主站是一款协议栈产品,能够使用户快速利用EtherCAT技术的所有好处,例如实时操作、极短的循环时间、以及最低成本的最高性能。该协议栈的先进架构专注于可移植到不同的操作系统,可适配到各种硬件平台、并且可通过基础(Class B)、标准(Class A)和超值包进行缩放。本篇文章将介绍虹科KPA EtherCAT主站软件如何基于Xilinx ZYNQ UltraScale+做移植测试。

# Description

开发环境

#硬件开发板:Xilinx HW-Z1-ZCU102 revision1.1

#EtherCAT主站软件开发包:

MDK_xilinx-2018.3_freertos_a53_trial_v2.4.48714.0-release.zip

HW_SAMPLE_xilinx-2018.3_freertos_a53_trial_v2.4.48714.0-release.zip

备注:由于前期软件开发包是基于revision1.0的硬件以及vivado2018.3移植测试的,导致该软件包在vivado2018.3和新版本硬件移植测试出现问题,具体问题是制作完boot.bin后,上电没法启动运行;查了一下xilinx官网,说是新版本硬件需要使用vivado2019.1及其以上版本,后来在vivado 2019.1重新创建IPcore硬件工程,工程文件是zcu102_freeRTOS,重新生成bit文件(zcu102_freertos\project_1\project_1.sdk\design_1_wrapper_hw_platform_0)和fsbl.elf文件(zcu102_freertos\project_1\project_1.sdk\fsbl\Release)覆盖软件包原路径(\\externals\boot)的bit文件和fsbl.elf,问题解决;

Step1 软件安装

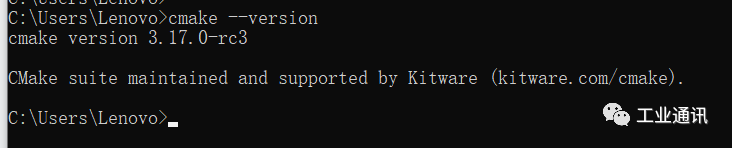

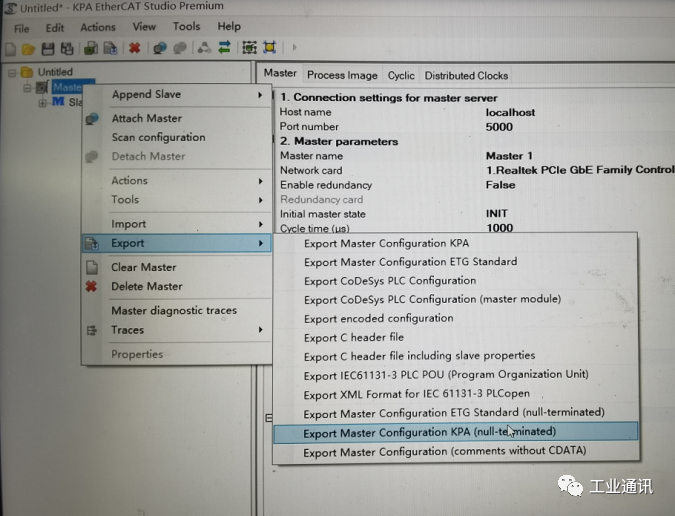

1. 安装KPA studio软件,Studio_v1.12.417.0_x86.zip;2. 安装基于windows的主站插件,MRT_WIN32_TRIAL_v1.6.44171.0.msi;3. 安装cmake环境,可到cmake官网下载exe安装,安装后查询到cmake版本如下: 参考《KPA Studio简易操作手册.pdf》使用EtherCAT配置软件,导出网络配置文件/ENI文件,可命名为master.xml或者其他名字,需与mkpa_config.h中命名保持一致,导出的ENI文件,格式一定要选择null-terminated格式。

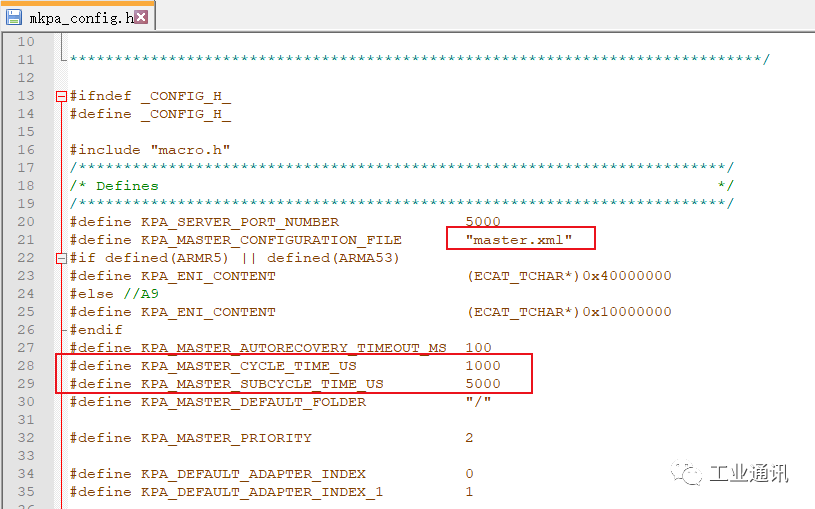

参考《KPA Studio简易操作手册.pdf》使用EtherCAT配置软件,导出网络配置文件/ENI文件,可命名为master.xml或者其他名字,需与mkpa_config.h中命名保持一致,导出的ENI文件,格式一定要选择null-terminated格式。

Step2 软件编译

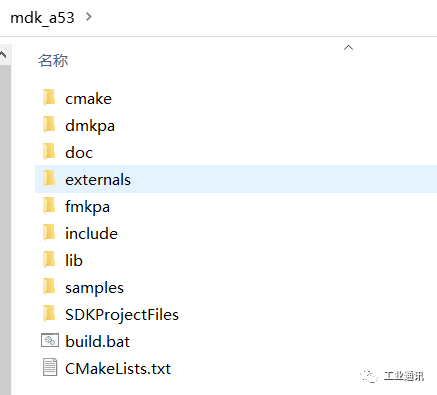

MDK_xilinx-2018.3_freertos_a53_trial_v2.4.48714.0-release.zip解压到mdk_a53文件夹下

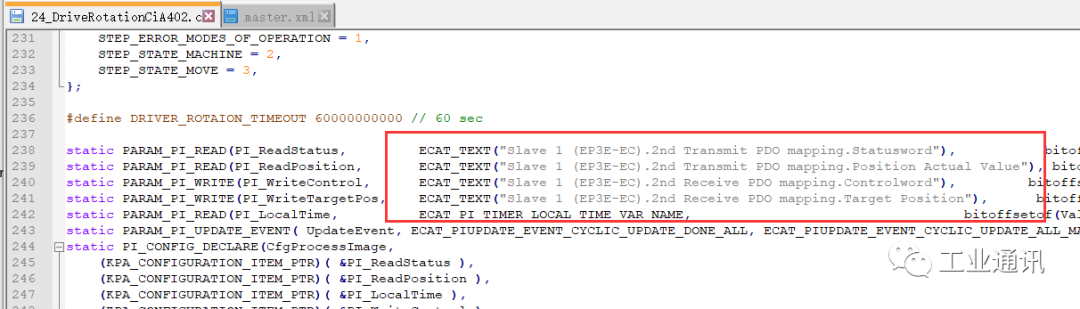

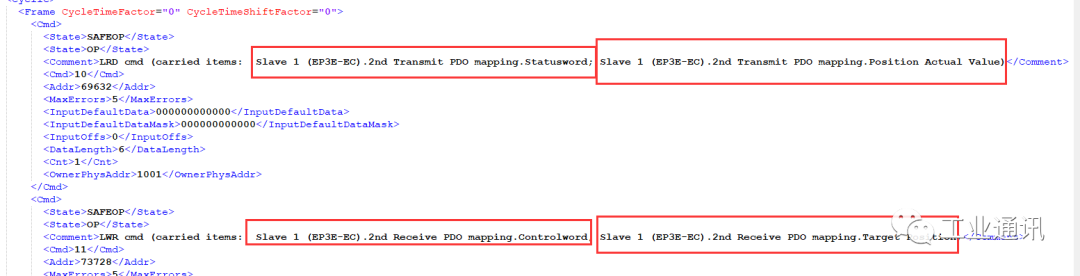

进入\mdk_a53\samples路径下修改对应样例程序,此处每个不同的样例程序包含不同的API,具有不同的功能,此处以24_DriveRotationCiA402为例,这是一个简单运行单轴伺服的样例程序,为了适配迈信伺服驱动器,需保持C文件中的描述和ENI文件描述一致,修改后保存

进入\mdk_a53\samples路径下修改对应样例程序,此处每个不同的样例程序包含不同的API,具有不同的功能,此处以24_DriveRotationCiA402为例,这是一个简单运行单轴伺服的样例程序,为了适配迈信伺服驱动器,需保持C文件中的描述和ENI文件描述一致,修改后保存

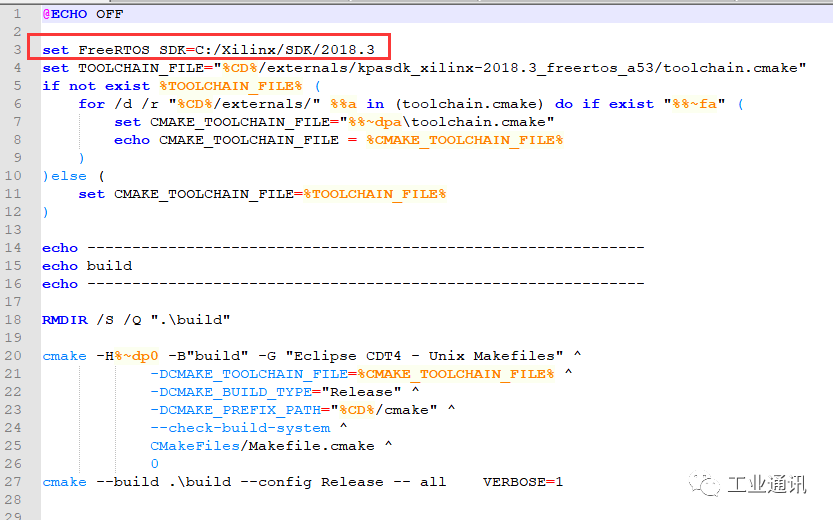

进入\mdk_a53下,打开build.bat,修改编译器路径,路径是xilinx SDK安装路径

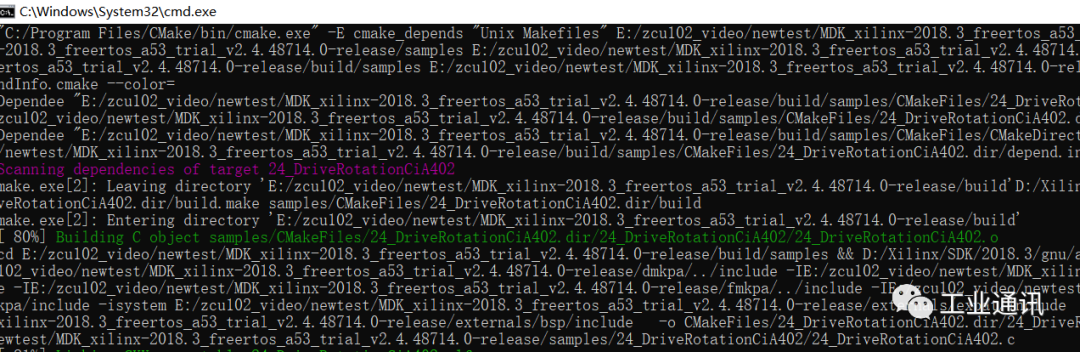

运行cmd,进入该路径下,运行build.bat,编译所有样例代码,包括编译24样例,在\build\samples路径下生成24_DriveRotationCiA402.elf文件

运行cmd,进入该路径下,运行build.bat,编译所有样例代码,包括编译24样例,在\build\samples路径下生成24_DriveRotationCiA402.elf文件

Step3 创建和运行boot.bin

进入mdk_a53\externals\boot路径,根据readme文件以及24_DriveRotationCiA402.bif文件;

拷贝zcu102_freeRTOS内vivado工程生成的design_1_wrapper.bit()文件到该路径下,覆盖原来bit文件;

zcu102_freertos\project_1\project_1.sdk\fsbl\Release下的fsbl.elf拷贝到该路径下,覆盖原来fsbl.elf文件;

拷贝\build\samples路径下生成的24_DriveRotationCiA402.elf到该路径下;

拷贝生成的ENI文件(master.xml)文件到该路径下

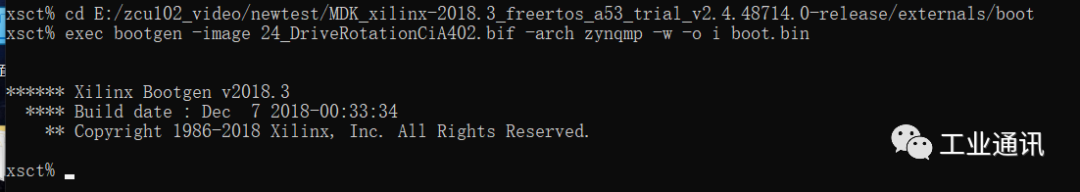

打开Xilinx XSCT tool进入到\externals\boot路径下,生成boot.bin

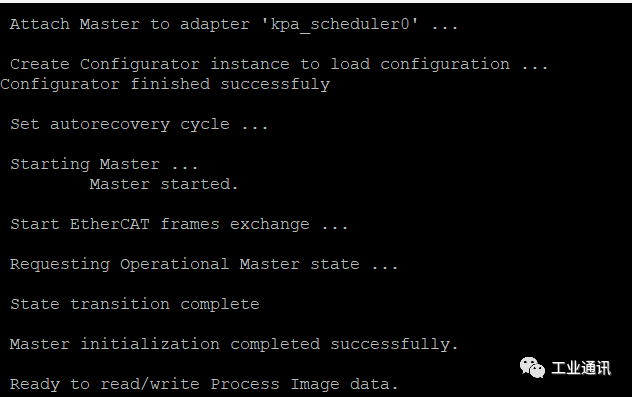

将boot.bin文件拷贝到SD卡中,设置开发板SD卡启动,上电运行

Step4 性能测试

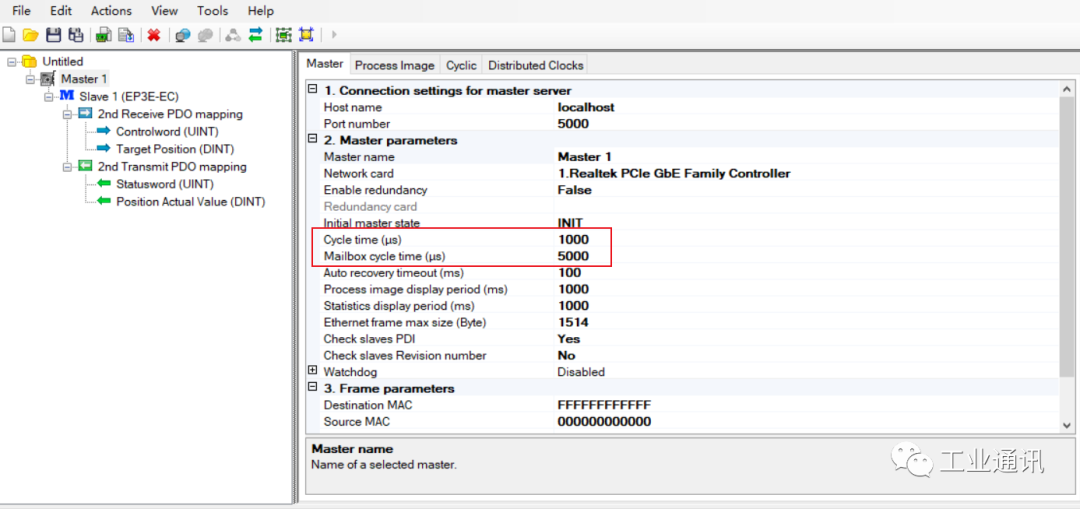

一般情况下EtherCAT主站性能测试会关注主站通讯周期,circle time是否稳定,抖动多少,因此可以设置在不同的circle time,比如2ms,1ms,500us,250us,125us等条件下测试抖动,可以采用第三方的抓包工具+wireshark进行报文分析,不同主站周期,需要修改代码以及ENI文件的circle time,此处以1ms主站周期,邮箱任务周期是5ms(主站周期的5倍)

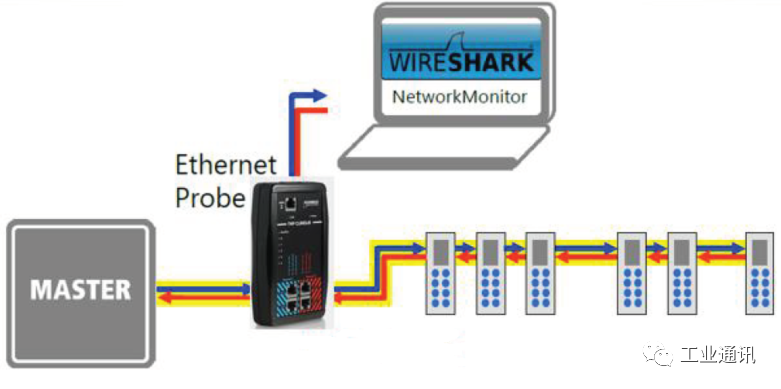

抓包方式,主站和从站直接接入第三方的抓包工具,连接方式如下示意图,可以先运行主站,待主从通讯稳定后,再进行数据抓包,这样抓出来的数据包就是pdo数据/过程数据,也可以主站启动前,开始抓包,这样就可以把整个启动过程的数据抓取出来,但是过滤时,op前的报文数据就不是我们需要分析的数据了。

抓包方式,主站和从站直接接入第三方的抓包工具,连接方式如下示意图,可以先运行主站,待主从通讯稳定后,再进行数据抓包,这样抓出来的数据包就是pdo数据/过程数据,也可以主站启动前,开始抓包,这样就可以把整个启动过程的数据抓取出来,但是过滤时,op前的报文数据就不是我们需要分析的数据了。

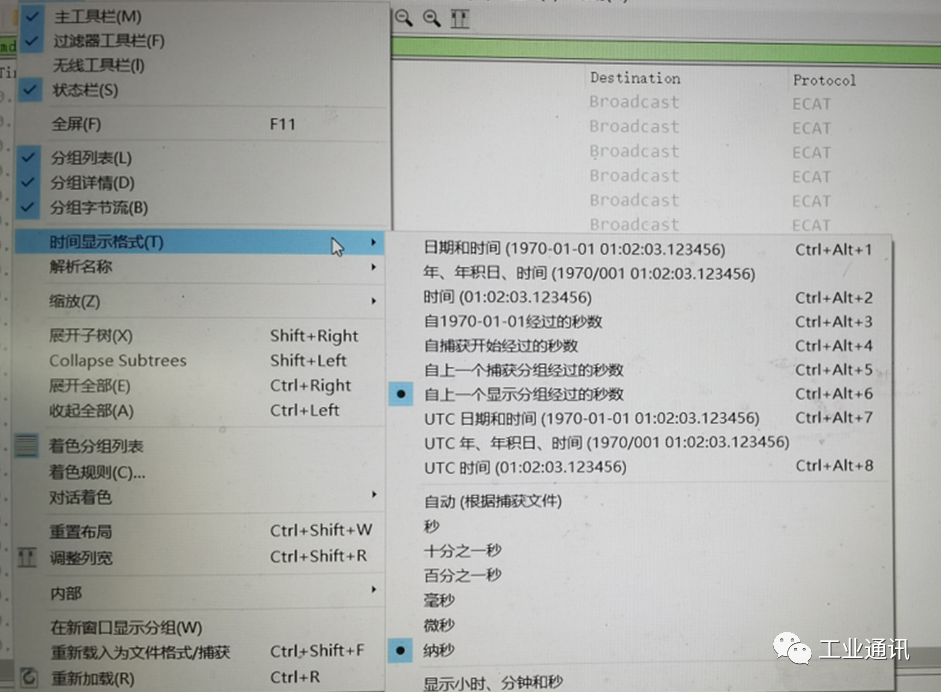

对Wireshark数据包进行针对性分析,设置时间显示格式如下:

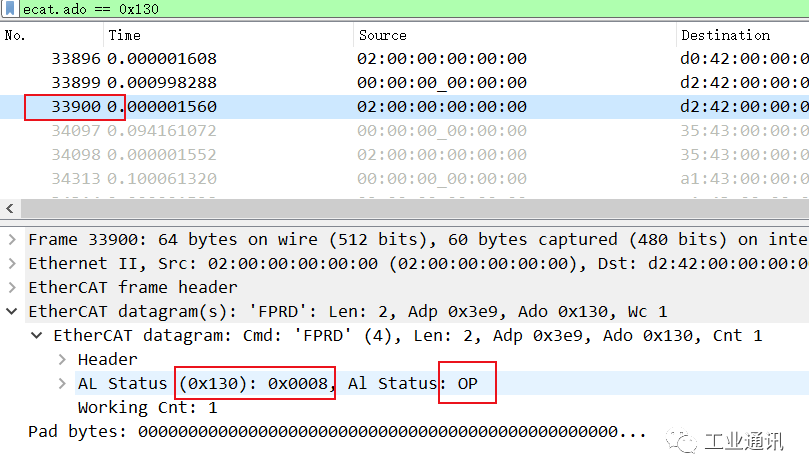

使用ecat.ado == 0x130命令,过滤出从站在第几条报文处进入op状态的,这里是33900,意味着33900前的报文不能用于分析circle time,因为pdo数据/周期性数据只在从站进入op后才被发送

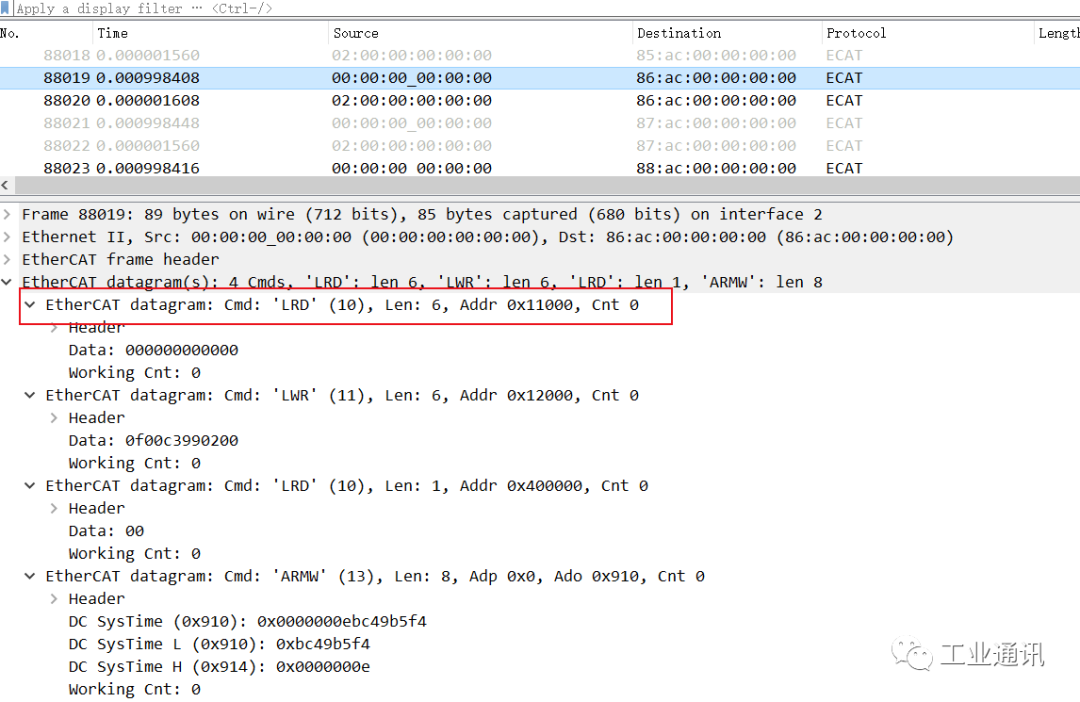

使用ecat.ado == 0x130命令,过滤出从站在第几条报文处进入op状态的,这里是33900,意味着33900前的报文不能用于分析circle time,因为pdo数据/周期性数据只在从站进入op后才被发送 分析周期性报文,注意到每个周期性报文包含三个子报文(逻辑寻址)以及一个DC相关的ARMW命令

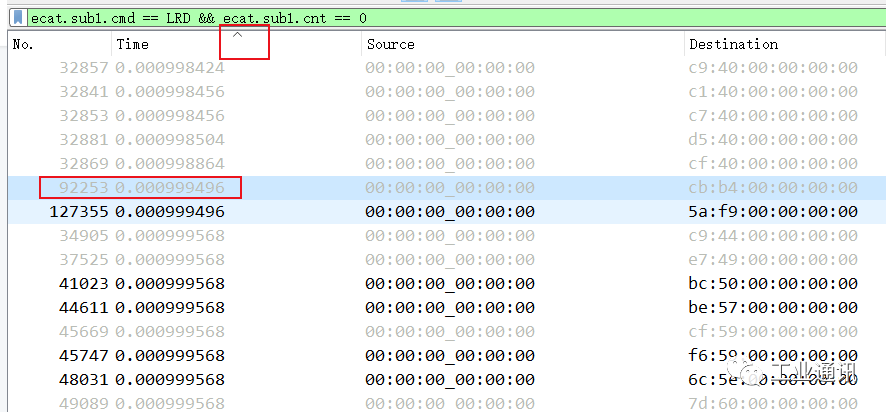

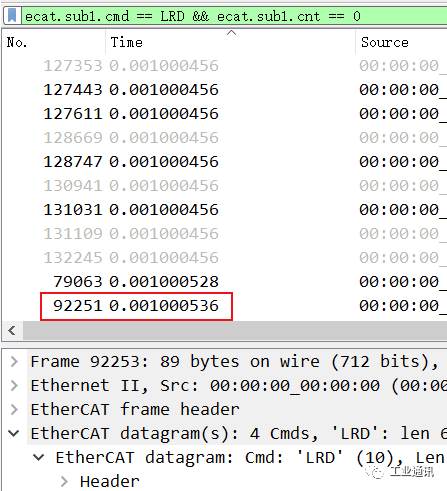

分析周期性报文,注意到每个周期性报文包含三个子报文(逻辑寻址)以及一个DC相关的ARMW命令 过滤出周期性报文,使用该指令ecat.sub1.cmd == LRD && ecat.sub1.cnt == 0,过滤出子报文1为LRD且计算器值为0(表示从主站发出,未经过从站)的周期性报文,选择三角进行报文排序,可以是从小到大,或者从大到小最小周期是999.496us

过滤出周期性报文,使用该指令ecat.sub1.cmd == LRD && ecat.sub1.cnt == 0,过滤出子报文1为LRD且计算器值为0(表示从主站发出,未经过从站)的周期性报文,选择三角进行报文排序,可以是从小到大,或者从大到小最小周期是999.496us

最大周期1000.536us

结论:可以看出1ms主站周期下,基于zcu102开发板,测试出来的主站周期的抖动是ns级别,实际在500us和250us,125us条件下,抖动都是在ns级别。

结论:可以看出1ms主站周期下,基于zcu102开发板,测试出来的主站周期的抖动是ns级别,实际在500us和250us,125us条件下,抖动都是在ns级别。

-

测试

+关注

关注

8文章

4429浏览量

125089

发布评论请先 登录

相关推荐

适用于Xilinx Zynq UltraScale+ MPSoC应用的电源参考设计

虹科干货 | 虹科KPA EtherCAT主站软件在Xilinx ZYNQ UltraScale+上移植测试

虹科干货 | 虹科KPA EtherCAT主站软件在Xilinx ZYNQ UltraScale+上移植测试

评论