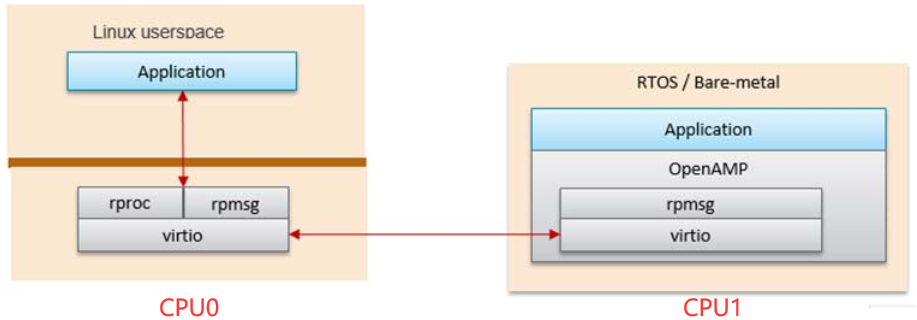

前 言:本文主要介绍基于OpenAMP框架的双核ARM通信案例的使用说明,CPU0(Master)运行Linux系统,CPU1(Remote)运行裸机或FreeRTOS程序。CPU0使用remoteproc加载CPU1程序,并对CPU1进行配置。

图 1

OpenAMP详细开发说明可查阅官方文档。

本文基于Xilinx Zynq-7010/7020平台进行案例测试。

图2

1、echo_test案例

1.1 案例功能

案例功能:CPU0使用RPMsg向CPU1发送数据,CPU1接收到数据后再使用RPMsg向CPU0回传数据。CPU0对回传的数据进行验证,并输出验证结果。

1.2 操作说明

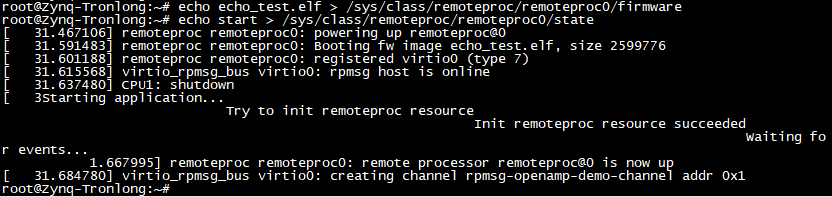

将CPU1裸机或FreeRTOS可执行文件复制到评估板文件系统“/lib/firmware/”目录下,并执行如下命令加载CPU1程序。

Target# echo echo_test.elf > /sys/class/remoteproc/remoteproc0/firmware

Target# echo start > /sys/class/remoteproc/remoteproc0/state

图 3

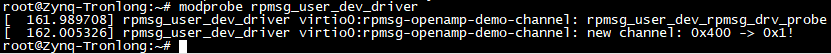

执行如下命令加载RPMsg驱动,并在“/dev/”目录下生成RPMsg设备节点。

Target# modprobe rpmsg_user_dev_driver

图 4

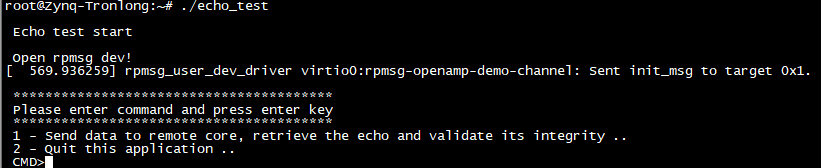

将CPU0应用程序可执行文件复制到评估板文件系统,并执行如下命令通过RPMsg与CPU1进行通信。

Target# ./echo_test

图 5

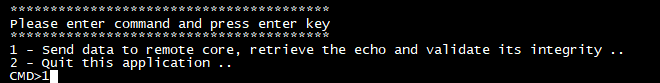

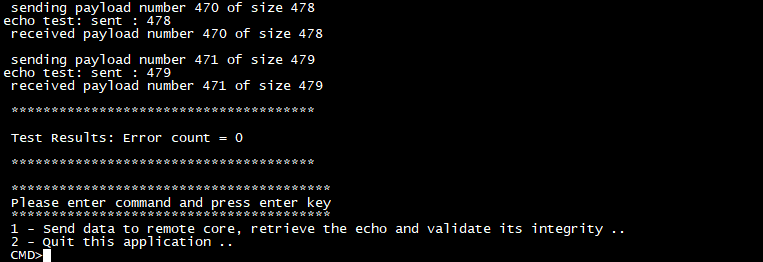

输入1,并按回车键进行测试。

图 6

图 7

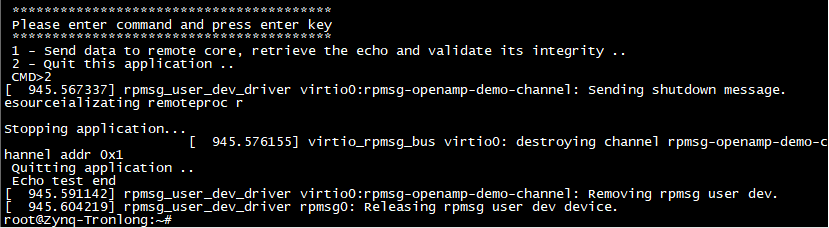

输入2,并按回车键退出测试。

图 8

执行如下命令,停止CPU1程序。

Target# echo stop > /sys/class/remoteproc/remoteproc0/state

图 9

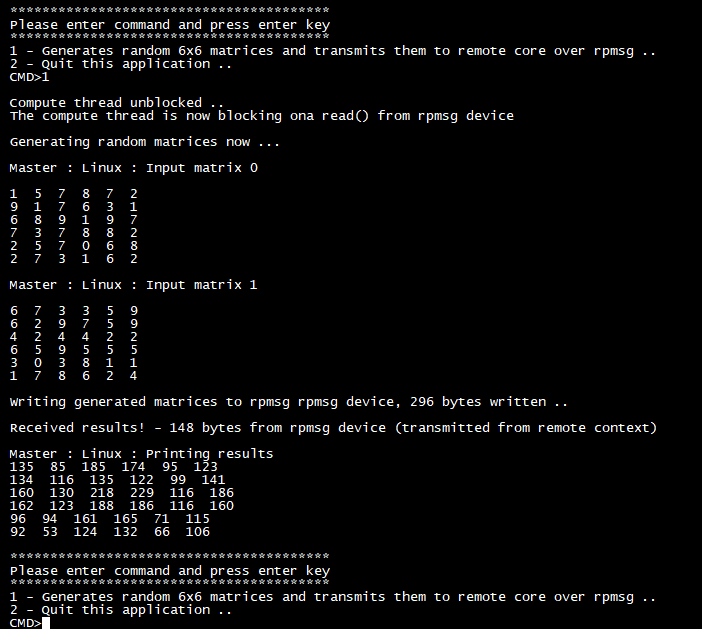

2、matrix_multiply案例

2.1 案例功能

案例功能:CPU0随机生成两个矩阵并使用RPMsg向CPU1发送数据,CPU1接收到数据后进行矩阵乘法运算,再使用RPMsg向CPU0回传运算结果,然后CPU0通过串口终端输出运算结果。

2.2 操作说明

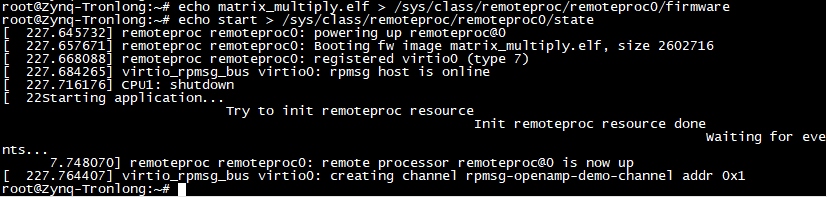

将CPU1裸机或FreeRTOS可执行文件复制到评估板文件系统“/lib/firmware/”目录下,并执行如下命令加载CPU1程序。

Target# echo matrix_multiply.elf > /sys/class/remoteproc/remoteproc0/firmware

Target# echo start > /sys/class/remoteproc/remoteproc0/state

图 10

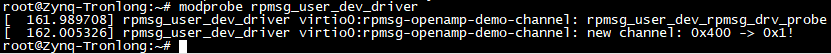

执行如下命令加载RPMsg驱动,并在“/dev/”目录下生成RPMsg设备节点。

Target# modprobe rpmsg_user_dev_driver

图 11

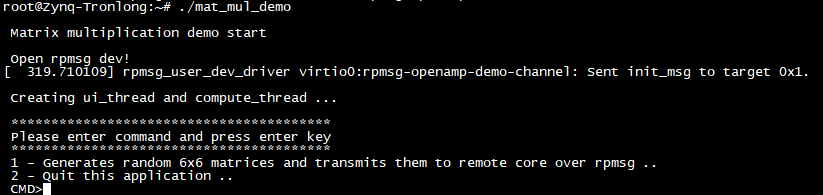

将CPU0应用程序可执行文件复制到评估板文件系统,并执行如下命令通过RPMsg与CPU1进行通信。

Target# ./mat_mul_demo

图 12

输入1,并按回车键进行测试。

图 13

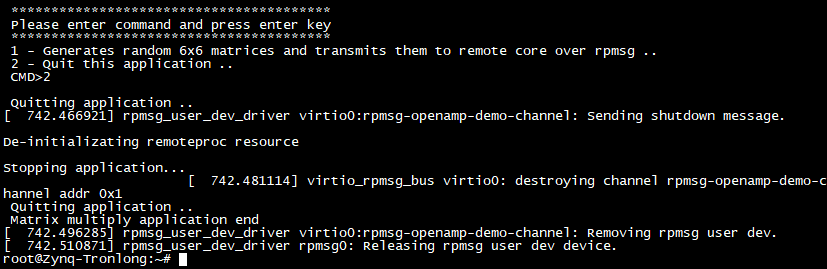

输入2,并按回车键退出测试。

图 14

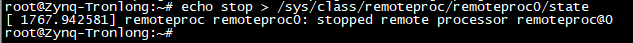

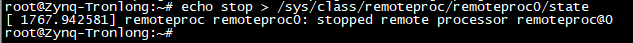

执行如下命令,停止CPU1程序。

Target# echo stop > /sys/class/remoteproc/remoteproc0/state

图 15

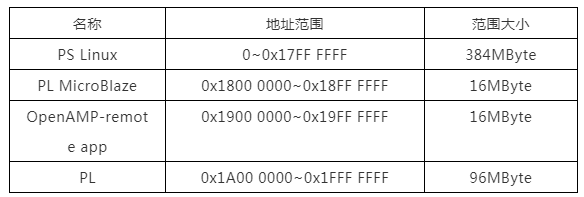

3、内存分配说明

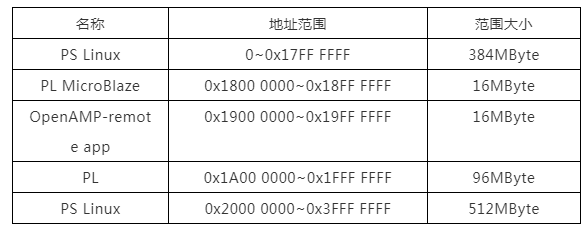

512MByte DDR容量版本核心板的内存地址分配如下:

表 1

1GByte DDR容量版本核心板的内存地址分配如下:

表 2

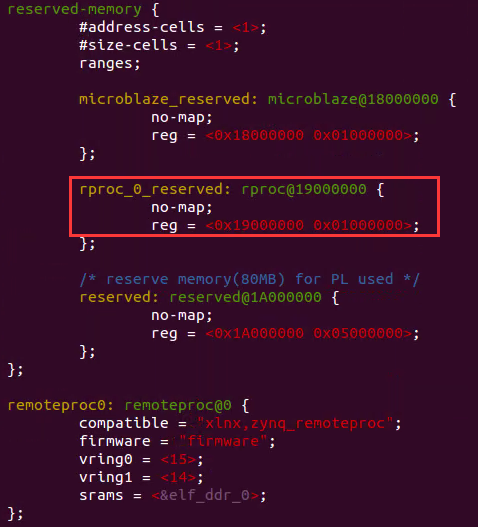

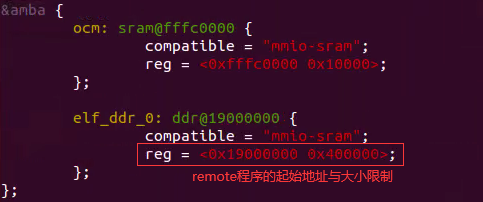

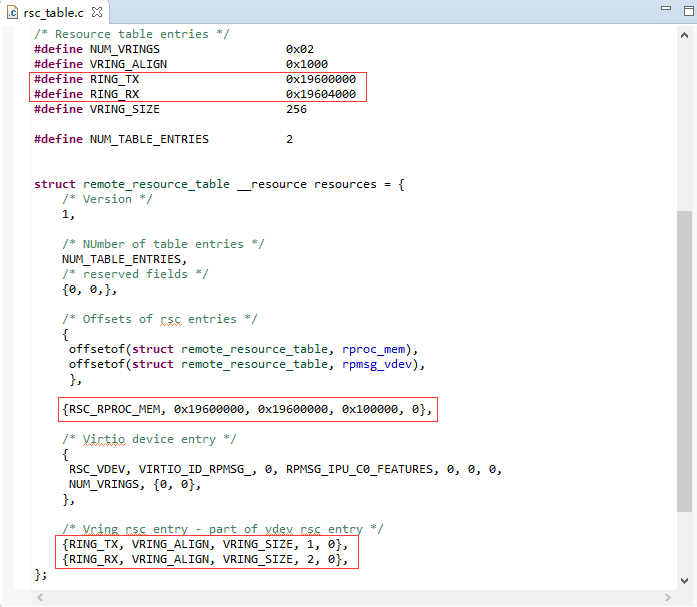

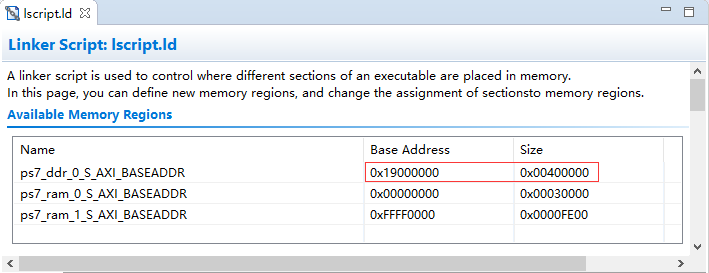

如需修改CPU1程序(OpenAMP-remote app)内存地址空间范围,可通过更改设备树文件tlz7x-easyevm-s.dts、资源表rsc_table.c及链接文件lscript.ld对内存地址空间进行重新分配。三者需同步修改并保持一致,以确保固件程序链接地址与设备树配置的elf_ddr_0对应。所使用的资源(内存和virtio设备资源)不能超出设备树文件配置的内存范围。

图 16设备树文件tlz7x-easyevm-s.dts配置

图 17设备树文件tlz7x-easyevm-s.dts配置

图 18 CPU1程序资源表rsc_table.c配置

图 19 CPU1程序链接文件lscript.ld配置

-

嵌入式

+关注

关注

4975文章

18228浏览量

287667 -

开发板

+关注

关注

25文章

4394浏览量

93704 -

Zynq-7000

+关注

关注

3文章

144浏览量

36594 -

核心板

+关注

关注

5文章

835浏览量

29105 -

工控板

+关注

关注

0文章

164浏览量

12866

发布评论请先 登录

相关推荐

简谈Xilinx Zynq-7000嵌入式系统设计与实现

AD9683的引脚如何与zynq 7015芯片中的JESD204 ip核端口对应相连?

适用于Xilinx Zynq UltraScale+ MPSoC应用的电源参考设计

嵌入式HLS 案例开发步骤分享——基于Zynq-7010/20工业开发板(4)

嵌入式HLS 案例开发步骤分享——基于Zynq-7010/20工业开发板(1)

xilinx ZYNQ7000系列基本开发流程之PS端

Xilinx ZYNQ双核ARM通信开发实例

Xilinx ZYNQ双核ARM通信开发实例

评论