GRE是Global Route Environment的缩写,中文意思为全局布线环境,运用具备阶层化意识的全面绕线引擎与图形式互连流程规划程序。通GRE技术在短时间就可以开发出包含众多互连总线与芯片引脚数的复杂且高速的设计组件。此外,运用GRE技术后便于工程师实现更佳的功能密度与系统效能最大化。Cadence这项系统互连设计解决方案,为PCB设计人员提供智能型规划和绕线的环境,节省大量的时间、增进功能密度并提升效能,同时也大幅降低成本。

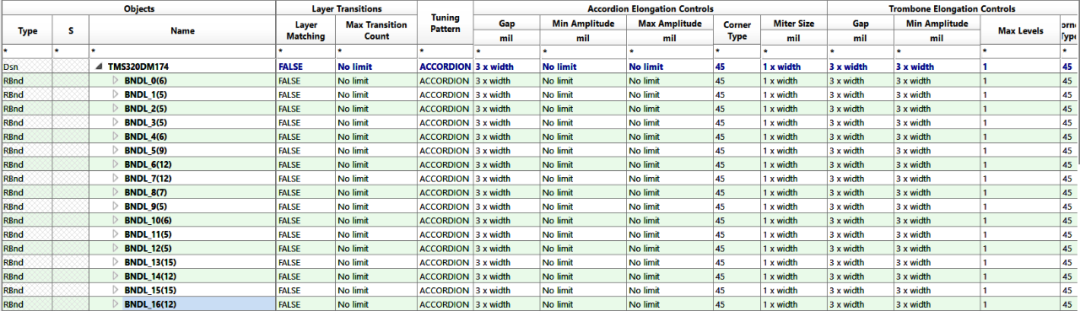

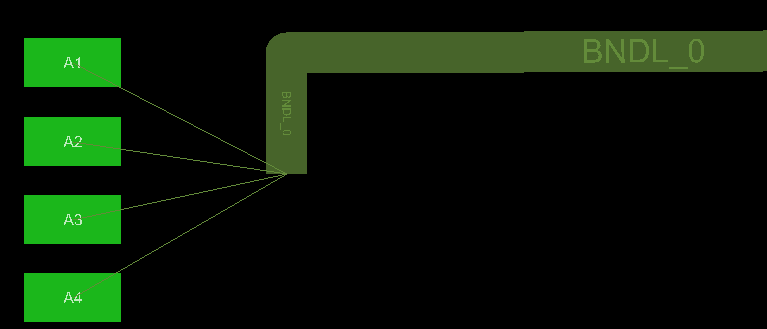

上期内容讲了全局布线GRE规划应用及参数设置,本期将通过4片DDR3中的1片为实例进行讲解,在Allegro中GRE处理的基本元素就是Bundle,详细讲解如何手动创建、自动创建、通过规则管理器来创建Bundle,并且编辑管理Bundle的详细操作。

教大家如何运用全局布线GRE规划应用技术提升智能绕线规划增强高密度PCB的设计效率。

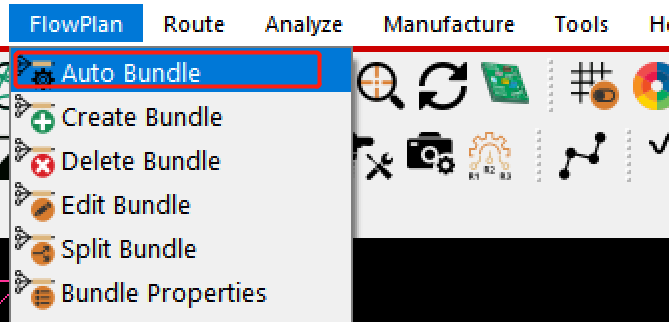

01自动创建Bundle

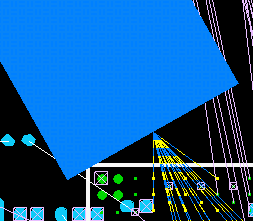

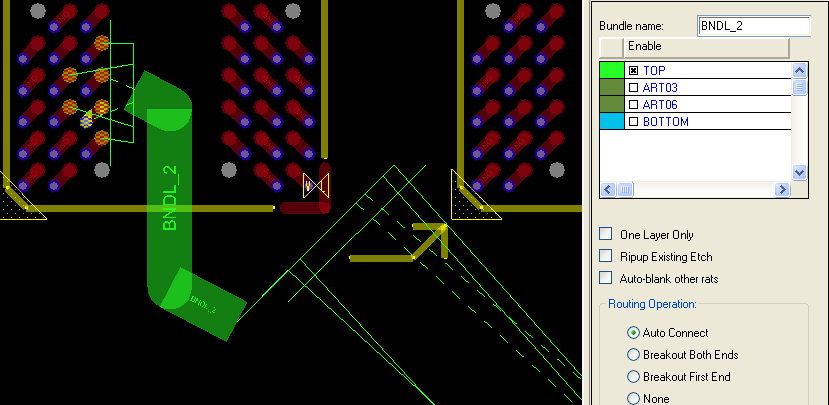

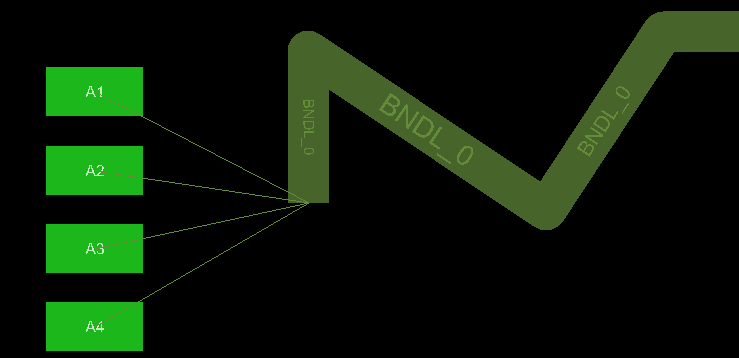

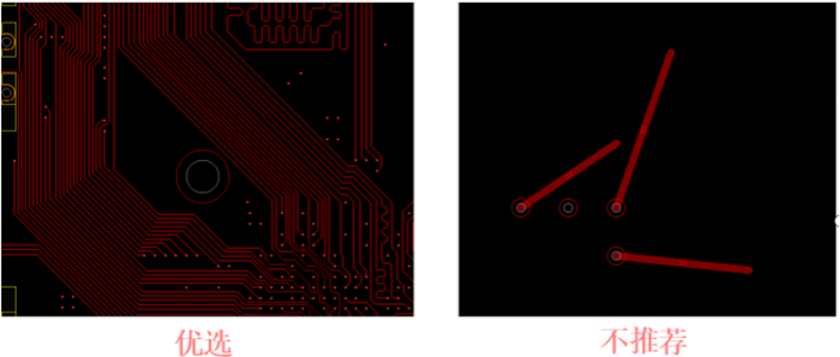

【1】在Flow Planning模式中,选择FlowPlan菜单—Auto Bundle命令,就可以按照GER的参数设置在整个PCB范围内创建Bundle,如下图1所示。也可以在工作区域内点击右键选择快捷菜单Auto Bundle命令自动创建Bundle。软件会根据设置的参数,按照布线的方便来自动创建Bundle,可以在布局完成以后使用Bundle来估计布线的区域位置是否够用,若不够的话,要先调整好位置后再进行布线,这样就可以避免布线后因位置不够要挪动元件的情况发生。

图1 执行Auto Bundle命令

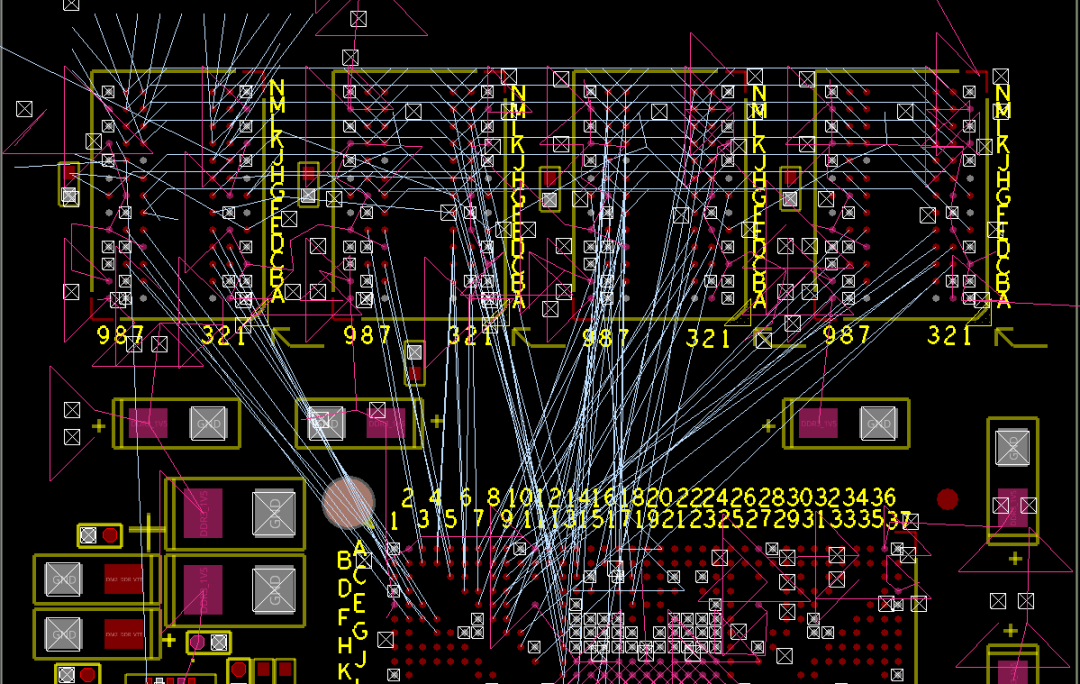

图2 执行Auto Bundle命令前的飞线显示

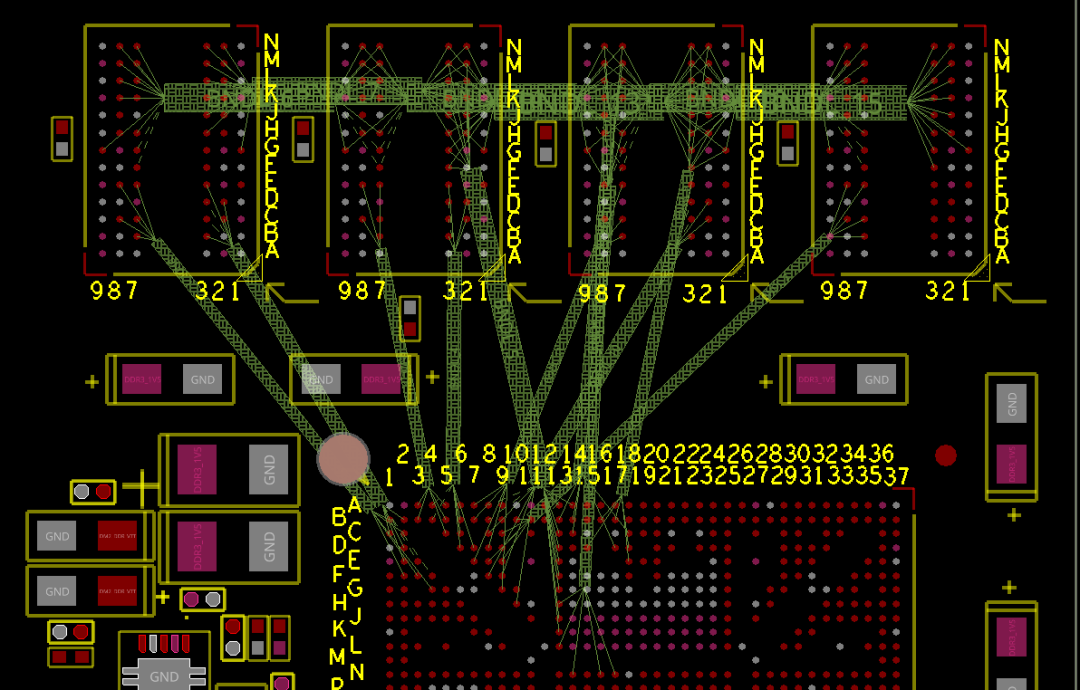

图3 执行Auto Bundle命令后创建Bundle

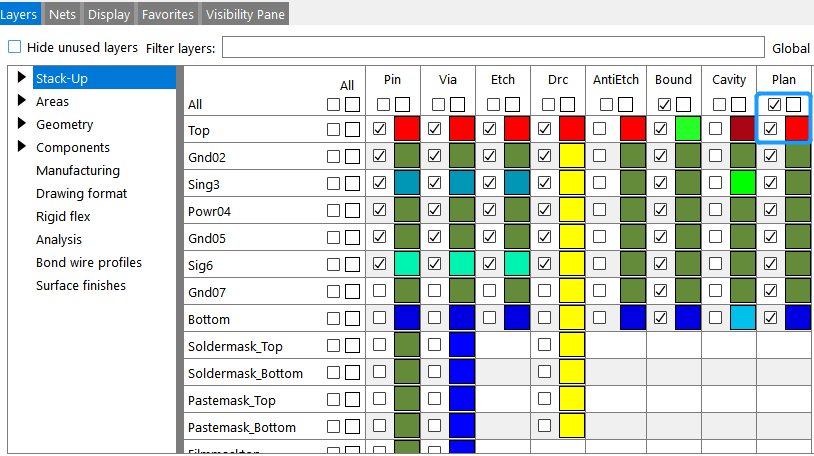

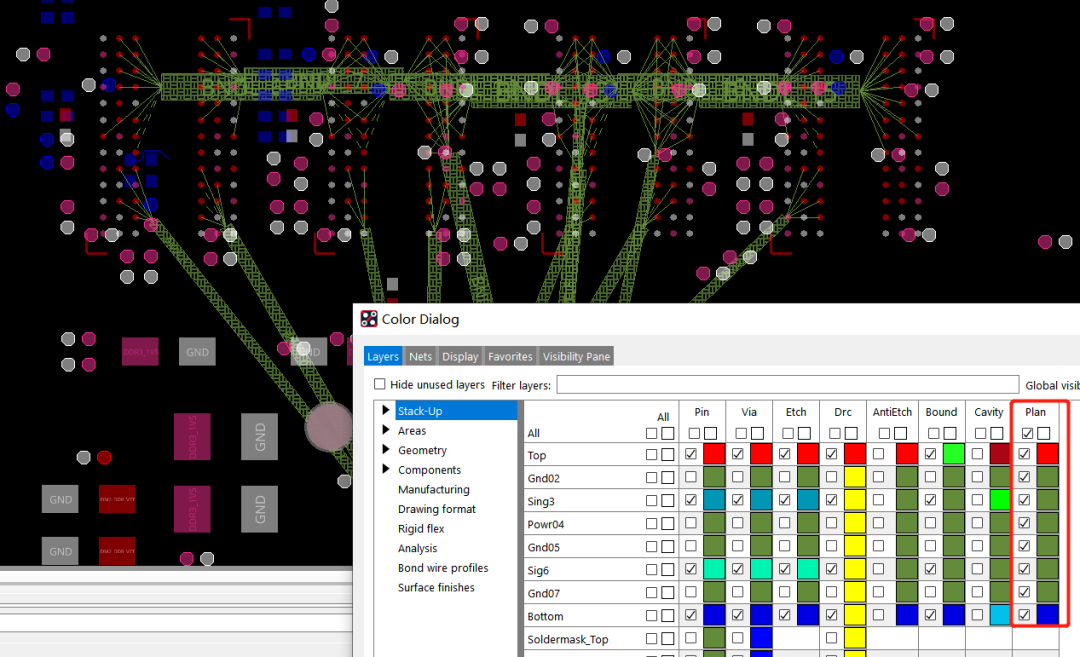

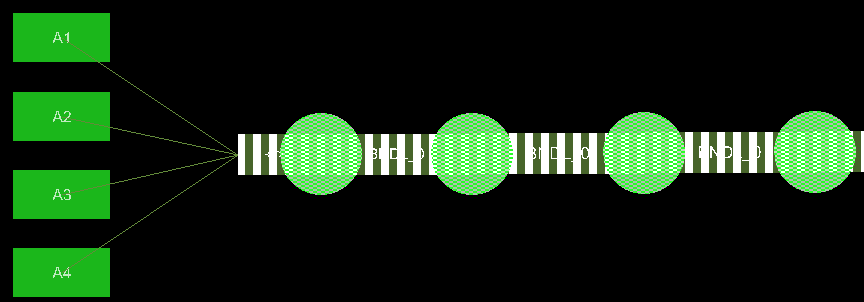

【2】Bundle的显示,有时候创建Bundle之后显示不出来,因为Bundle显示的层没有被打开。选择Display菜单--Color/Visibility命令打开Color窗口,如下图3所示。在Stack-Up--Plan中将Through All勾选后即可打开Bundle的显示(若创建的Bundle是放在Top层,那么在该处就需要勾选Top层的复选项后才能显示出来,其他层也是同样道理,在没有指定层的情况下,默认的Bundle会存在Through All)。如下图4所示。

02手工创建Bundle

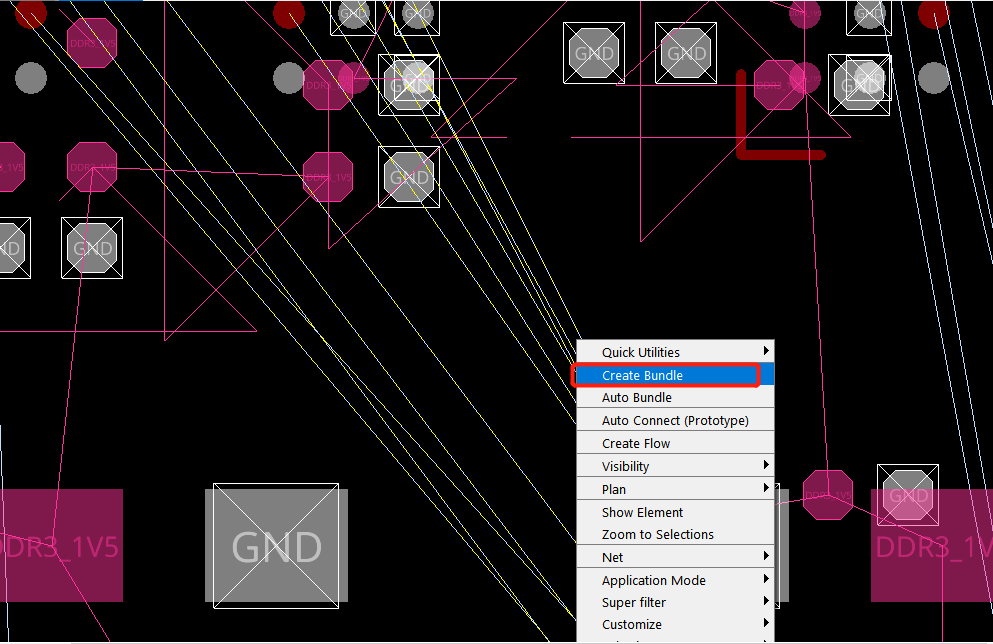

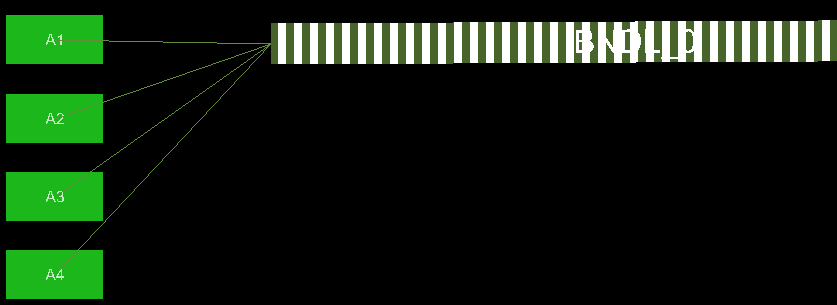

【1】在工作区域内,用鼠标框选要创建Bundle的网络飞线后,点击右键菜单中选择Create Bundle就可以创建当前框选飞线网络的Bundle。如下图5所示。手工创建Bundle的时候,可以将只需要进行选择的网络飞线显示出来,这样方便进行选择,避免使用鼠标在拖动的时候框选到其他不相关的网络飞线。

图5 手工创建Bundle

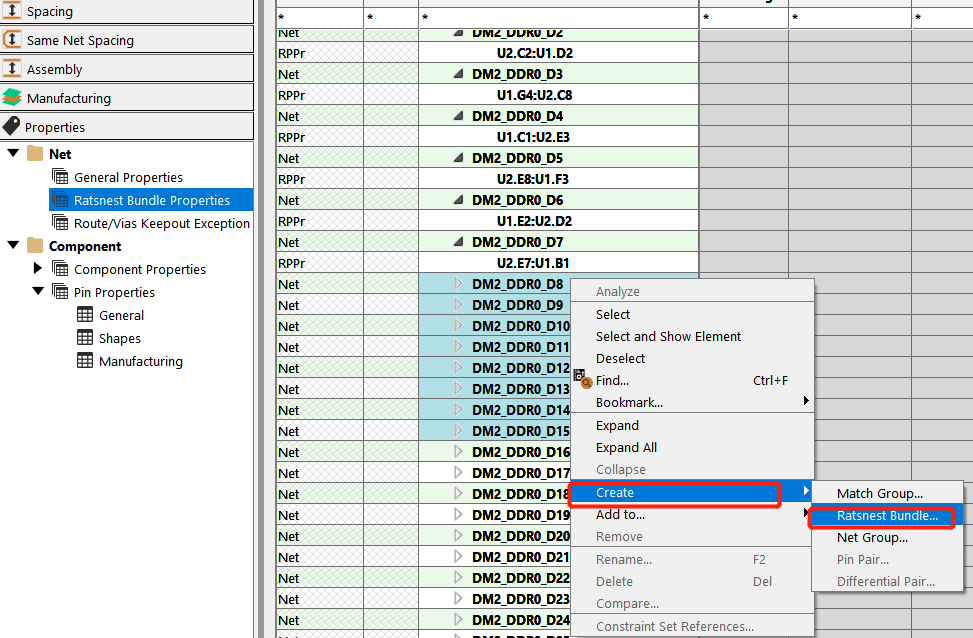

03通过规则管理器来创建Bundle

打开规则管理器选择Properties--Ratsnest Bundle Properties工作薄中选中要创建的网络,点击右键选择Ratsnest Bundle命令后,选中的网络将会创建Bundle,如下图6所示。

图6 通过规则管理器来创建Bundle04Bundle的编辑操作

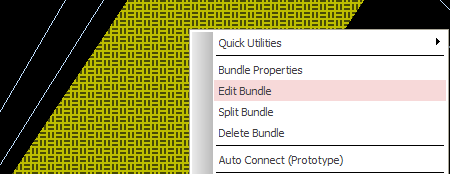

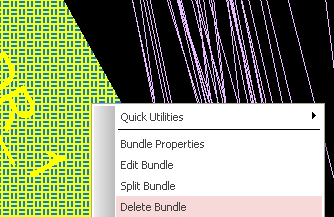

Bundle的编辑有三个命令分别是:Edit Bundle、Split Bundle、Delete Bundle,使用方法具体如下。

【1】Edit Bundle命令可以将Bundle之外的飞线加入到当前的Bundle中来。用鼠标选中需要增加飞线的Bundle,点击右键选择Edit Bundle命令,如下图7所示。然后用鼠标左键在想要增加到Bundle中的飞线上点击,被点击的飞线将会被加入到Bundle中,同时可以看到Bundle也变宽,如下图8所示。

图7 执行Edit Bundle命令

图8 加入飞线Bundle变宽

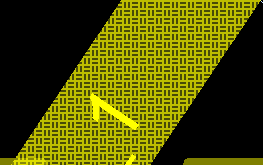

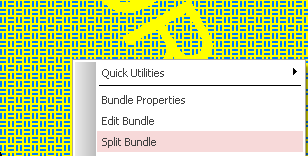

【2】Split Bundle命令可以将一个Bundle拆分成两个或者多个。用鼠标选中需要拆分的Bundle,点击右键选择Split Bundle命令,如下图9所示。然后用鼠标左键在需要拆分的Bundle内头部飞线上点击,此时被点击的飞线将被拆分出形成一个独立的Bundle,如下图10所示。

图9 SplitBundle命令

图10 拆分成两个的Bundle

【3】Delete Bundle命令用来删除当前选中的Bundle,返回飞线显示状态。用鼠标点击选中需要进行删除的Bundle,点击右键选择Delete Bundle命令,此时被选中的Bundle将会被删除,连接飞线返回飞线的状态显示,如下图11所示。

图11.1 删除前的Bundle显示

图11.2 执行Delete Bundle命令后飞线显示

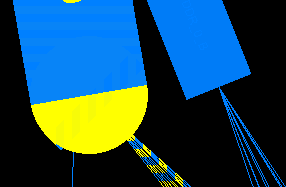

05规划Flow走线路径

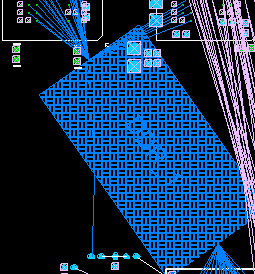

【1】Flow是Bundle的图形表现方式,Bundle的大小决定着Flow粗细和走线路径,包括层和层之间的转换。Bundle刚生产的时候,图形是空心网状的,定义了Bundle的Flow之后,也就是编辑了Bundle之后会变成实心的。如下图12所示。

图12.1 Bundle图形是空心网状

图12.2 Bundle之后Bundle会变成实心

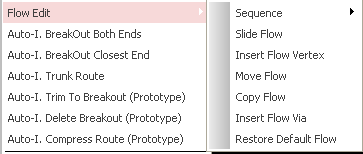

【2】Flow的操作,就如同普通布线一样,可以使用Move、Delete、Slide、Vertex命令,也可以增加过孔,修改走线的层等。所有的操作都在右键的菜单中选择命令,进入命令状态以后,用鼠标来对Bundle进行操作。如果觉得Flow规划比较乱或者存在错误想回到最初的Bundle的状态中去,可以选择Restore Default Flow命令,取消当前的规划,回到Bundle最初状态去。常用的操作命令如下图13所示。

图13 Flow的操作命令

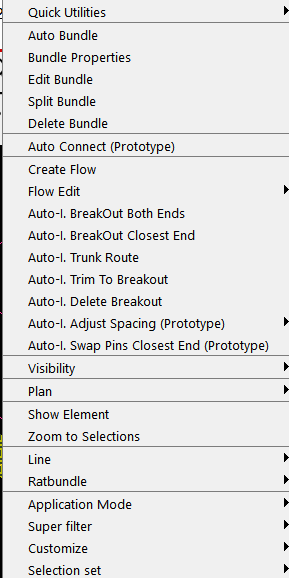

【3】选中Bundle后,右键选择Create Flow(Prototype)命令,可以给选中的Bundle 创建Flow布线规划。进入Create Flow命令以后在Option选项卡中,Bundle name文本框中显示为当前选中Bundle的名称,可以支持修改,直接在文本框中输入新的名称后用鼠标再次在工作区域内点击后,Bundle的名称将被修改。

Enable选项框中会列出当前电路板所有的电气层,勾选哪个电气层,表示创建Flow布线规划将放在那个层中,比如只勾选TOP层,表示创建Flow布线规划将存在于TOP层中。

复选项One Layer Only表示只在一个层进行规划,复选项Ripup Existing Etch表示拆掉其他的布线,复选项Ripup Existing Etch表示自动隐藏其他的飞线。

Routing Operation 选项组中用来选择当Flow布线规划完成以后将进行哪些操作,Auto Connect 表示自动信息布线连接,Breakout Both Ends表示将进行规划线头两端的出线顺序处理,Breakout First End表示将进行起始端出线线头的处理,None不操作,一般情况下选择None不操作即可。如下图14所示。

图14 Bundle name文本框当中的设置有修改

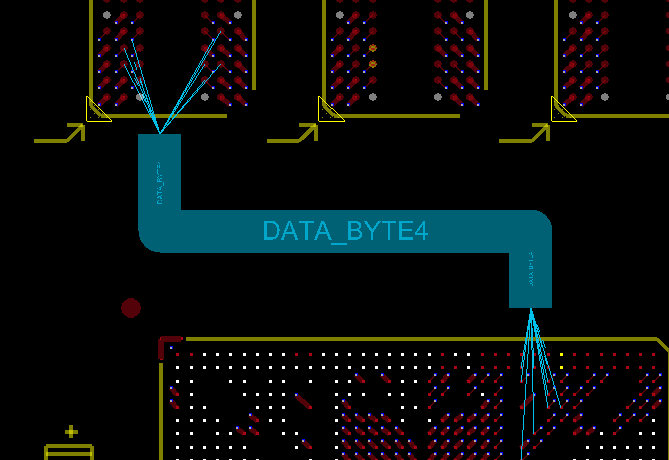

Create Flow的命令状态下,鼠标沿着DDR3和CPU布线的路径拉线进行布线规划,完成后的布线规划如下图15所示。

图15 DDR3和CPU进行布线规划

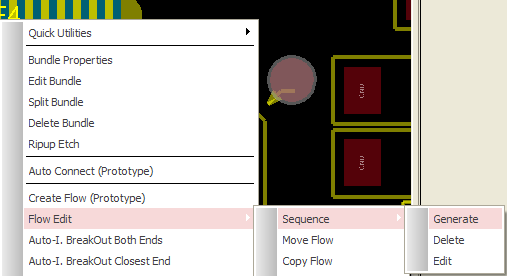

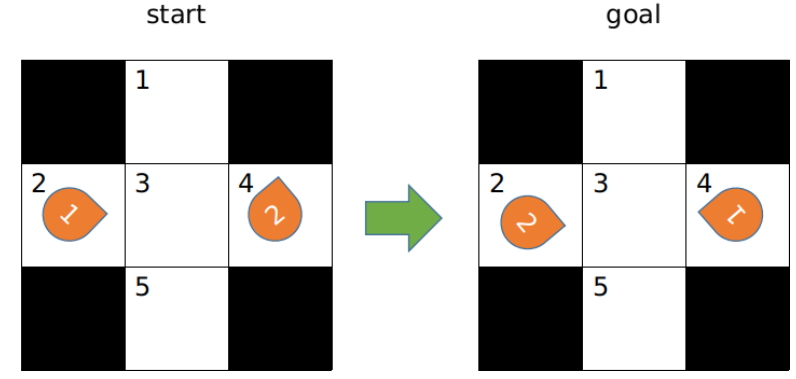

【4】选中Bundle后,右键选择Flow Edit--Sequence--Generate命令,将生成当前Bundle的Breakout Both Ends,系统自动会按照元件与过孔摆放位置对线两端飞线出线顺序进行调整。选择Delete命令后,将删除生成的Breakout Both Ends,如下图16所示。

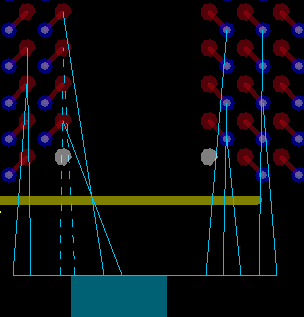

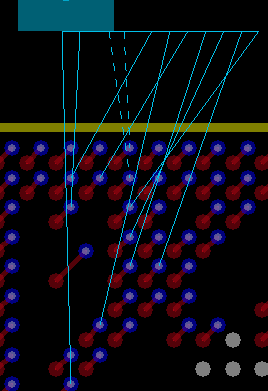

选择Edit命令后,可以进入两端飞线顺序的交换编辑状态,用鼠标分别点击不同的飞线,软件会根据点击的前后顺序来交换飞线显示。实线显示的飞线是当前层能布通的飞线,虚线显示的为当前层不能布通的飞线,另外出线的角度也可以使用Side Flow进行调整,可以按照布线的要求调整到合理满意为止。如下图17所示。

图17 Generate生成线序和编辑调整线序

如下图18所示,在当前的Bundle中共计有11根飞线网络,其中DDR3和CPU处均显示有9根实线,有2根虚线。这说明,在当前层中有9根线可以布通,有2根线布不通,这2根就要通过换层,增加过孔来处理。

此外当选中Edit命令后,用鼠标点击两端飞线进行交换的过程中,当点击一端之后,另外一端也会跟着交换。如下图19所示

图18 Breakout Both Ends的显示

图19 Breakout Both Ends的显示

【5】选中Bundle后,右键选择Slide Flow命令,可以对Bundle的布线规划路径进行编辑(直角线段编辑)。命令被选择后Bundle会跟在鼠标上,在合适的位置点击之后,就可以摆放下调整过的Bundle。当按住Shift键后拖动鼠标,Bundle可以按照直线的方式进行移动。如下图20所示。

图20 Slide Flow命令对调整规划路径

【6】选中Bundle后,右键选择Insert Flow Vertex命令,可以对Bundle的布线规划路径进行编辑(增加任意拐角编辑)。命令被选择后用鼠标在Bundle上点击,该处将会产生一个拐角,拖动鼠标将可以拖动出任意角的拐角。当按住Shift按后拖动鼠标,Bundle可以按照线的方式进行移动,不会产生任意拐角。如下图21所示。

图21 Insert Flow Vertex命令增加任意拐角

【7】选中Bundle后,右键选择Insert Flow Via命令,可以在Bundle的布线规划路径中插入Flow过孔。命令被选择后用鼠标在Bundle上点击,点击处将产生一个Flow 过孔,如下图22所示。

图22 规划路径中插入Flow过孔

【8】选中Bundle后,右键选择Move Flow命令,可以对Bundle的布线规划路径进行整体移动,如下图23所示。

图23 规划路径进行整体移动

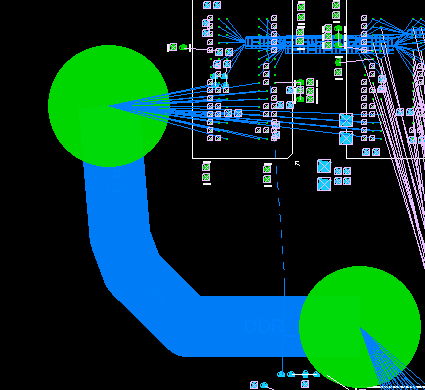

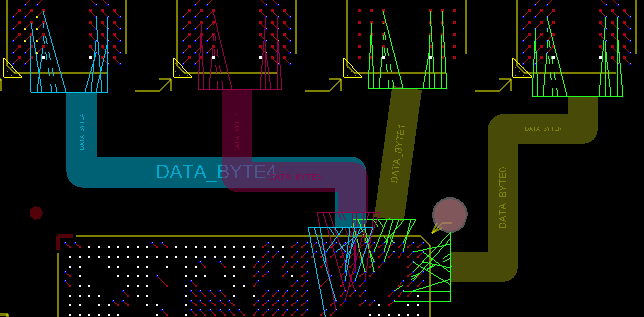

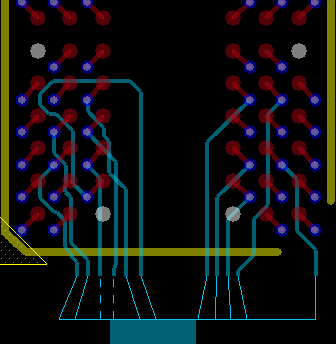

【9】4片DDR3数据线规划Flow走线路径后情况如下图24所示,右侧的两个芯片布线规划在内层,左侧的两片规划在Bottom层和Top层。

图24 DDR3数据线规划Flow走线路径

06Auto-I.Breakout Both Ends

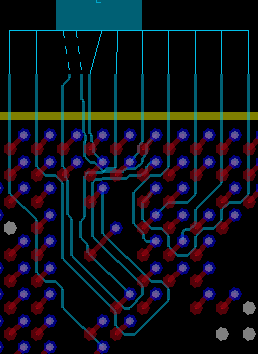

选中Bundle后,右键选择Auto-I.Breakout Both Ends命令,软件会根据当前Bundle两端飞线的顺序,尝试自动扇出(拉线)Bundle中的所有布线网络,所有引脚都会被扇出走线。注意如果是飞线中有交叉线,全部引脚不能扇出的情况下系统就不会自动100%的扇出所有飞线。

执行命令auto-I trunk route命令,系统就会按照设置的参数将中间的走线进行删除操作。若这些线是有差分或等长属性的话,系统就会按照设置的参数进行绕线操作,操作完成以后命令返回。当系统遇到无法完成的情况后就不会100%的执行,系统会自动执行到无法执行命令为止。完成后如下图25所示。

图25 Auto-I.Breakout Both Ends的所有布线网络布线

总结 通过上面的学习让我们看到了全局布线环境GRE的运用技巧,通GRE技术在短时间就可以完成包含众多互连总线与芯片引脚数的复杂且高速的设计组件设计。运用GRE技术后可以方便工程师在密度与系统效能最大化方面做出最快速的评估,为PCB设计人员提供智能型规划和绕线的环境,节省大量的时间、增进功能密度并提升效能,同时也大幅降低成本。阅读完这篇文章的小伙伴可以自己去试一试这个新功能,为己所用提高工作效率。另外需要本次讲解实例文件的小伙伴,可以点击打赏按钮,完成打赏后会有工作人员发放实例原始文件给您,精彩不容错过,期待您持续关注喔!

-

pcb

+关注

关注

4216文章

22446浏览量

385273

发布评论请先 登录

相关推荐

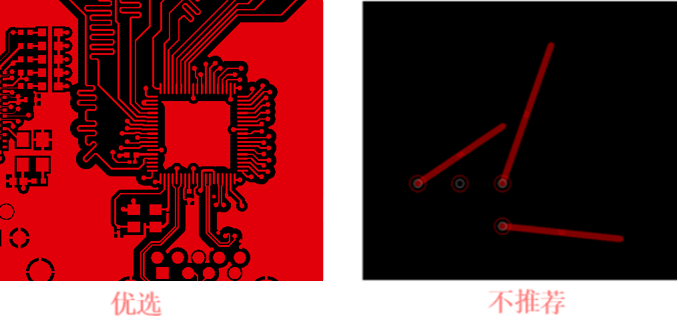

PCB设计必备:31条布线技巧

31条PCB设计布线技巧!

【PCB设计干货】DDR电路的PCB布局布线要求

【PCB设计必备】31条布线技巧

PCB设计中布线的要点总结

PCB设计必备:31条布线技巧!

PCB设计必备:31条布线技巧!

实例讲解 | 如何运用全局布线GRE规划应用技术提升PCB设计效率

实例讲解 | 如何运用全局布线GRE规划应用技术提升PCB设计效率

评论