近日,国家重大科研装备研制项目“超分辨光刻装备研制”通过验收。该***由中国科学院光电技术研究所研制,光刻分辨力达到22纳米,结合双重曝光技术后,未来还可用于制造10纳米级别的芯片。

中科院理化技术研究所许祖彦院士等验收组专家一致表示,该***在365纳米光源波长下,单次曝光最高线宽分辨力达到22纳米。项目在原理上突破分辨力衍射极限,建立了一条高分辨、大面积的纳米光刻装备研发新路线,绕过国外相关知识产权壁垒。

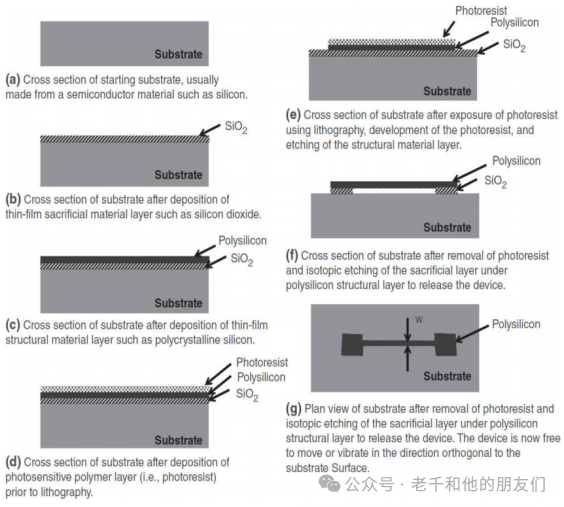

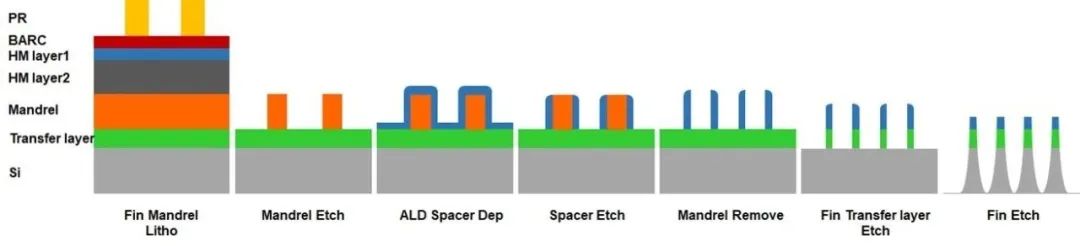

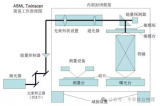

***是制造芯片的核心装备,我国在这一领域长期落后。它采用类似照片冲印的技术,把母版上的精细图形通过曝光转移至硅片上,一般来说,光刻分辨力越高,加工的芯片集成度也就越高。但传统光刻技术由于受到光学衍射效应的影响,分辨力进一步提高受到很大限制。

为获得更高分辨力,传统上采用缩短光波、增加成像系统数值孔径等技术路径来改进***,但技术难度极高,装备成本也极高。

项目副总设计师胡松介绍,中科院光电所此次通过验收的表面等离子体超分辨光刻装备,打破了传统路线格局,形成一条全新的纳米光学光刻技术路线,具有完全自主知识产权,为超材料/超表面、第三代光学器件、广义芯片等变革性领域的跨越式发展提供了制造工具。

据了解,这种超分辨光刻装备制造的相关器件已在中国航天科技集团公司第八研究院、电子科技大学、四川大学华西医院、中科院微系统所等多家科研院所和高校的重大研究任务中得到应用。

-

芯片

+关注

关注

462文章

53541浏览量

459200

发布评论请先 登录

基于飞腾CPU的安全计算机平台研制项目通过试验评审

【「芯片通识课:一本书读懂芯片技术」阅读体验】芯片怎样制造

纳米技术的发展历程和制造方法

我国超分辨光刻装备研制项目通过验收 未来可用于制造10纳米级别的芯片

我国超分辨光刻装备研制项目通过验收 未来可用于制造10纳米级别的芯片

评论