声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

33文章

1797浏览量

133148 -

硬件

+关注

关注

11文章

3555浏览量

68744 -

逻辑

+关注

关注

2文章

834浏览量

30052

发布评论请先 登录

相关推荐

热点推荐

阿斯顿马丁沙特阿美F1车队进站背后的Arm技术支持

在世界一级方程式(Formula One,以下简称 F1)锦标赛中,两秒钟足以决定比赛胜负。一次完美的进站需要极其精准的协同配合,从更换车轮到赛车驶出,每个动作都堪称瞬间完成。但如此高水准的精准度,仅靠人类本能很难实现。

利用 NucleiStudio IDE 和 vivado 进行软硬件联合仿真

本文利用NucleiStudio IDE 和 vivado 对 NICE demo协处理器进行软硬件联合仿真。

1. 下载demo_nice

发表于 11-05 13:56

【产品介绍】Altair PBS Professional HPC工作负载管理器和作业调度管理系统

AltairPBSProfessional行业领先的HPC工作负载管理器和作业调度管理系统PBSProfessional是一款快速、强大的工作负载管理器和作业调度管理系统,旨在提高生产

TPS92665-Q1汽车级LED矩阵管理器技术解析

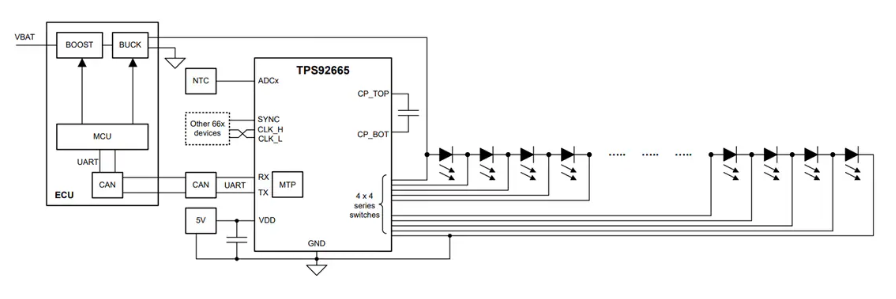

Texas Instruments TPS92665 LED矩阵管理器通过提供单独的像素级LED控制实现全动态自适应照明解决方案。该器件包括四个子串的三串联集成开关,用于旁路连接独立LED。通过单独的子串,该器件可以接受单个或多个电流源。

AMD Vivado ChipScope助力硬件调试

许多硬件问题只有在整个集成系统实时运行的过程中才会显现出来。AMD Vivado ChipScope 提供了一套完整的调试流程,可在系统运行期间最大限度提升对可编程逻辑的观测能力,助力设计调试。

K230设备管理器里面没有COM是怎么回事?

我的K230连接电脑后,设备管理器里面没有新的USB串行设备(COMx),电脑也没有弹出CanMV设备,我看设备管理器里面只有一个“其他设备-K230 USB Boot Device”有个三角形

发表于 08-04 08:04

WICED IDE 6.6.1.1怎样才能连接到自定义硬件?

)我们使用 JTAG?

设备启动的先决条件是什么? 有带启动选项的 ROM 启动加载器吗?

WICED-IDE 是否期望准确看到连接 Evalboard 时设备管理器显示的 WICED-USB

发表于 07-09 07:01

F1宣布与联想集团深化合作

包括F1在内的体育赛事不仅是速度、体能的较量,更是尖端技术的极限测试场。置身于F1争分夺秒的严苛环境,其背后的设备能力与澎湃算力也迎来了另一场“竞速”,而我们,在实战中经受住了这场考验!

ADI创新电源管理器件介绍

在电子系统中,电源管理器件担负着电能的变换、分配、监测等工作,为系统中不同的用电组件提供持续充足的能量,确保其稳定可靠工作,是不可或缺的存在。因此,对于硬件工程师来说,电源管理器件的选型和应用,是产品开发中重要的一环。

F1®与亚马逊云科技联合推出全新在线体验 车迷可亲手打造专属赛道

北京 ——2025 年 5 月 22 日 世界一级方程式锦标赛®(以下简称:F1®)在其成立75周年之际,与亚马逊云科技联合推出了全新数字互动体验,使其车迷可自主创建、定制并分享其专属F1赛道

发表于 05-22 11:40

•1401次阅读

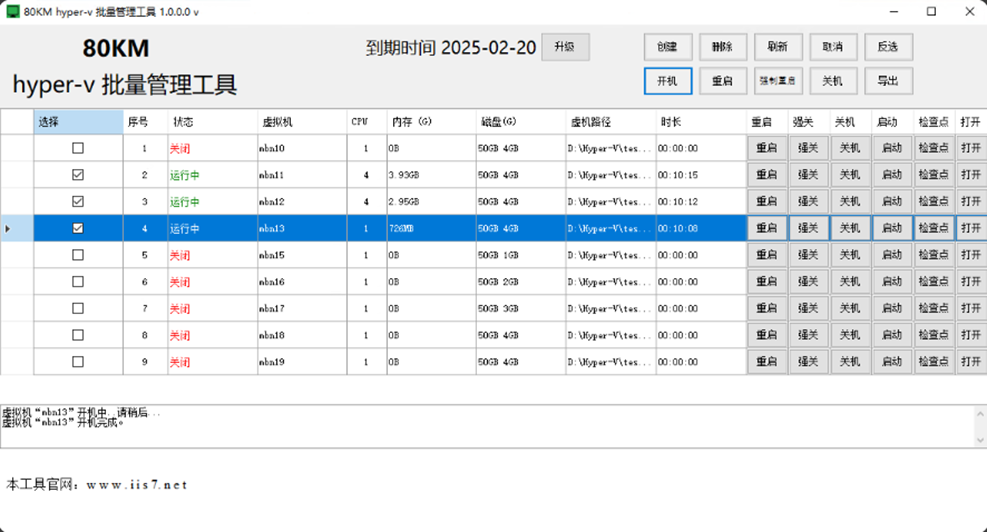

hyper管理器,Hyper管理器:管理工具使用指南

随着大数据、云计算等新兴技术的不断发展,数据的规模呈指数级增长。在这样的背景下,批量管理工具的价值愈发凸显,它成为了我们在数据管理领域的重要利器。今天就为大家介绍Hyper管理器:管理

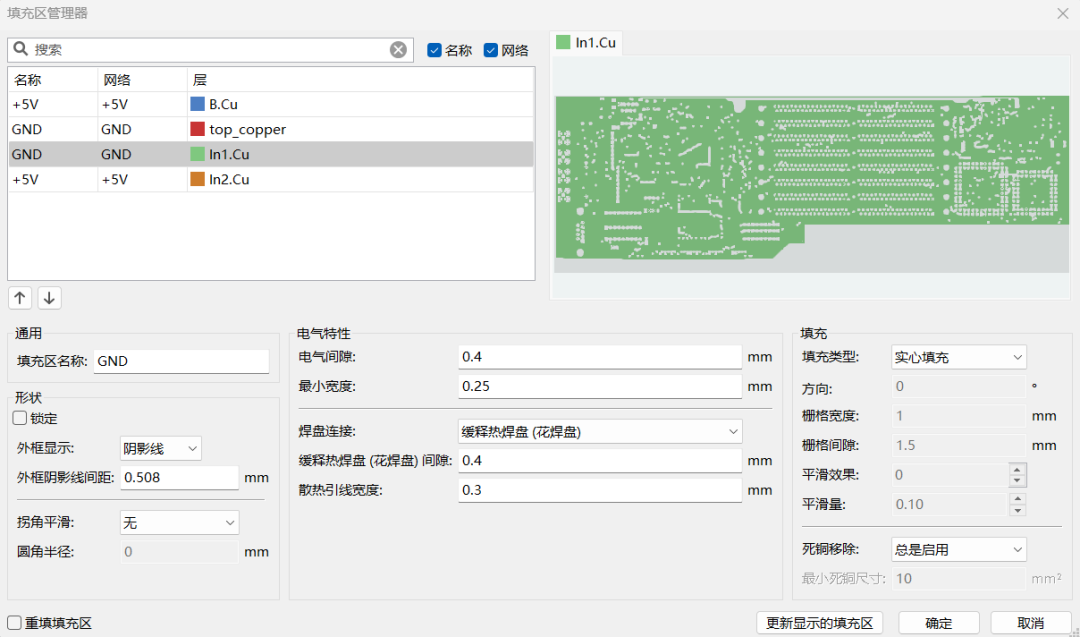

KiCad 9 探秘(五):敷铜管理器

管理 PCB 中所有的敷铜区域。包括以下操作: 查看敷铜的详细属性 对敷铜进行命名或修改敷铜的名称 修改敷铜的优先级 修改选定敷铜的特性(如电气间隙、最小宽度、热焊盘模式等) 更具修改的属性重新敷铜 敷铜管理器怎么用? 打开PC

Vivado Design Suite用户指南:逻辑仿真

电子发烧友网站提供《Vivado Design Suite用户指南:逻辑仿真.pdf》资料免费下载

发表于 01-15 15:25

•0次下载

TSW14J56EVM无论是上电后,还是上电前将usb线与电脑连接,设备管理器都无法找到该设备,为什么?

TSW14J56EVM无论是上电后,还是上电前将usb线与电脑连接,设备管理器都无法找到该设备,打开HSDC软件显示没有设备。但是换成新采购的同样的开发板,用同样的线和与同一台电脑连接,设备

发表于 12-13 06:42

如何使用Vivado硬件管理器连接F1进行定制逻辑设计

如何使用Vivado硬件管理器连接F1进行定制逻辑设计

评论