无论用做独立的处理单元,或者与辅助处理器联合使用,SoC FPGA器件均可以改善嵌入式处理的安全性。虽然可以利用专用安全器件来构建嵌入式处理器模块,实施监测和静态密匙存储,然而,整合系统关键功能的SoC FPGA器件若能提供安全特性,便可以提供更大的安全性、灵活性和更好的性能。

在嵌入式设计中,Linux日益流行。随着32位计算成为常见商品,Yocto等项目使得用于嵌入式应用和基于Linux的系统的创建、开发,以及维护变得更加容易,使得Linux系统的流行性可能会进一步增长。Linux使得OEM厂商变得更像初创企业,其灵活的硬件开发团队通过使用操作系统来提取底层的硬件细节,可以加快上市速度。尽管Linux系统具有优势,然而,如果没有合适的方法来启动其嵌入式处理器,便会易于受到rootkit攻击,对于将会创建数十亿个新的潜在不安全端点的新兴物联网来说,Rootkit特别构成重大威胁。

一般而言,rootkit试图接入特权(根)模式,同时躲避系统恶意软件检测工具。恶意软件也可能试图通过修改系统的启动过程,把自己安装系统以进入持久状态。如果成功,恶意软件感染便是永久的,或者通过上电循环持续,自此便可以为所欲为,包括记录击键、形成僵尸网络、收集个人信息,以及实施未经授权的服务。一旦系统受到感染,可能需要重新安装整个操作系统。

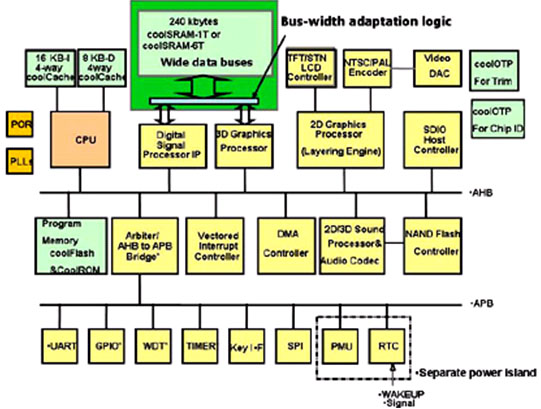

问题从嵌入式处理器开始,其启动通常如图1所示。在上电时,片上ROM将从外部非易失性存储器取得启动加载程序。启动加载程序是专用的,并且在启动期间对处理器进行配置以满足特定的应用需求。时钟、缓存、存储器控制器,以及外设均进行配置。一旦处理器完成初始化,就从外部非易失性存储器取得应用程序,有时进行解压缩,并且复制到应用程序开始之处的快速外部易失性存储器,让程序开始运行。

图1 嵌入式启动过程

在启动过程中,恶意软件有机会试图修改嵌入式系统的启动程序bootloader。如图2所示为嵌入式Linux系统的典型框图,UBOOT、Linux内核和应用程序层均存储在易于读取的非易失性存储器中。

图2 嵌入式Linux系统

保护启动过程的唯一方法,是使用一个确信它始终以预期方式运行的组件来提供保护。作为系统组件,这种信任根(root-of-trust)支持了系统、软件和数据完整性和保密性的校验,以及内部和外部实体的信任扩展。这是创建所有其它安全层的基础,它的密匙必须一直保密,而且之前的启动过程不可改变,这是十分重要的。在嵌入式系统中,信任根与其它系统组件共同工作,以期确保只有经过授权的代码来安全地启动主处理器,从而将信任域扩展到处理器及其应用。通过使用加密技术,可以扩展信任域以涵盖所有重要的系统组件,甚至通过本质上不安全的网络将数个信任系统捆绑在一起。

虽然许多较新的处理器具有支持安全启动的专门特性,然而处理器芯片安全启动的固有支持远不普及,通常需要一个多芯片解决方案。一个更好的解决方案是基于闪存工艺的FPGA器件,它们可以在多芯片嵌入式系统中提供最佳的信任根器件,显著提升主嵌入式处理器所运行的代码的可信性。

基于闪存工艺的解决方案本质上更加安全(它们一经编程,关键的信息永不丢失),而且今天基于闪存工艺的 SoC FPGA解决方案还具有数项附加的先进安全特性,包括片上振荡器、用于加密服务的加速器、安全密匙存储、真正随机数发生器、在安全的嵌入式Flash memory(eNVM)中的片上启动代码存储,以及使能外部处理器高速安全启动的高速串行外设接口(SPI)。这些器件还具有超越较早期解决方案的更强大的设计安全性,并且包含抵御差异化功率分析(DPA)技术的防篡改措施。结合嵌入式Linux CPU,它们能够有效地用于防止恶意软件试图修改嵌入式系统的启动程序。

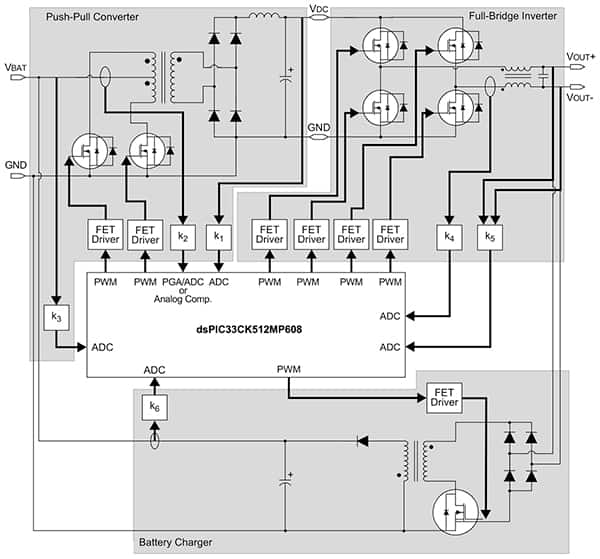

图3所示为可以用于安全启动的基于闪存工艺的SoC示例,美高森美SmartFusion2 SoC器件中的eNVM用于存储UBOOT,其FPGA架构则实现高速的SPI接口。CPU并不知悉SoC位于其和SPI闪存之间。在上电时,SoC将UBOOT的SPI读取请求从内部eNVM导向CPU,而后,CPU经过正常的UBOOT启动过程,并且从外部SPI闪存取得应用镜像的剩余部分,在后一个阶段中,SoC用作外部存储器的管道,并且将应用镜像传送给CPU。SoC及其内部eNVM仅可使用经过认证的加密位流进行编程,这一位流仅可由SoC的FPGA开发环境来建立。位流文件格式是专有的,并且不提供给任何人,并且具有从Cryptography Research Incorporated(现为Rambus)授权许可的专利保护措施,可以抵御DPA侧道攻击。换句话说,恶意软件试图写入快闪的唯一途径是具有设计用于该SoC并备有合适的加密和用户定义密匙的位流。

图3 SmartFusion2器件用于存储UBOOT

为了确保安全的多级启动,在提供和执行代码之前必须先进行验证,这是必不可少的,这可确保不会出现搅乱或损坏各阶段的启动,并且可以使用对称或非对称密匙加密技术来进行。更好的是,使用对前一个阶段的连续反馈来确认在启动加载期间没有发生篡改。如果所有的防篡改(AT)监测器确认环境安全,随后的各个阶段便可以继续执行。

今天的SoC FPGA可以独立提供运行时间监测和校正行动,有需要时也可以提供惩罚。为了这样做,所有的应用程序代码将存储在SPI快闪中,而且可加密。SoC器件将在每个阶段对代码进行真实性检查和解密 (如果需要),并且通过MPU-to-FPGA SPI接口进行请求时,把它们馈入主MPU。为了增加安全性,启动加载程序代码将会存储在SoC FPGA的eNVM中。

在上电之后,FPGA将保持主MPU在复位状态,直到它完成自已的完整性自我测试。在准备好时,它会释放复位。MPU将被配置成从通向FPGA的接口启动(例如通过SPI接口)。FPGA用作SPI从器件,在MPU复位之后,将向MPU提供所请求的Phase-0启动代码,假设MPU本身不支持安全启动,挑战则会是将某些代码载入MPU中并且高度确保它未被篡改。

如果各个项目均没有问题,启动过程将会连续将通过确认的代码载入MPU的SRAM中,这将包括发起下一阶段的所需代码,以及包括一个通过确认的RSA 或者 ECC公共密匙。一旦MPU SRAM中的代码获得信任,便可以部署附加的安全措施,比如使用公共密匙方法来建立分享的密匙,以及使用分享的密匙,对FPGA和MPU之间传输的所有后续导引代码进行加密。此外,也可以将系统所有的硬件组件捆绑在一起加密,使得系统中必须具备初始系统的所有组件才可以运作。

此外,SoC可以提供模块环境情况的实时监控,比如温度、电压、时钟频率和其它因素。FPGA架构可以通过安全的配置,提供I/O给外部篡改传感器和侵入检测器。SoC通过它们来感测,防止来自已知漏洞的攻击,这些攻击会施加异常条件来提取关键的信息。只要通过合适的设计,便可以达到更高的安全水平。

-

处理器

+关注

关注

68文章

20150浏览量

247270 -

嵌入式

+关注

关注

5186文章

20155浏览量

328968 -

soc

+关注

关注

38文章

4516浏览量

227652

发布评论请先 登录

嵌入式闪存技术助力智能汽车接口的实现

嵌入式闪存助力智能汽车接口应用实现

基于闪存工艺的SoC FPGA器件实现安全启动设计

如何实现嵌入式ASIC和SoC的存储器设计?

SOC嵌入式相关资料推荐

基于ARM-μCLinux嵌入式系统启动引导的实现

使用新SRAM工艺实现嵌入式ASIC和SoC的存储器设计

如何使用 DSC 和 MCU 确保嵌入式系统安全

基于闪存工艺的SoC实现嵌入式系统安全启动的设计

基于闪存工艺的SoC实现嵌入式系统安全启动的设计

评论