半导体产业链竞争格局与国产化进程发展分析

半导体产业作为全球科技竞争的战略制高点,其自主可控能力直接关系国家科技安全与产业竞争力。在全球产业链重构与技术竞争加剧的背景下,我国半导体产业的发展路径与突破方向备受关注。本文将从产业链各环节的竞争格局、技术壁垒、国产化瓶颈及未来突破方向展开系统性分析。

一、产业链各环节竞争格局与技术壁垒

(一)上游:核心技术与设备材料被美欧日垄断,国产化率亟待突破

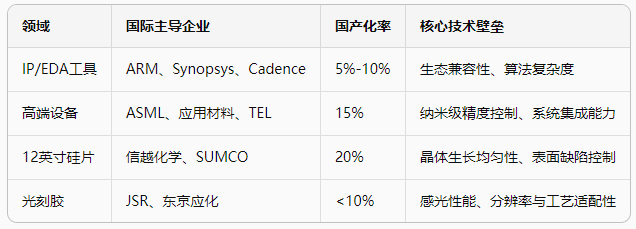

上游是半导体产业链技术壁垒最高的环节,IP、EDA工具、设备及材料基本由美欧日企业主导,国产化率普遍低于20%,具体表现为:

1. IP与EDA工具:美国企业绝对垄断,生态壁垒难以突破

市场格局:美国企业占据全球90%以上市场份额,如ARM(移动芯片架构)、Synopsys(EDA工具)、Cadence(设计软件)等。

国产化率:仅5%-10%,国内企业(如华大九天、芯原股份)仅能覆盖部分细分工具,全流程自主可控能力不足。

技术难点:

生态耦合性:需与芯片设计流程、制造工艺高度适配,新工具需通过长期验证才能被行业接受;

算法复杂度:EDA工具涉及数亿晶体管的布局布线优化,算法精度直接影响芯片性能与功耗。

2. 设备:高端市场被荷美日主导,高精度制造成最大瓶颈

市场格局:荷兰ASML垄断EUV光刻机市场,美国应用材料、泛林半导体,日本Tokyo Electron(TEL)占据刻蚀、沉积等核心设备领域80%以上份额。

国产化率:整体约15%,28nm及以上成熟制程设备国产化率约30%,但14nm以下先进制程设备仍不足5%。

技术难点:

EUV光刻机:反射镜需达到“原子级光滑”(表面粗糙度<0.1nm),光学系统需控制万亿分之一秒的激光脉冲精度;

刻蚀设备:需在7nm制程中实现纳米级图案转移,单次刻蚀误差需小于1nm。

3. 材料:日本企业主导高端市场,纯度与均匀性要求严苛

市场格局:日本信越化学、SUMCO占据全球70%的高端硅片市场,JSR、东京应化垄断光刻胶领域;德国巴斯夫、美国陶氏化学在电子特气领域领先。

国产化率:12英寸硅片约20%,光刻胶、电子特气等关键材料仅为个位数。

技术难点:

超高纯度:电子级多晶硅纯度需达到99.999999999%(11个9),任何杂质都会导致芯片失效;

批次稳定性:同一批次材料的厚度、均匀性误差需控制在0.1%以内,满足大规模量产需求。

表:上游关键领域国产化率与国际主导企业对比

(二)中游:设计与制造环节技术壁垒高,高端产品国产化任重道远

中游是产业链的核心制造环节,芯片设计与晶圆制造技术壁垒突出,高端产品国产化率仍处于较低水平。

1. 芯片设计:结构性分化明显,高端产品依赖进口

行业特点:轻资产、高研发投入(年均研发费用率>20%),需前端架构设计与后端物理实现协同突破。

技术难点:

全芯片仿真:需处理数十亿晶体管数据,单次仿真耗时可达数周;

验证成本:7nm芯片一次流片成本超5000万美元,验证周期占设计总周期的60%以上。

国产化率:

优势领域:通信芯片(如华为海思麒麟系列)、中低端MCU(微控制单元)国产化率约50%;

短板领域:高端GPU(图形处理器)、FPGA(现场可编程门阵列)、车规级SoC(系统级芯片)国产化率不足10%,市场被英伟达、赛灵思、高通等垄断。

2. 晶圆制造:先进制程差距显著,成熟制程加速替代

市场格局:台积电占据全球56%的高端制程(7nm及以下)市场份额,三星、英特尔紧随其后;成熟制程(28nm-90nm)竞争激烈,我国中芯国际、华虹半导体已实现规模化量产。

国产化进展:

成熟制程:28nm工艺良率提升至90%以上,产能占全球15%;

先进制程:14nm工艺进入风险量产阶段,但良率(约70%)与台积电(95%+)差距显著,7nm及以下制程尚未突破。

核心瓶颈:

工艺复杂度:先进制程需整合EUV光刻、3D堆叠等技术,单晶圆制造步骤超1000道;

设备配套:14nm以下制程所需的EUV光刻机、原子层沉积(ALD)设备等仍依赖进口。

(三)下游:封测领域实现“从跟跑到领跑”,高端化转型成关键

下游封装测试是我国半导体产业的优势环节,但高端封装技术与核心设备仍存短板。

1. 竞争格局:传统封装优势显著,全球份额超50%

市场地位:长电科技、通富微电、华天科技跻身全球封测企业前十,合计占据全球38%的市场份额;

国产化率:传统封装(DIP、SOP)达70%,中高端封装(BGA、CSP)约50%。

2. 技术转型:从“劳动密集型”向“技术密集型”升级

发展方向:2.5D/3D先进封装(如Chiplet)成为主流,通过多芯片堆叠提升芯片性能,可替代部分先进制程需求;

技术难点:

亚微米级对准:芯片间互联精度需控制在0.5μm以内,误差过大会导致信号延迟;

系统级测试:需同时验证多芯片协同工作稳定性,测试成本占封装总成本的40%以上。

高端短板:先进封装国产化率仅30%,焊线机(国产化率5%)、AOI检测设备(10%)等关键设备依赖进口(日本K&S、美国泰瑞达)。

二、国产化进程的核心瓶颈

我国半导体产业从“能用”向“好用”“先进”迈进的过程中,面临四大核心瓶颈:

(一)光刻机:先进制程“卡脖子”的核心设备

技术壁垒:EUV光刻机是7nm及以下制程的“必需品”,全球仅ASML能量产,单台售价超1.2亿美元,且需全球5000多家供应商协同配套;

国内差距:上海微电子已实现90nm DUV光刻机量产,但EUV光刻机的光源(波长13.5nm)、光学系统等核心部件仍未突破,预计2030年前难以实现国产化替代。

(二)EDA全流程工具:芯片设计的“操作系统”

垄断现状:Synopsys、Cadence、Mentor(被西门子收购)占据全球95%的EDA市场份额,我国设计企业超80%的工具依赖进口;

生态困境:国产EDA工具需兼容国际主流设计流程,而行业标准由国外企业主导,新工具难以进入主流供应链。

(三)IP架构:高端芯片设计的“地基”

主导格局:CPU领域x86架构(英特尔、AMD)、ARM架构(移动设备)垄断市场,GPU领域英伟达CUDA架构形成生态壁垒;

自主探索:RISC-V开源架构成为突破口,但生态成熟度不足,全球开发者仅为ARM的1/5,高端芯片设计仍需依赖国外IP授权。

(四)先进制程工艺:晶圆制造的“珠穆朗玛峰”

差距量化:台积电已量产3nm工艺,良率超90%,我国中芯国际14nm良率约70%,且产能仅为台积电的1/10;

工艺难点:FinFET(鳍式场效应晶体管)、GAA(全环绕栅极)等先进结构设计需突破材料科学与精密制造极限,单道工艺研发成本超10亿美元。

三、挑战与潜力:在技术攻坚中把握发展机遇

尽管面临诸多挑战,我国半导体产业已在部分领域实现突破:下游封测确立全球优势,中低端芯片设计与制造形成规模化产能,国产化替代从“单点突破”向“产业链协同”演进。未来需聚焦三大方向:

(一)长期研发投入:突破“卡脖子”技术

重点领域:光刻机核心部件(光学系统、精密机械)、EDA全流程工具、高端硅片与光刻胶;

创新模式:构建“产学研用”协同体系,如中科院微电子所联合中芯国际攻关14nm工艺,华为海思与国内EDA企业共建自主设计平台。

(二)高端化转型:从“中低端替代”到“高端突破”

产品升级:在AI芯片、车规级MCU等高端领域加大投入,如寒武纪思元系列GPU、地平线征程系列车规芯片已实现商业化落地;

制造协同:推动Chiplet技术产业化,通过多芯片异构集成绕过先进制程限制,中芯国际已联合长电科技开发2.5D封装方案。

(三)生态建设:培育自主技术体系

开源生态:依托RISC-V架构构建自主芯片生态,国内企业(如阿里平头哥、华为)已推出基于RISC-V的处理器;

政策支持:通过“大基金”(国家集成电路产业投资基金)二期加大对设备、材料等上游领域投资,2023年以来已注资超800亿元。

半导体产业链的国产化是一场“持久战”,需在正视技术差距的同时,坚定战略定力。随着政策支持、资本投入与人才积累的持续加码,我国有望在未来5-10年实现从“产业链跟随者”向“关键领域引领者”的跨越,为全球半导体产业格局注入新动能。在此过程中,需平衡“自主创新”与“开放合作”,通过产业链协同与全球资源整合,逐步突破技术壁垒,构建安全可控的半导体生态体系。

审核编辑 黄宇

-

半导体

+关注

关注

336文章

29989浏览量

258371 -

芯片设计

+关注

关注

15文章

1128浏览量

56454 -

封测

+关注

关注

4文章

378浏览量

35995

发布评论请先 登录

知存科技荣登2025中国半导体企业影响力百强榜单

重塑话语权:新时达硬核技术为中国半导体制造打通自主可控关键链路

封测全球份额超50%却卡壳高端设备,中国半导体如何补齐最后一块短板?

封测全球份额超50%却卡壳高端设备,中国半导体如何补齐最后一块短板?

评论