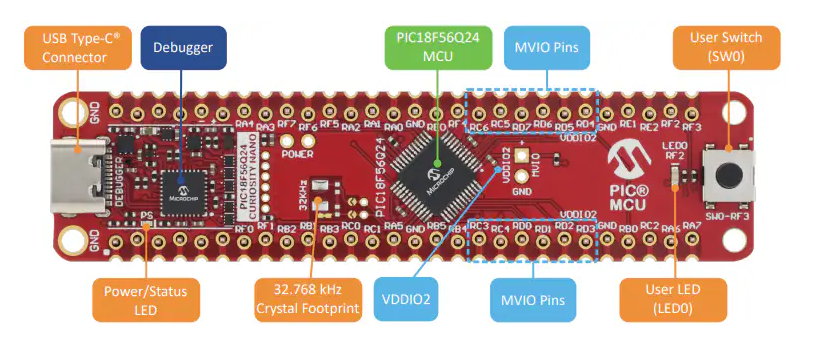

Microchip Technology PIC18F24/25Q24微控制器是PIC18-Q24微控制器系列28/40/44/48引脚器件的一部分,用于传感器接口、实时控制和通信应用。PIC18F24Q24具有16KB内存、1KB数据SRAM和512B EEPROM。同时,PIC18F25Q24具有32KB内存、2KB数据SRAM和512B EEPROM。该器件具有24个I/O引脚,包括四个由V DDIO ^2^ 供电的MVIO引脚。

数据手册:*附件:Microchip Technology PIC18F24,25Q24 微控制器数据手册.pdf

Microchip PIC18F24/25Q24微控制器还具有用于处理中断的具有固定延迟的向量中断控制器、系统总线仲裁器、直接内存访问(DMA)功能、支持异步收发器(UART)、支持异步DMX-512、数字可寻址照明接口(DALI®)和本地互连网络(LIN)协议、串行外设接口(SPI)和I^2^C。此外,该系列还包括内存访问分区(MAP)和设备信息区(DIA)等内存功能,可存储工厂校准值,帮助提高温度传感器的精度。

特性

- 多电压I/O (MVIO)

- MVIO供电引脚支持在1.62V至5.5V电压范围内工作

- 该域与主V

DD电压电平无关 - 通过可编程跳变点在附加电压域上进行电压监控

- 编程和调试接口禁用(PDID),可以禁用ICSP接口,以防止外部存储器访问或修改

- 向量中断(VI)功能-中断响应时间更短

- 可选择的高/低优先级

- 可编程矢量表基础地址

- 固定中断延迟:3个指令周期

- 向后兼容以前的中断功能

- 内存访问分区(MAP),程序闪存可分为:

- 应用方框

- 启动块

- 带SAFLOCK的存储区域闪存(SAF)模块,可防止修改

- 编程和调试

- 编程和调试接口禁用(PDID)

- 经由2个引脚实现在线串行编程™(ICSP™)

- 电路内调试 (ICD)(通过2个引脚提供3个断点)

- 片上集成调试

- 4个带计算功能的直接内存访问(DMA)控制器模数转换器(ADCC):

- 8位数模转换器 (DAC):

- 2个I/O引脚上提供缓冲输出

- 与ADC和比较器的内部连接

- 2个高速比较器:(CMP)

- 可配置功率与速度模式

- 可配置输出极性

- 通过外设引脚选择外部输出

- 2个零交叉检测(ZCD),检测引脚上的交流信号何时接地

- 3个16位双PWM提供6个PWM输出

- 电压基准:

- 固定电压基准,1.024V、2.048V和4.096V输出电平

- 内部连接ADC、比较器和DAC

- UART,硬件支持LIN/DMX

- 2个SPI模块:

- 可配置长度字节

- 任意长度数据包

- 无接收发射和无发射接收选项

- 传输字节计数器

- 独立发射和接收缓冲器,具有2字节FIFO和DMA功能

- 2个I^2^C模块,兼容SMBus和PMBus™:

- 7位和10位寻址模式,具有地址屏蔽模式

- 专用地址、发射/接收缓冲器和DMA功能

- I^2^C、SMBus 2.0/3.0和1.8V输入电平选择

- 多主器件模式,包括自寻址

- 设备信息区(DIA)存储:

- 温度指示器出厂校准数据

- 固定电压基准测量数据

- Microchip唯一标识符

- 低功率模式

- 睡眠: < 1μA(3V时典型值)和最低功耗

- 打盹模式:CPU和外设以不同的周期速率运行(通常CPU更低)

- 空闲:外设运行时CPU停止

- 外设模块禁用(PMD),可选择性地禁用硬件模块,最大限度地降低未使用外设的有源功耗

- 器件I/O端口特性:

- 24个I/O引脚,包括4个MVIO引脚,由V

DDIO^2^ (PIC18F24/25/26Q24)供电 - 35个I/O引脚,包括12个MVIO引脚,由V

DDIO^2^ (PIC18F45/46Q24)供电 - 43个I/O引脚,包括12个MVIO引脚,由V

DDIO^2^ (PIC18F55/56Q24)供电 - MVIO引脚支持1.62V至5.5V电压范围

- 独立可编程I/O方向、开漏、压摆率和弱上拉控制

- 使用LV-TTL输入缓冲器在所有I/O引脚上设有低压接口

- 大多数引脚上的变化中断

- 3个可编程外部中断引脚

- 24个I/O引脚,包括4个MVIO引脚,由V

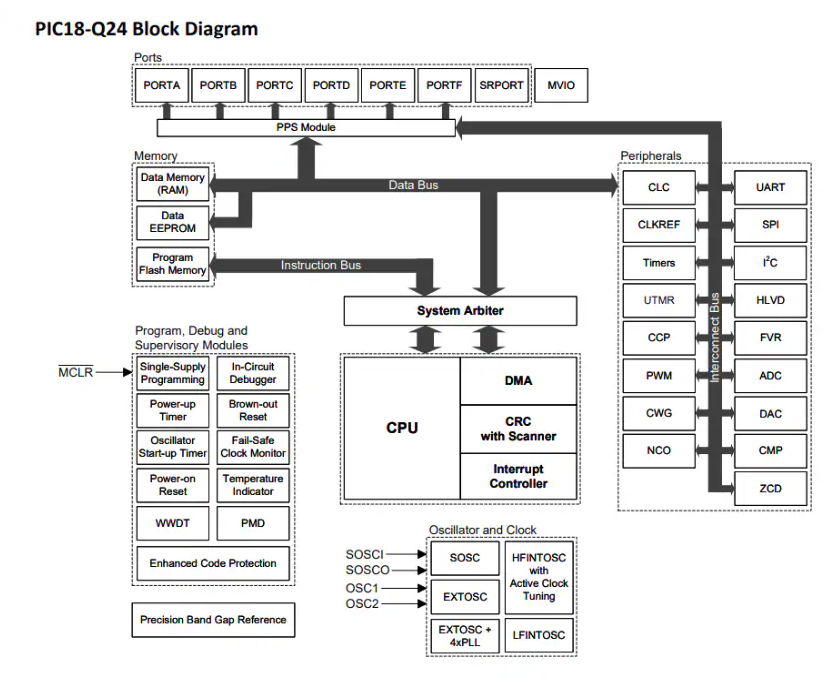

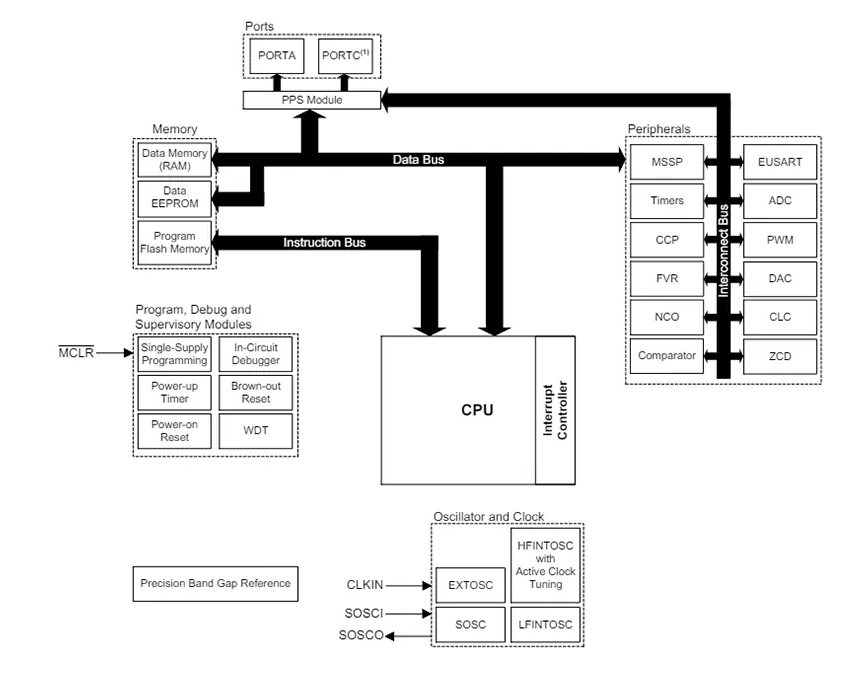

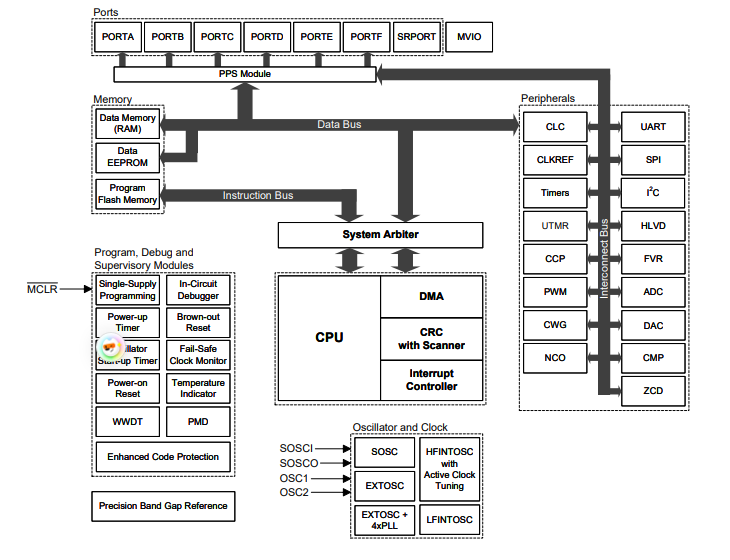

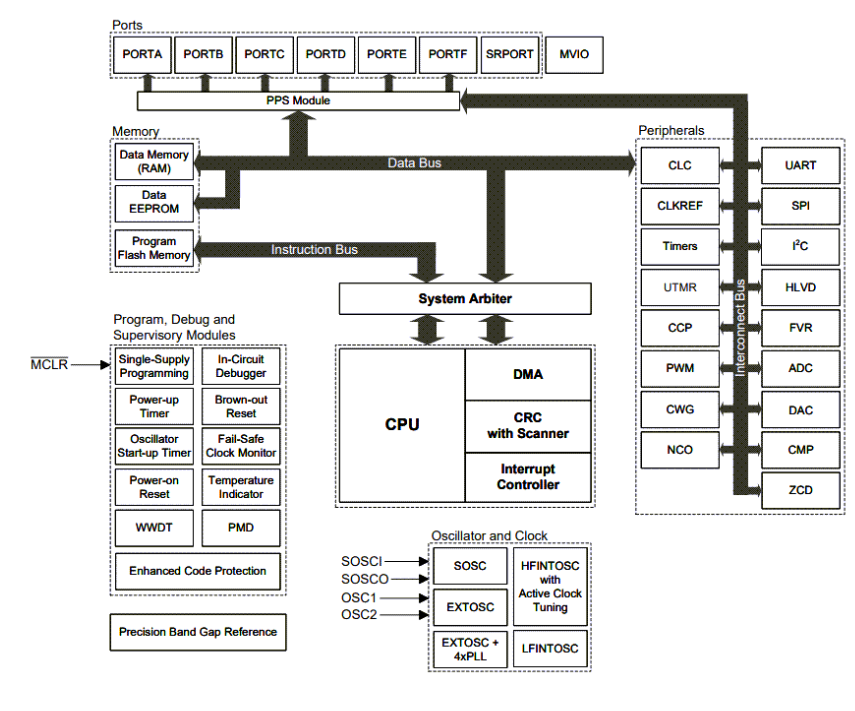

框图

PIC18F24/25Q24微控制器技术解析与应用指南

一、产品概述与核心特性

Microchip Technology的PIC18F24/25Q24系列是28引脚低功耗高性能微控制器,采用先进的XLP技术,专为传感器接口、实时控制和通信应用而设计。该系列产品具有以下显著特性:

- 多电压I/O(MVIO)接口:允许部分I/O引脚工作在不同于微控制器主电压域的电压水平

- 增强型代码保护功能:

- 可禁用编程和调试接口(PDID)

- 存储区闪存(SAF)一次性编程能力

- 丰富的模拟外设:

- 10位带计算功能的模数转换器(ADCC),最高300ksps采样率

- 8位信号路由端口模块

- 高/低电压检测(HLVD)

- 高速模拟比较器(CMP)

二、内存架构与分区管理

PIC18F24/25Q24采用改良的哈佛架构,提供灵活的内存管理方案:

程序闪存分区

- 应用区块:存储用户固件,默认分配全部程序闪存空间

- 引导区块:可选区域,适合存储引导加载程序,大小通过BBSIZE配置位可调

- 存储区闪存(SAF) :数据存储专用区,不可执行代码,位于内存末端

内存保护机制

- 写保护:通过WRTAPP、WRTSAF等配置位实现不同区域的写保护

- 代码保护:CP配置位控制整个程序存储器的读取保护

- 安全锁定:SAFLOCK配置位使SAF区域变为一次性可编程

三、关键外设功能解析

1. 多电压I/O系统(MVIO)

MVIO接口允许部分I/O引脚(4个在28引脚版本)由独立的VDDIO2供电(1.62V至5.5V),包含:

- 专用低电压检测电路

- 中断功能

- 与主电压域完全隔离的操作

2. 增强型模拟外设

10位ADCC转换器:

- 支持30个外部通道和9个内部通道

- 硬件电容分压器(CVD)支持,简化触摸传感设计

- 自动数学功能(平均、滤波、阈值比较)

互补波形发生器(CWG) :

- 上升/下降沿死区控制

- 全桥、半桥和单通道驱动模式

- 多种信号源选择

3. 通信接口

- 双I2C模块:支持标准/快速/快速+模式(最高1MHz)

- 双SPI模块:可配置数据包长度,带DMA支持

- 双UART模块:

- 支持LIN、DALI、DMX-512协议

- 异步UART、RS-232/485兼容

四、开发实践指南

1. 最小系统连接要求

2. 编程与调试接口

- ICSP接口使用两个专用引脚(ICSPCLK和ICSPDAT)

- 开发完成后可通过ICSPDIS配置位永久禁用编程接口

- 代码保护状态下仍可通过内部NVM接口访问内存

3. 低功耗设计技巧

- 多种省电模式:Doze、Idle、Sleep

- 外设模块禁用(PMD)功能:可单独关闭未使用外设以降低功耗

- 典型Sleep电流:<1μA @3V

- 工作电流:48μA @32kHz,3V

五、应用设计注意事项

- 未使用I/O处理:应配置为输出并驱动至低电平,或通过1kΩ-10kΩ电阻下拉

- 中断设计:

- 向量中断控制器(VIC)提供固定延迟(3指令周期)

- 支持127级硬件堆栈

- 可编程优先级(高/低两级)

- 时序关键应用:

- 内部振荡器精度±1%(校准后)

- 带主动时钟调谐功能

- 64MHz最大工作频率(62.5ns指令周期)

六、安全特性与产品保护

- 增强代码保护:

- 可选择禁用ICSP接口(PDID)

- 存储区闪存(SAF)锁定功能

- 防止未经授权的固件读取

- 唯一标识:

- 出厂预编程的Microchip唯一标识符(MUI)

- 可选客户定制外部标识符(EUI)

- 安全存储:

- 设备信息区(DIA)存储工厂校准数据

- 配置信息区(DCI)包含器件特性参数

-

微控制器

+关注

关注

48文章

8249浏览量

162347 -

实时控制

+关注

关注

0文章

51浏览量

9828 -

传感器接口

+关注

关注

0文章

22浏览量

12775

发布评论请先 登录

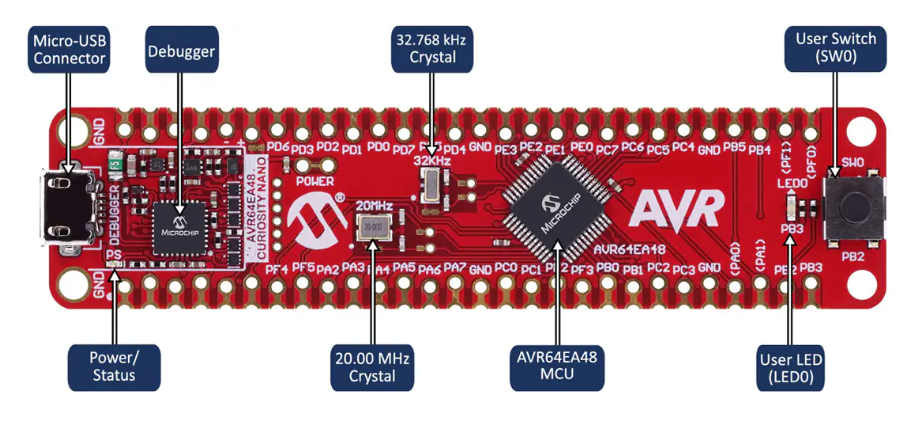

如何启动块板与PIC微控制器和16-24个带有微控制器的通信

如何设计PIC18f2520微控制器的PCB

PIC18F2515/PIC18F2510/PIC18F24

PIC微控制器技术及应用 24-29章

PIC18F到PIC24F软件移植指南

仿真PIC18和PIC24单片机及dsPIC数字信号控制器的数据EEPROM

PIC16F18013/14/23/24微控制器技术解析与应用指南

PIC18-Q24 系列微控制器:高性能、低功耗与增强型代码保护的完美结合

PIC18F56Q24 Curiosity Nano开发板技术解析与应用指南

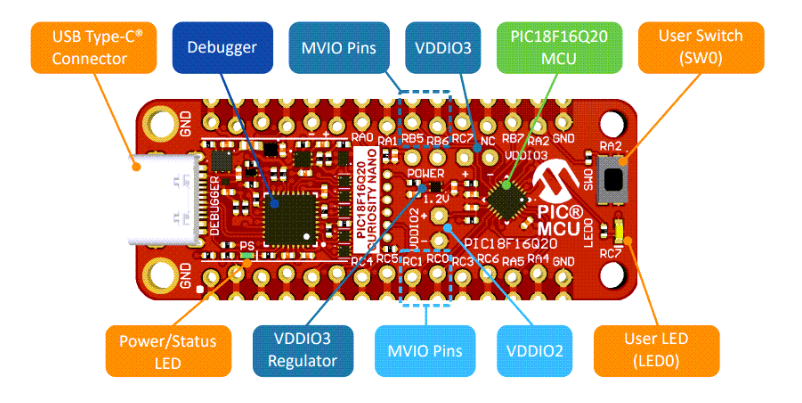

PIC18F16Q20 Curiosity Nano开发板技术解析与应用指南

PIC18-Q24 微控制器:高性能、低功耗与增强型代码保护的完美结合

PIC18F56Q71 Curiosity Nano评估套件技术解析与应用指南

PIC18F24/25Q24微控制器技术解析与应用指南

PIC18F24/25Q24微控制器技术解析与应用指南

评论