近日,中国集成电路知识产权联盟秘书处纲正知识产权中心发布了《集成电路专利态势报告(2018版)》。该报告分别从集成电路总体、DRAM 领域、FPGA 领域、光刻设备领域这四个方面,分析了各个领域的专利态势。

集成电路总体专利态势

首先来看集成电路总体的专利态势,据报告显示,集成电路领域专利申请量态势逐年增长。2010年-2015年间年均增长率 5.89%,其中 2015 年增速最高,达到 9.28%。

截止到 2017 年 12 月 31 日,集成电路领域全球公开专利申请 209.7 万件,授权 144.5 万件。其中,中国大陆申请 46.4 万件,授权 27.8 万件,紧随美国和日本之后,位列第三。

报告指出,《国家集成电路产业发展推进纲要》等全国及地方各层面战略新兴产业规划的相继出台营造了良好发展环境,激发企业活力和创造力,带动产业链协同可持续发展,推动中国集成电路领域跨越式发展。

截至目前,全球专利申请总量的冠军是三星,随后分别是 NEC、高通、日立、富士通、松下、东芝、三菱化学、IBM 和索尼。可以看到,在前十名中有一家韩国企业、两家美国企业和七家日本企业。

而在中国大陆专利申请总量排名中,排在第一和第二位的分别是中兴通讯和华为。随后分别是三星、国家电网、高通、京东方、松下、OPPO、英特尔和台积电。

从 2017 年新公开的全球专利申请量排名来看,高通和三星仍占据前两位。值得一提的是,排名前十的企业中,有三家中国企业上榜,分别是华为、中兴和京东方,可见中国企业 2017 年也在全球持续大量布局。

而在 2017 年新公开的中国大陆专利申请量排名中,申请量最大的为中兴通讯,其后为国家电网、努比亚和华为,与中国大陆申请总量排名差异不大。值得一提的是,OPPO 和小米等中国厂商进入前十,表明近年来在加强专利布局方面正在逐步追赶。

在集成电路行业专利技术领域排名(IPC 大组前十)中,申请量较大的领域集中于集成电路的制造、零器件、数据交换与传输、光刻设备以及存储器。

在中国大陆内地省市专利排名中,广东省集成电路专利申请量达 90790 件,位居全国首位。北京、江苏、上海和浙江紧随其后,分别以52067件、35336件、31298件、24493件专利申请量位居第二、三、四、五位。

总体来看,全球集成电路行业专利态势呈现五个特点:一是全球范围内集成电路行业的专利申请量现阶段趋于稳定;二是在申请人和申请地域两个维度呈现聚集的特点;三是申请人以企业为主;四是 2017 年,集成电路领域专利公开量仍然较大;五是中国信息技术申请总量中占比较高的多为经济发达地区。

DRAM 领域专利态势

在 DRAM 领域,截止到 2017 年 12 月 31 日,全球公开专利申请 14 万余件,全球申请总量排名日本最高,其后是美国和韩国。其中,中国大陆专利 6 千余件,位居第六位。

DRAM 行业专利申请高峰期在 1995 年到 2006 年。1995 年申请量开始新一轮激增,正是 DDR 技术开始发展的时期。巅峰时期可以达到年申请量 6000 多件,从 2007 年开始专利申请量逐年下降,近两年维持在每年 2000 件左右。

在全球 DRAM 专利申请总量排名中,位居前列的主要申请人有:三星、海力士、美光和日立。值得注意的是,这与 DRAM 内存市场占有率也相匹配。

而在中国大陆 DRAM 专利申请总量排名中,位居前列的企业主要有:海力士、三星、NEC 和IBM等。

总体来看,DRAM 领域专利态势呈现三个特点:一是 DRAM 领域技术发展较为成熟,技术研发投入有所减少;二是 DRAM 研发重心在于 DRAM 操作和设计方面;三是 DRAM 领域知识产权作用巨大。

FPGA 领域专利态势

在 FPGA 领域,截止到 2017 年 12 月 31 日,全球公开专利申请 8 万余件,全球申请总量排名中国大陆最高,总共申请专利 2 万余件,其后是美国和日本。

FPGA 领域全球专利申请经历了三个阶段,第一个阶段是 1989 年到 2000 年,处于萌芽期,申请量较少,第二阶段是 2001 年到 2012 年,是 FPGA 产业的快速发展期,年申请量直线上升,第三阶段是 2013 年到 2017 年,上升趋势趋于稳定,年申请量小幅上升。

在全球 FPGA 专利申请总量排名中,位居前三的企业为 ALTERA、赛灵思和 L attice。值得一提的是,在前十的排名中,有两家中国企业也入围了,分别是位居第四和第七的中国电网和中兴。

而在中国大陆 FPGA 专利申请总量排名中,主要的申请人为国家电网、中兴通讯和华为等企业及北京航空航天大学、哈尔滨工业大学、浙江大学和电子科技大学等高校。

报告指出,FPGA 领域专利主要集中在 H03K19/177和 H03K19/173矩阵式排列的逻辑电路,另外,由于 FPGA 中很多涉及硬件电路编程语言的,还有相当一部分专利聚焦在计算机辅助设计、电路测试上。

总体来看,FPGA 领域专利态势呈现四个特点:一是FPGA领域技术发展较为成熟,上升趋势趋于稳定;二是全球范围内,中国、美国和日本申请量位于前列;三是 FPGA 领域专利持有者相对比较集中;四是 FPGA 领域国内主要研发主体还是高校。

光刻设备领域专利态势

在光刻设备领域,截止到 2017 年 12 月 31 日,全球公开专利申请 8.2 万件,全球申请总量排名美国最高,其后是日本和韩国。其中,中国大陆专利 1 万件,位居第四位。

在全球光刻设备专利申请总量排名中,ASML 位居榜首,紧随其后的是卡尔蔡司、海力士和三星。

而在中国大陆光刻设备专利申请总量排名中,除 ASML 依然位居榜首外,其余位居前十的基本都是中国企业,分别有中芯国际、上海微电子装备有限公司、京东方、上海华虹宏力、上海华力微电子,还有中科院光电研究所和中科院微电子所两家科研院所。

报告指出,光刻领域专利排名较高的类别聚焦在 G03F7图纹面、H01L21专门适用于制造和处理半导体或固体器件或其部件的方法或设备上,申请量明显高出其他分类。

总体来看,光刻设备领域专利态势呈现四个特点:一是光刻设备技术近几年申请量相对稳定;二是全球范围内日本和美国申请量位于全球前列,韩国第三;三是光刻设备领域中国主要的申请人中,主要为企业;四是光刻设备主要技术集中在 G03F7、H01L21两个 IPC 类别上,说明曝光材料及设备、半导体设备制造技术在光刻设备领域占比较高。

-

FPGA

+关注

关注

1655文章

22283浏览量

630243 -

华为

+关注

关注

217文章

35783浏览量

260709 -

中兴

+关注

关注

6文章

2001浏览量

69242

发布评论请先 登录

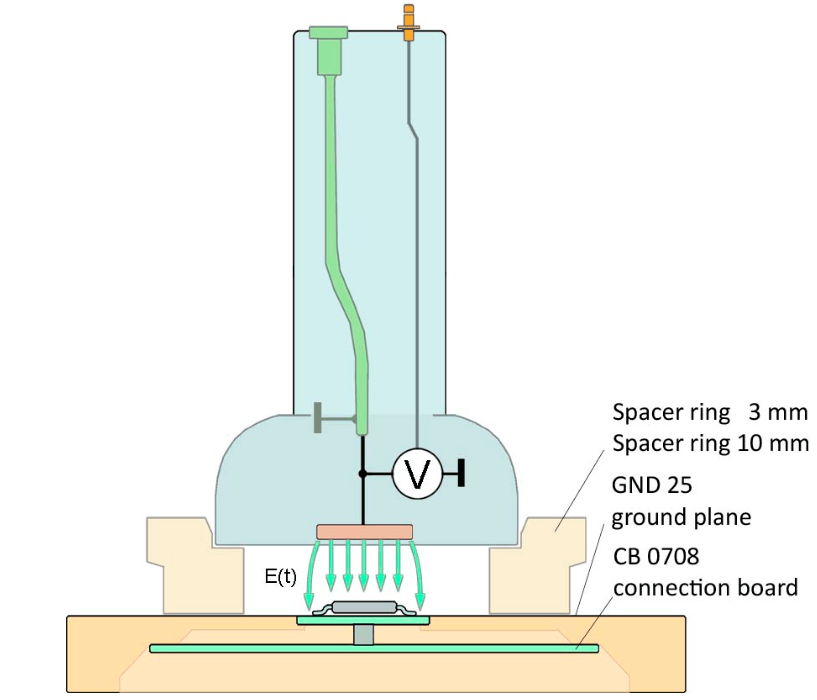

如何确定12英寸集成电路新建项目中光刻机、刻蚀机等不同设备所需的防震基座类型和数量?-江苏泊苏系统集

PDK在集成电路领域的定义、组成和作用

中国集成电路大全 接口集成电路

集成电路制造设备防震基座选型指南:为稳定护航

未来五年:集成电路制造设备定制化防震基座制造厂商的风云之路

爱普生(EPSON) 集成电路IC

集成电路设计中静态时序分析介绍

集成电路为什么要封胶?

数字集成电路 Verilog 熟悉vivado FPGA微电子、电子工程

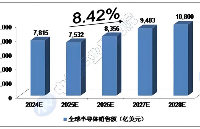

未来五年中国集成电路与半导体设备防震基座需求预测

集成电路电磁兼容性及应对措施相关分析(三)集成电路ESD 测试与分析

集成电路电磁兼容性及应对措施相关分析(三)—集成电路ESD 测试与分析

DRAM、FPGA、集成电路总体和光刻设备领域的专利态势分析

DRAM、FPGA、集成电路总体和光刻设备领域的专利态势分析

评论