概述

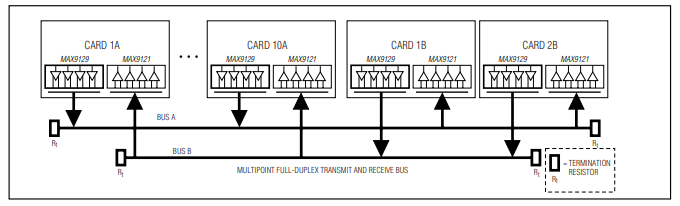

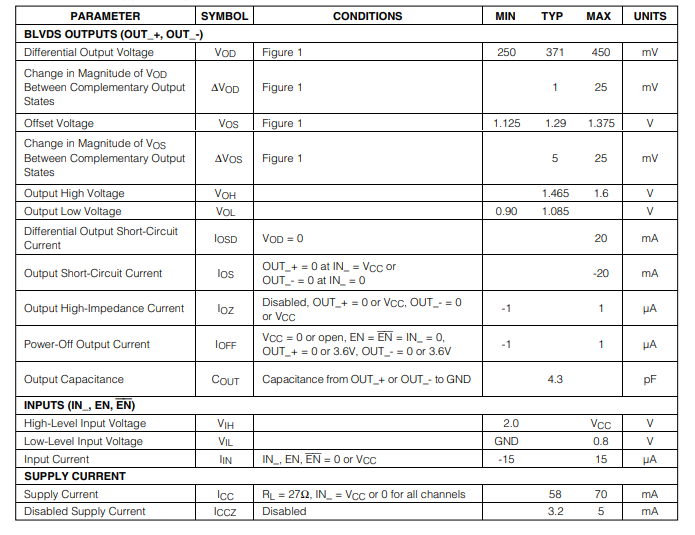

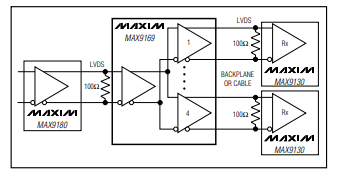

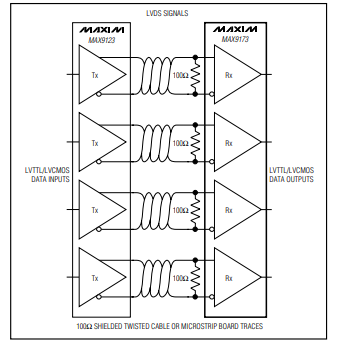

MAX9129是一款具有流通引脚排列的四路总线低压差分信号(BLVDS)驱动器。该器件设计用于驱动多点重负载的总线,具有受控的过渡时间(最小1ns,从0%至100%),以减少信号反射。MAX9129接收四路LVTTL/LVCMOS输入电平,即使在27Ω负载下,也可转换为250mV至450mV (标准LVDS电平信号)的输出电平信号,速度高达200Mbps (100MHz)。

上电复位确保在上电和断电过程中,所有的四个输出被禁止,呈现高阻输出。通过控制EN和/EN两个输入,输出可以置为高阻态,使器件处于11mW的低功耗状态。所有四路接收器共用该使能信号。流通引脚排列简化了PCB的布线,且通过分开LVTTL/LVCMOS输入和BLVDS输出,减少了串扰。

MAX9129工作于+3.3V单电源,满足-40°C至+85°C的工作温度范围。该器件提供16引脚QFN和TSSOP封装。对于具有流通引脚排列的四路LVDS线接收器,请参考MAX9121的数据资料。

数据表:*附件:MAX9129四路、总线式LVDS驱动器,引脚按信号流向排列技术手册.pdf

应用

特性

- 27Ω负载下驱动LVDS电平信号

- 1ns (从0%至100%)最小过渡时间,减少了反射

- 保证200Mbps (100MHz)数据速率

- 使能引脚控制高阻输出

- 电源断电后,输出为高阻

- 无毛刺输出的上电和断电过程

- 可热插拔

- 流通引脚排列

- 提供有微型QFN封装(比TSSOP小50%)

- +3.3V单电源

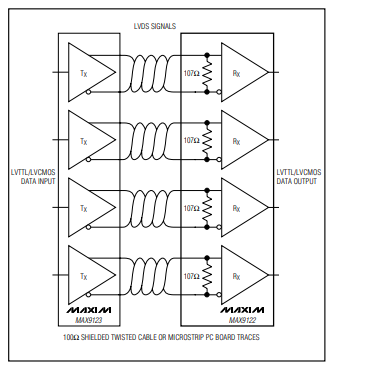

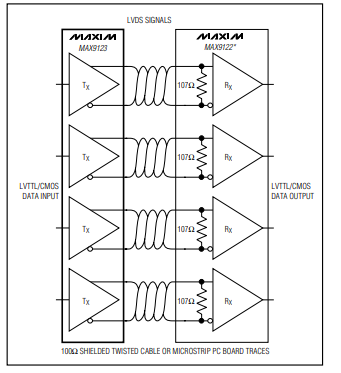

应用电路

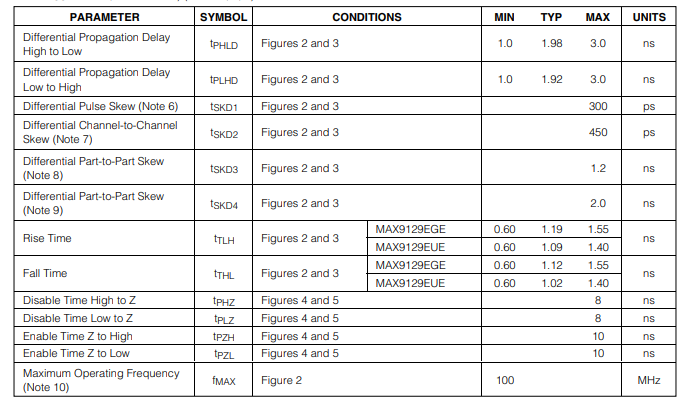

交流电气特性

典型操作特性

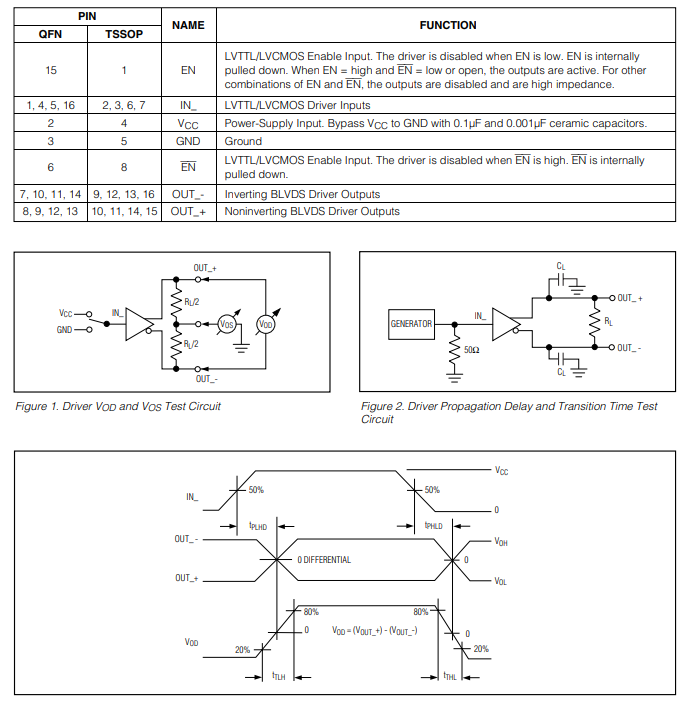

引脚配置描述

-

驱动器

+关注

关注

54文章

9019浏览量

153388 -

lvds

+关注

关注

2文章

1216浏览量

69136 -

LVTTL

+关注

关注

0文章

89浏览量

13431

发布评论请先 登录

总线LVDS驱动器电路设计

ADN4667: 3 V LVDS四通道CMOS差分线驱动

SN65LVDS047 具有直通引脚的四路 LVDS 驱动器

MAX9129EUE+ 接口 - 驱动器,接收器,收发器

MAX9129EUE+T 接口 - 驱动器,接收器,收发器

DS90C031QML LVDS四路CMOS差分线路驱动器数据表

DS90C031B LVDS四路CMOS差分线路驱动器数据表

DS90C031 LVDS四路CMOS差分线路驱动器数据表

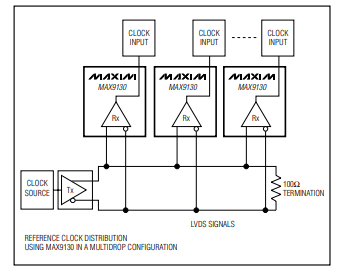

MAX9130单路、500Mbps、LVDS线接收器,SC70封装技术手册

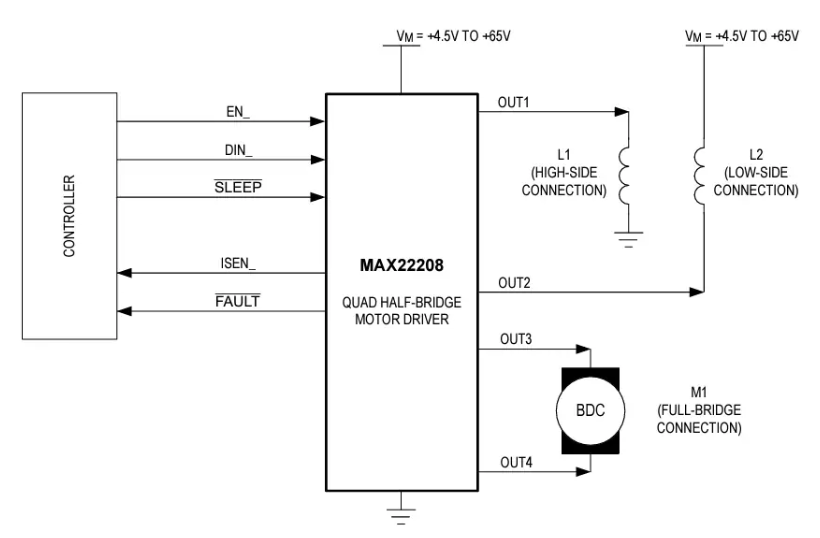

Analog Devices / Maxim Integrated MAX22208四路半H桥驱动器数据手册

MAX9129四路、总线式LVDS驱动器,引脚按信号流向排列技术手册

MAX9129四路、总线式LVDS驱动器,引脚按信号流向排列技术手册

评论