概述

LTC 6603 是一款双通道、匹配、可编程低通滤波器,适用于通信接收器和发送器。 LTC6603 的选择性,再加上其线性相位、相位匹配和动态范围,使其适合于许多通信系统中的滤波处理。 凭借通道之间的 1.5° 相位匹配精度,LTC6603 可以在那些需要匹配滤波器对的应用 (例如:收发器 I 和 Q 通道) 中使用。 此外,差分输入和输出还提供了一个适合于大多数通信系统的简单接口。

采样数据滤波器不需要使用一个外部时钟,而且其截止频率可以采用单个外部电阻器来设定 (准确度达 3.5% 或更高)。 该外部电阻器负责设置一个内部振荡器,这个振荡器在应用于滤波器网络之前便被分频。 这使得对于每个外部电阻器阻值可以获得多达 3 种截止频率,从而允许在一个超过 6 个倍频程的范围内设置截止频率。 或者,也可以利用一个外部时钟来设定滤波器截止频率。 滤波器增益也可被设置为 1、2、4 或 16。

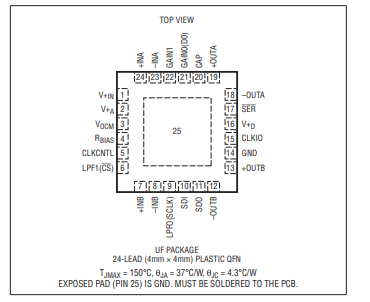

LTC6603 具有一种可通过串行接口来设置的低功率停机模式,并采用 24 引脚 4mm x 4mm QFN 封装。

数据表:*附件:LTC6603双通道、可调低通滤波器技术手册.pdf

应用

特性

- 保证相位和增益匹配规格

- 可编程带宽 (BW) 高达 2.5MHz

- 可编程增益 (0dB/6dB/12dB/24dB)

- 9 阶线性相位响应

- 差分、轨至轨输入和输出

- 低噪声:-145dBm/Hz (参考于输入)

- 低失真:-75dBc (在200kHz)

- 简单的引脚编程或 SPI 接口

- 可利用一个外部电阻器来设定最大速率/功率

- 工作电压范围:2.7V 至 3.6V

- 输入范围从 0V 至 5.5V

- 4mm x 4mm QFN 封装

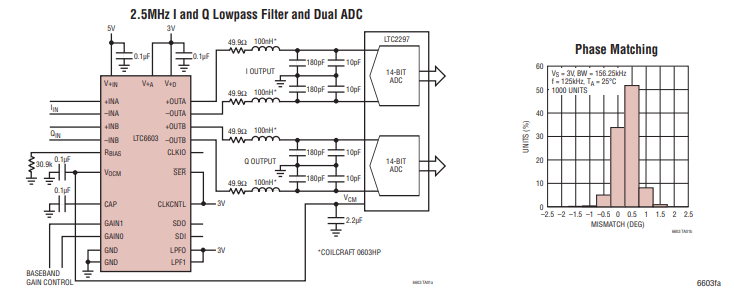

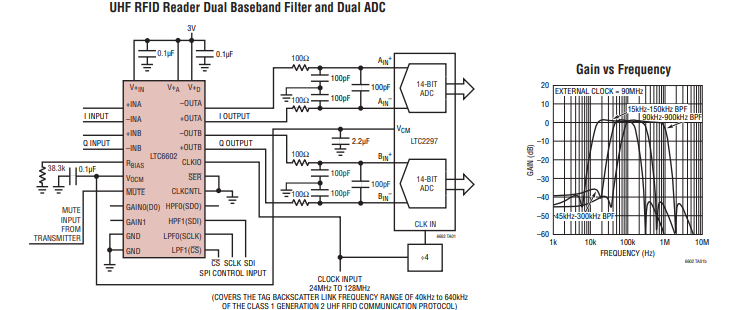

典型应用

引脚配置描述

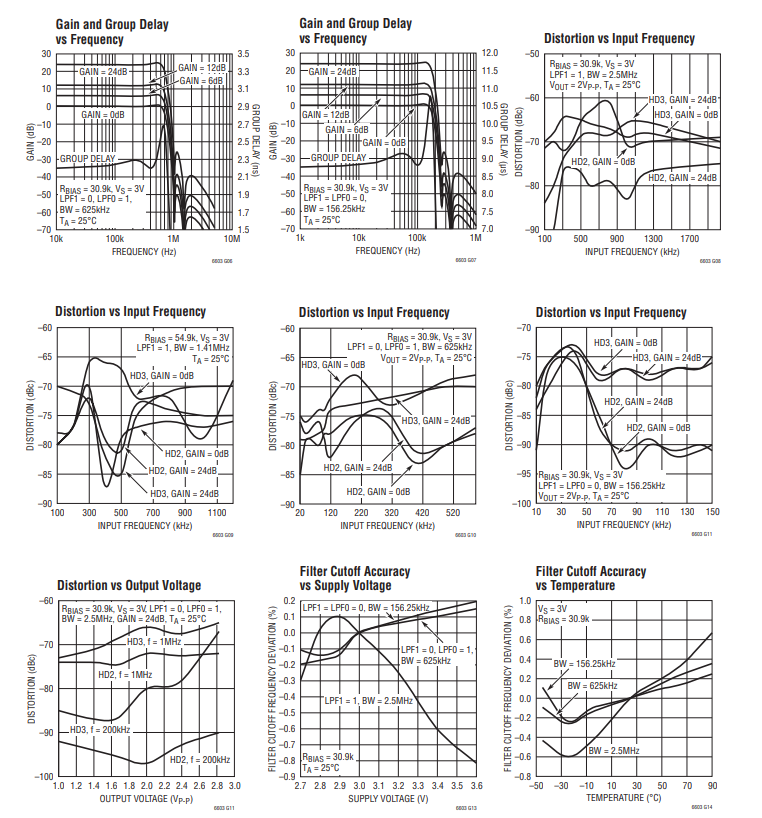

典型性能特征

典型性能特征

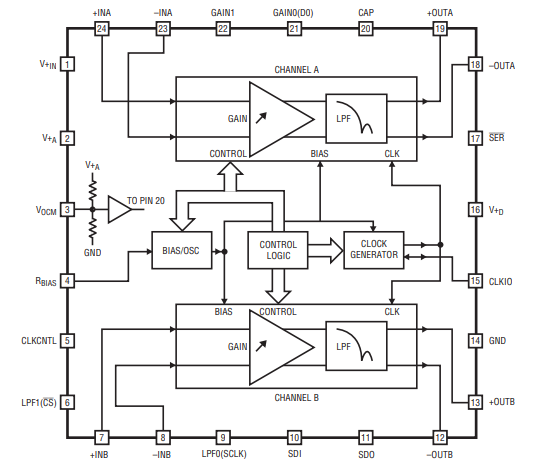

框图

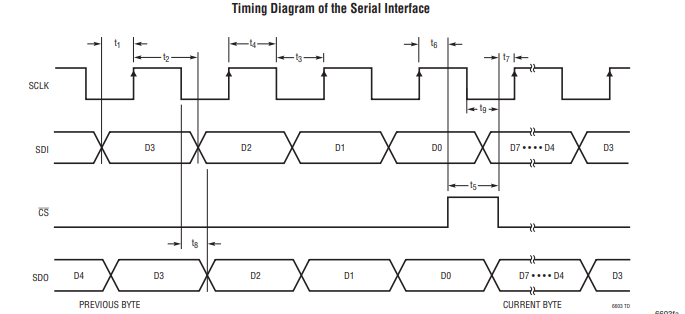

时序图

应用信息

工作原理(参考框图)

LTC6603具有两个匹配的滤波器通道,每个通道都包含增益控制和低通滤波器网络,由单个控制模块控制,并由单个时钟发生器提供时钟信号。增益和截止频率可以分别进行编程。这两个通道并非相互独立,例如,若将增益设置为24dB,那么两个通道的增益均为24dB。滤波器可以由外部时钟驱动,也可以使用内部振荡器。连接到RBias引脚的电阻为滤波器网络和内部振荡器设置偏置电流(除非由外部时钟驱动)。改变时钟频率会改变滤波器带宽,这使得滤波器能够“调谐”到多种不同的带宽。

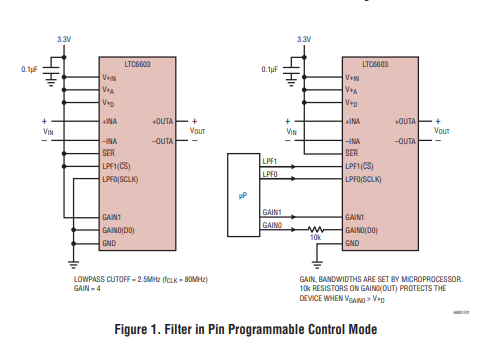

引脚可编程接口

如图1所示,将SER连接到V+D可使滤波器通过引脚直接控制,通过引脚可编程控制线GAIN0、GAIN1、LPF1和LPF0进行控制。GAIN0(D0)引脚为双向引脚(在引脚可编程控制模式下为输入,在串行控制模式下为输出)。在引脚可编程控制模式下,该引脚上的电压不能超过V+D;否则,大电流可能会通过寄生二极管注入V+D(见图2)。建议在GAIN0(D0)引脚处连接一个10kΩ电阻(见图1)。SER具有内部电流限制功能,限制电流约为1mA。逻辑输入均无内部上拉或下拉,需上拉至V+D 。

串行接口

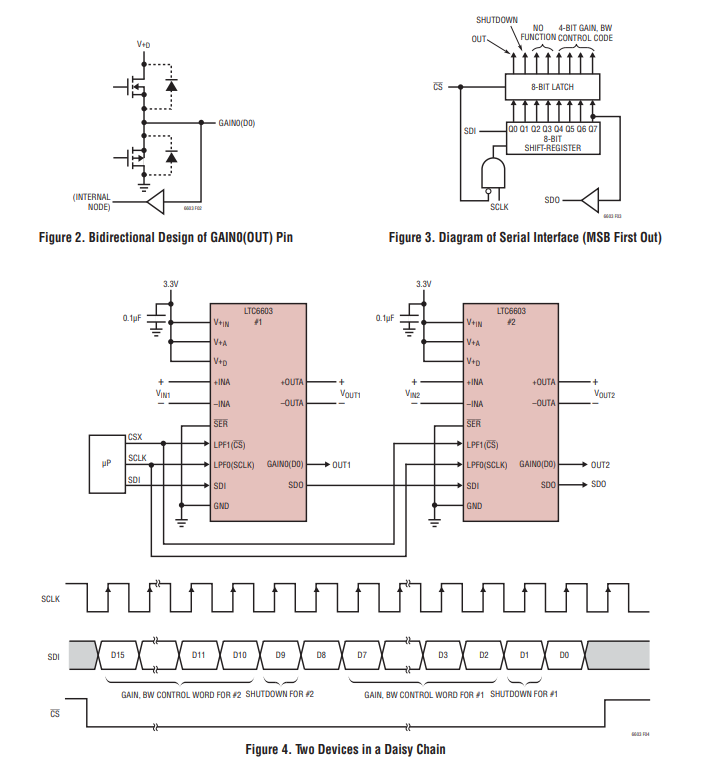

将SER连接到地可通过SPI串行接口控制滤波器。当CS为低电平时,串行数据在时钟(SCLK)上升沿从SDI移入8位移位寄存器,最高有效位(MSB)最先移出(见图3)。串行数据在时钟下降沿从SDO移出。CS为高电平时,8位移位寄存器中的数据将加载到8位D锁存器(即串行控制寄存器)中。注意:在拉高CS之前,SCLK必须为低电平,以避免出现额外的内部时钟脉冲。SDO始终处于活动状态(不会处于三态),不能与其他SPI输出进行“线或”操作。此外,CS为高电平时,SDO不会强制为零。

多个LTC6603可以与其他LTC6603或其他具有串行接口的器件进行菊花链连接。菊花链连接通过将前级芯片的SDO连接到下一级芯片的SDI来实现,同时SCLK和CS保持连接到所有芯片,菊花链串行数据在时钟作用下传输到所有芯片,然后拉高CS信号以同时更新所有芯片。图4展示了两个LTC6603菊花链连接的SPI配置示例。

-

滤波器

+关注

关注

162文章

8358浏览量

184777 -

接收器

+关注

关注

15文章

2637浏览量

76331 -

低通滤波器

+关注

关注

15文章

528浏览量

48830

发布评论请先 登录

具有双通道可编程带通滤波器和差分驱动器LTC6602的演示板DC1304A-A

LTC6603 双通道、可调低通滤波器

LTC6601/LTC6603/LTC6605 - 高性能宽带有源滤波器和 ADC 驱动器系列提供前所未有的准确度以减轻设计负担

UG-1045:评估ADRF6520双通道、可编程低通滤波器和VGA,用于微波无线电的2 GHz通道间距

LTC6603双通道、可调低通滤波器技术手册

LTC6603双通道、可调低通滤波器技术手册

评论