1984 年,在硅谷工作的Bernie Vonderschmitt、Ross Freeman 和 Jim Barnett 共同构建了一个设想,他们梦想创立一家不同于一般的公司。他们希望创建一家在整个新领域内开发和推出先进技术的公司。并且,他们还希望以这种方式领导它:在这里工作的人们热爱他们的工作、享受工作的乐趣,并对他们所从事的工作着迷。他们创造性地推出了“无晶圆半导体”公司的概念。

图2-1 Ross Freeman(左)是FPGA的发明人,Bernie Vonderschmitt(右)是赛灵思公司的创始人

RossFreeman,这位密西根大学的毕业生,1984年提出了在那个晶体管堪比黄金的时代最为激进的想法——让芯片就像一个空白的磁带,可以随由工程师在上面编程增添功能,就好像画师在白布上任意涂鸦。而这念头,又如一石激起千层浪,诞生了一个价值数十亿美元的全新行业——可编程逻辑器件(PLD)。看,牛人是这样看IC layout的,这是Ross Freeman在检查全球第一款FPGA--XC2064

时光荏苒,光阴如箭,30多年过去,RossFreeman最初构建的可编程器件帝国已经发生了翻天覆地的变化,恰如人间的沧海桑田,赛灵思还是赛灵思 ,但是FPGA已经不是原来的FPGA了!从最初的胶合逻辑到嵌入式逻辑处理再到云计算人工智能加速处理单元再到赛灵思第四任CEO Vitor Peng带来的ACAP平台,与时俱进的赛灵思书写了一个没有竞争对手时不断超越自己的励志故事。

3月16日,刚上任不到两个月的Vitor Peng来到中国,带着他迷人的微笑,在长达近四个小时的时间里为中国媒体分享了他治下赛灵思的战略并揭晓了一个有500亿晶体管耗资10亿美元打造的新品---ACAP平台。

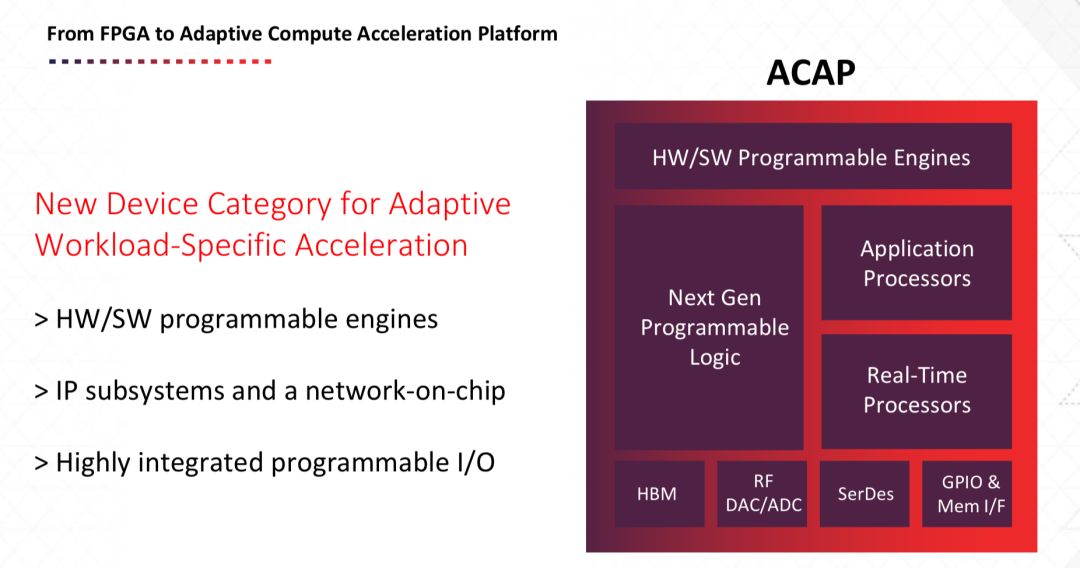

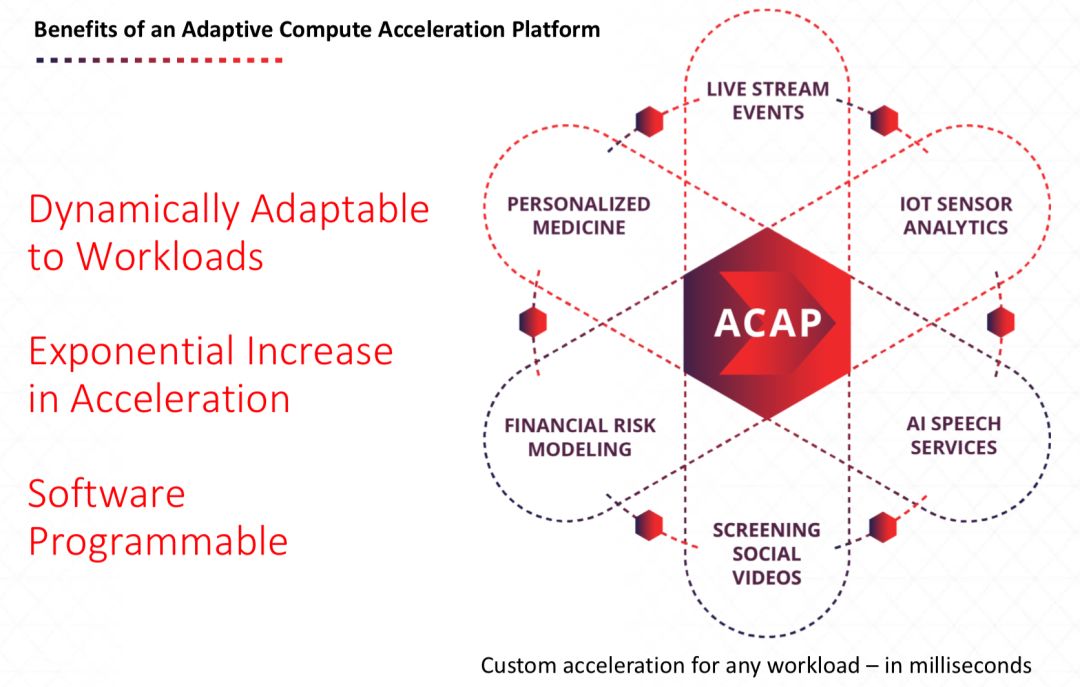

ACAP是什么?自适应计算加速平台ACAP(Adaptive Compute Acceleration Platform),这是一款超越FPGA功能的突破性产品,简称ACAP(读A-开普),“它是一个高度集成的多核异构计算平台,能根据各种应用与工作负载的需求从硬件层对其进行灵活修改。ACAP 可在工作过程中进行动态调节的自适应能力,实现了 CPU 与 GPU 所无法企及的性能与性能功耗比。”Victor指出,“在大数据与人工智能迅速兴起的时代,ACAP 理想适用于加速广泛的应用,其中包括视频转码、数据库、数据压缩、搜索、AI推断、基因组学、机器视觉、计算存储及网络加速等。软硬件开发人员将能够针对端点、边缘及云应用设计基于 ACAP 的产品。首款 ACAP 产品系列,将是采用台积电 7 nm工艺技术开发的代号为“Everest(珠穆朗玛峰)”的产品系列,该产品将于今年年底实现流片。 ”

这是赛灵思耗资10亿美元,1500名员工四年打造的心血,最高级别有500亿的晶体管!

“ACAP未来将成为一种新的主流产品类型,我们公司是首先推出ACAP这类产品的公司,我们认为未来需要这种更加灵活的能对工作负载适应性的平台,它会变成一个主流平台,和CPU、GPU一样会成为非常基础性的未来世界构建平台。”他坚定地表示。“ACAP的推出,不仅是对业界一项重大的技术颠覆,更是我们自发明 FPGA 以来最卓著的工程成就。这款革命性的全新架构是赛灵思更广泛市场战略的一部分,将帮助公司朝着 FPGA 以外的领域发展,并突破‘仅支持硬件开发者’的局限。ACAP 产品在数据中心以及我们广泛市场领域的应用,将加速自适应算技术的广泛普及,从而让智能、互连、自适应的世界更早成为现实。”

500亿晶体管!ACAP 技术细节

ACAP 的核心是新一代的 FPGA 架构,结合了分布式存储器与硬件可编程的 DSP 模块、一个多核 SoC 以及一个或多个软件可编程且同时又具备硬件自适应的计算引擎,并全部通过片上网络(NoC)实现互连。ACAP还拥有高度集成的可编程I/O功能,根据不同的器件型号这些功能从集成式硬件可编程存储器控制器,到先进的SerDes收发器技术,前沿的RF-ADC/DAC和集成式高带宽存储器(HBM)。

Victor表示软件开发人员将能够利用 C/C++、OpenCL 和 Python 等软件工具应用ACAP系统。同时,ACAP也仍然能利用 FPGA 工具从RTL 级进行编程。

据透露,ACAP历经四年的研发,累积研发投资逾 10 亿美元,每颗芯片有500亿晶体管!赛灵思目前有超过 1500 名软硬件工程师参与“ACAP 和Everest”的设计。目前,软件工具已交付给主要客户。首款“Everest”产品将于 2018 年实现流片,于 2019 年交付给客户。

与当今最新的 16 纳米Virtex® VU9P FPGA 相比,“Everest”有望将深度神经网络的性能提升20 倍!基于“Everest”的 5G 远程无线电头端和目前最新的 16 纳米无线电相比可将带宽提升 4 倍。届时,跨多个市场领域的各种应用都能实现性能和功耗效率的显著提升,这些市场包括汽车、工业、科学与医疗、航空航天、测试、测量与仿真、音视频与广播以及消费类电子产品市场等。他表示赛灵思未来几个月会陆续发布更多ACAP平台详细信息,如需了解更多信息,请访问china.xilinx.com。

赛灵思三大愿景

Victor Peng 于 2008 年加入赛灵思,加入赛灵思之前,Peng 曾担任 AMD 公司图形产品部(GPG)芯片工程企业副总裁,是 AMD 核心芯片工程团队的主要领导人,负责为图形、游戏主机产品、CPU 芯片和消费者业务部门提供支持。拥有CPU、GPU和FPGA经历的他,更能深刻理解处理器技术未来的发展。

他表示他的治理愿景是旨在为赛灵思带来新发展、新技术和新方向,打造“自适应的智能世界”。在该世界中,赛灵思将超越 FPGA 的局限,推出高度灵活且自适应的全新处理器及平台产品系列,为用户从端点到边缘再到云端多种不同技术的快速创新提供支持。"以前我们在FPGA领域,已经没有竞争对手,现在我们进入了更高级的处理器领域,竞争对手可能是来自CPU的也可能是来自GPU的,这是一个更高级别的竞争。"他表示。这意味着英特尔、Nvidia等公司将成为赛灵思未来的竞争对手。

要适应这样的竞争,他提出未来赛灵思三大战略:

一、“数据中心加速领先”提为发展新重点

他指出赛灵思正在加强与关键数据中心客户、生态系统合作伙伴及软件应用开发商的合作力度,以进一步推动计算加速、计算存储及网络加速领域的创新与部署。数据中心是一个快速普及技术的领域,以此为重点,可以让客户迅速受益于赛灵思技术为各种应用所带来的数量级提升的性能和单位功耗性能优势,其中包括人工智能(AI)推断、视频与图像处理、基因组学等应用。

二、加速主流市场的发展

在这些主流市场中,赛灵思一直是关键技术的领先者而且拥有深厚的市场根基。这些市场包括八大市场领域:汽车、无线基础设施、有线通信、音频、视频与广播、航空航天、工业、科学与医疗、测试、测量与仿真以及消费类电子技术。这些主流市场与客户仍然是赛灵思的核心,公司将继续积极推进上述领域的创新。

三、驱动自适应计算,推出ACAP 平台

Victor 指出未来的处理器平台灵活处理负载需求,适应各种计算需求,ACAP 其实是高度集成的多核异构计算平台,能针对各种应用与工作负载的需求,从硬件层进行更改变化。ACAP 的自适应能力可支持在工作过程中以毫秒级动态调节,实现了 CPU 与 GPU 所无法企及的性能水平与单位功耗性能。

Peng指出:“虽然 FPGA 与 Zynq® SoC 技术仍然是我们业务的核心,但赛灵思今后将不再仅仅是一家 FPGA 企业。FPGA技术是我们的传统,我们在此基础上已发展了多年,包括在可编程芯片上全面集成了 SoC,开发出了 3D IC,构建了软件开发框架,并创建了合作伙伴生态系统,为行业提供了独一无二的产品。ACAP 的发明,意味着我们将上述创新提升到了一个新的高度,在当前以及未来我们将为数据中心与我们的主流市场创造更多的价值。”

自从2015年英特尔167亿美元收购FPGA领域老二Altera后,赛灵思一直在不断超越自己,从工艺从架构方面颠覆传统的FPGA ,现在人工智能技术普及、智能化趋势日益明显,新一代自适应计算加速平台ACAP也应运而生了希望ACAP带来更多颠覆性产品。毕竟它的软硬件可编程自适应计算引擎、下一代可编程逻辑单元都是很新的技术,可以适应灵活多变的处理需求。

-

FPGA

+关注

关注

1655文章

22283浏览量

630223 -

晶体管

+关注

关注

78文章

10250浏览量

146259

原文标题:赛灵思还是赛灵思,但是FPGA已经不是原来的FPGA了!

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

MUN5136数字晶体管技术解析与应用指南

电压选择晶体管应用电路第二期

多值电场型电压选择晶体管结构

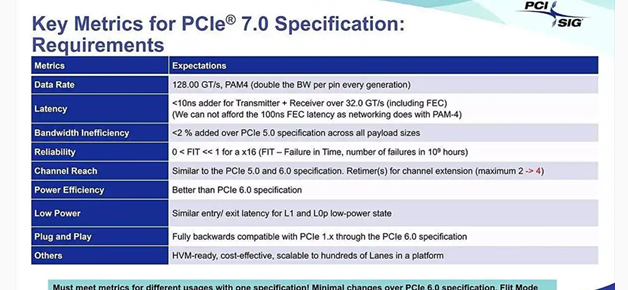

PCIe 7.0技术细节曝光

下一代高速芯片晶体管解制造问题解决了!

多值电场型电压选择晶体管结构

晶体管电路设计(下)

索尼IP编码板:技术细节与应用探索

晶体管电路设计(下) [日 铃木雅臣]

氮化镓晶体管的并联设计技术手册免费下载

晶体管电路设计与制作

PDTD114EU 50V 500mA NPN电阻的晶体管规格书

PDTB114EU 50V、500mA PNP电阻晶体管规格书

500亿晶体管!ACAP技术细节

500亿晶体管!ACAP技术细节

评论