Compute Express Link(CXL)于2019年首次发布,是处理器与AI加速器、内存缓冲区、智能网络接口卡、持久性存储器和固态驱动器等设备之间的开放式行业标准互连技术。作为一种行业标准接口,CXL提升了不同制造商硬件组件之间的互操作性,减少了兼容性问题,为数据中心硬件市场带来了更多样化且更具竞争力的发展环境。

尽管该标准推出至今仅短短5年,然而在此期间,我们所处的世界已发生诸多变化。其中,数据中心与高性能计算环境工作负载的持续增长尤为关键,这为改善人类生活的机器学习与人工智能解决方案的广泛应用提供了有力支撑。

CXL的核心在于提供一致性与内存语义,其带宽能够随PCIe扩展,同时实现远低于PCIe的延迟。在本文中,我们将进一步介绍开发者如何借助符合规范的CXL IP,紧跟技术进步,满足市场需求和持续发展的行业标准。本文将介绍CXL 3.1标准的最新更新内容,包括新增的安全特性,以及如何持续为下一代基础结构提供内存池功能。

CXL标准的演进历程

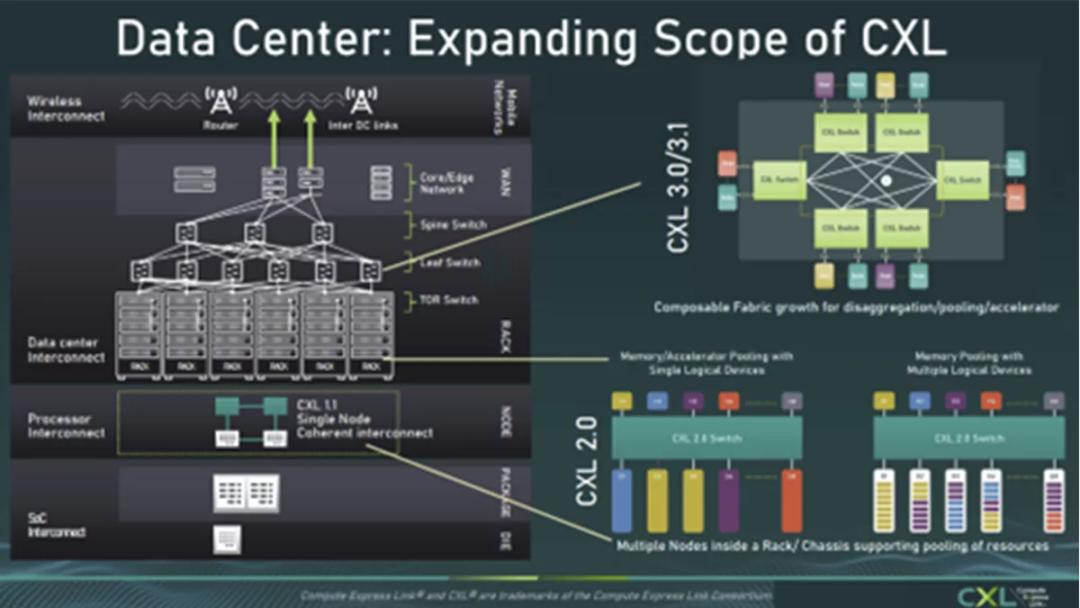

从CXL 2.0到CXL 3.x的演进,标志着在满足行业需求方面取得了重大进展。对更高速度的需求是推动CXL向3.x演进的主要驱动力之一,这与PCIe 6.x的发展方向一致。此外,CXL正朝着更对称的一致性模型转变,这使得连接到CXL的设备能够生成内存周期,并更高效地相互通信。这一改进突破了以主机为中心的传统方法,有助于实现在不同设备之间实现更灵活、高效的内存利用。

始终不变的是,CXL一直是关键的互连技术,能够在CPU、加速器和内存设备之间实现高效、高性能的通信。最新的CXL 3.1规范充分满足了下一代计算中数据密集型应用日益增长的需求。

▲从CXL 2.0过渡到CXL 3.0/3.1。资料来源:CXL联盟

CXL 3.1的主要特性

CXL 3.1标志着互连技术在CXL 3.0的基础上向前迈出了重要一步,它提供了更高的速度、安全性、灵活性和效率,以满足快速增长的行业需求。具体来说,与前代产品相比,CXL 3.1具有以下改进特性:

扩展元数据:每个高速缓存行支持多达32位元数据,以及2位用于缓存一致性的元数据,用于描述缓存行的共享、独占、修改或无效状态。

新用例:从元数据中获取的新信息可用于访问控制、数据类型标记、内存分层算法等用例。

提高CXL内存设备错误可见性:提供关于可更正错误限制、错误来源以及错误发生时所涉事务的新信息。

强化对内存设备RAS的控制:提供内存备用、DDR5错误检查清洗、介质测试、巡逻清洗,以及容量/性能下降相关信息。

可信执行环境安全协议(TSP):使基于虚拟化的TEE能够托管机密性计算工作负载。

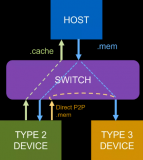

点对点通信:助力加速器实现直接的点对点CXL内存访问,提高资源利用率并减少延迟

虽然这些特性带来了切实的提升,但CXL 3.1也引入了更多复杂性,随之带来了新的挑战。对于任何新标准的发布,应对这些挑战对于确保稳定性和性能至关重要。例如,CXL 3.x采用了256字节FLIT格式(类似于PCIe 6.x)来实现前向纠错,从而减少误码。这一改变对于在更高传输速率下保持数据完整性和性能至关重要。

借助可信执行环境安全协议(TSP)

强化安全性

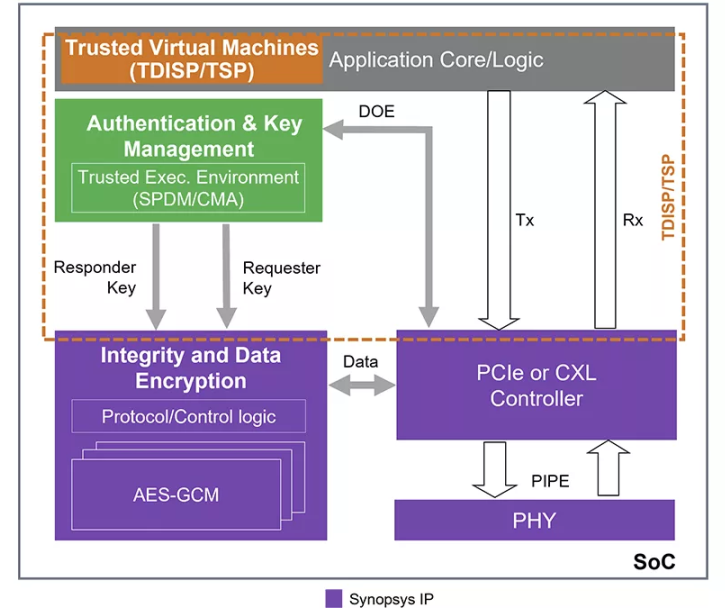

安全性仍然是CXL 3.1标准的基石。具体来说,可信执行环境安全协议(TSP)适用于CXL.cache和CXL.mem,旨在保护基于虚拟化的环境,使其能够托管机密性计算工作负载。该特性基于CXL 2.0中引入的现有完整性和数据加密(IDE)协议,进一步增强了整个接口的数据保护。TSP的整合确保了数据的机密性与完整性,防范虚拟化环境中潜在的安全威胁。在数据日益敏感、法规愈发严格的当下,这一点尤为重要。CXL.io虚拟化支持继续受TEE设备接口安全协议(TDISP)的约束,该协议由PCI-SIG管理,并于2022年8月发布。

这些安全协议共同提升了与协议相关的安全性。凭借在这些领域的深厚专业知识,新思科技能够提供全面的支持,确保实施方案既鲁棒又安全。

CXL 3.1未来的改进方向与新思科技的承诺

展望未来,CXL标准预计将不断改进。行业发展日新月异,新的需求与技术不断涌现。新思科技始终致力于在这些变革中保持领先地位。我们积极参与标准制定过程,不仅确保自身能够迅速适应新特性,还主动为推动这些标准的未来发展贡献力量。

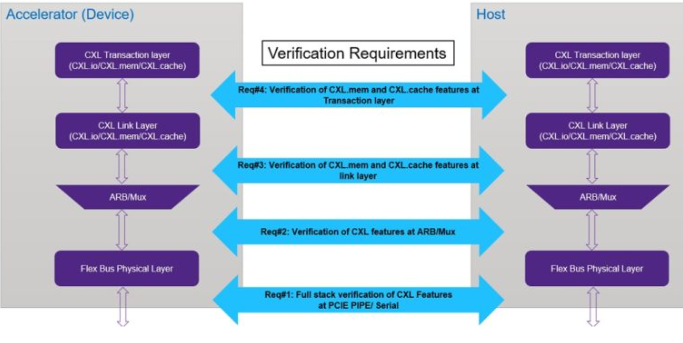

随着CXL的持续发展与变化,新思科技将始终站在前沿,随时准备整合并支持这些技术进步。我们高度关注安全性、性能与适应性,完全有能力助力客户充分释放CXL 3.1及后续版本的潜力。新思科技CXL IP为CXL提供了完整的IP解决方案(包括控制器、PHY、IDE安全模块和验证IP),为人工智能、机器学习和云计算应用提供安全、低延迟且高带宽的互连。为降低风险,新思科技CXL IP解决方案基于新思科技PCI Express IP构建,该IP已在众多应用中得到验证。

-

处理器

+关注

关注

68文章

20148浏览量

247130 -

存储器

+关注

关注

39文章

7714浏览量

170851 -

cpu

+关注

关注

68文章

11216浏览量

222942 -

新思科技

+关注

关注

5文章

923浏览量

52639

原文标题:CXL 3.1:CXL 标准的进阶之路上,如何将互连性能推向新高?

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

互联标准之战,CXL正在走向胜利

【直播回顾】OpenHarmony 3.1 Release版本南北向关键能力解读

一窥CXL协议

一文解析CXL系统架构

CXL事务层的结构是由哪些部分组成的

CXL内存协议介绍

一文详解CXL链路层格式的定义

DesignWare CXL为SoC提供优化的多芯片IP堆栈

新思CXL2.0验证IP,加速连接新一代互联技术

新思科技推出新一代开放标准互联技术CXL

CXL协议和标准介绍, CXL2.0和3.0有什么新功能?

揭开CXL的神秘面纱:概述

新思科技CXL 3.1验证解决方案

第二代AMD Versal Premium系列SoC满足各种CXL应用需求

新思科技解读CXL 3.1标准

新思科技解读CXL 3.1标准

评论