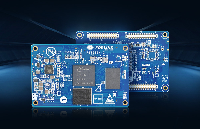

FET113i-S核心板是飞凌嵌入式基于全志T113-i处理器设计的国产工业级核心板,凭借卓越的稳定性和超高性价比,FET113i-S核心板得到了客户朋友们的广泛关注。作为一款拥有A7核+RISC-V核+DSP核的多核异构架构芯片,全志科技于近期释放了T113-i的RISC-V核(玄铁C906)资料,飞凌嵌入式也快速进行了适配。

1、什么是RISC-V?

RISC-V是一种基于精简指令集计算(RISC)原则的开放源代码指令集架构(ISA)。它由加州大学伯克利分校在2010年首次发布,并迅速获得了全球学术界和工业界的广泛关注和支持。RISC-V架构以其开放、简洁、可扩展的特性,正逐渐成为全球半导体产业中一股不可忽视的力量。

2、T113-i的RISC-V有何优势?

高效能与低功耗

RISC-V架构遵循精简指令集计算机的原则,通过简化硬件设计,提高执行效率,降低了开发成本。T113-i处理器中的RISC-V核能够高效地完成各种计算任务,同时保持较低的功耗,非常适合于资源受限的边缘计算环境。

模块化与可扩展性

RISC-V架构设计简洁,采用模块化设计,可以根据需求选择不同的指令集扩展。T113-i处理器中的RISC-V核支持多种标准化扩展指令集,如M(整数乘除法)、A(原子操作)、F/D/Q(单/双/四精度浮点运算)等,可以根据实际应用场景的需要进行灵活组合添加。

开放标准与无授权费用

RISC-V是开源的,允许任何人免费使用和扩展,无需授权费用。这极大地促进了技术的共享和创新,降低了产品的开发成本。

满足实时性需求

在T113-i的A7核、RISC-V核和DSP核可以同时运行,实现一芯多用,异构同时用。这种设计提高了系统的整体性能,并满足了多样化的应用场景需求。其中,RISC-V核可以匹配对实时性要求较高的应用场景,确保系统能够迅速响应并处理各种实时数据。

3、国产化降本的优质之选

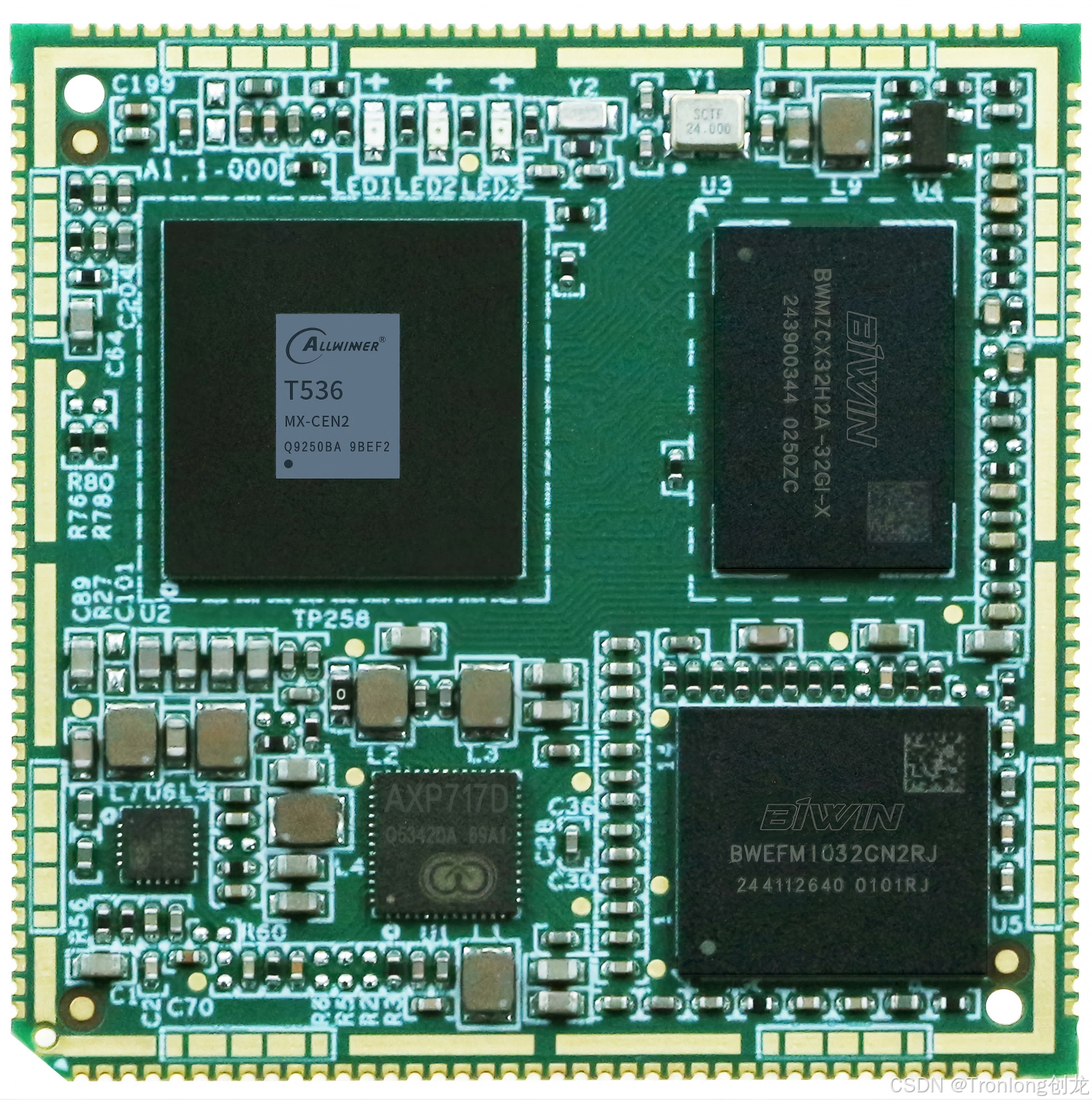

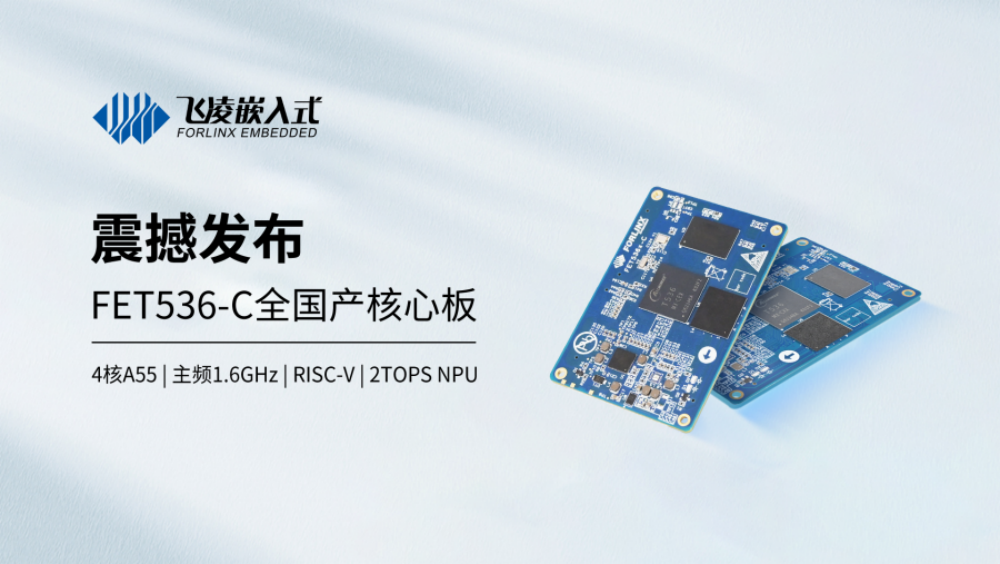

已完成RISC-V核适配的飞凌嵌入式FET113i-S核心板含税最低仅需88元;整板工业级品质使其可以应对更多更复杂的应用场景;全面的外设接口资源也让核心板兼具强大易用性和泛用性;此外,100%的元器件国产化率也意味着安全性和竞争力的提升——FET113i-S核心板是助力新基建领域实现国产化替代升级的优质之选。

不仅产品本身的优势明显,飞凌嵌入式稳定的供应能力与强大的技术支持能力也是帮助客户项目快速落地、抢占市场先机的有利保障。

-

核心板

+关注

关注

6文章

1344浏览量

31763 -

全志

+关注

关注

25文章

302浏览量

54474 -

RISC-V

+关注

关注

48文章

2797浏览量

51925

发布评论请先 登录

【飞凌T527N开发板试用】异构RISC-V核心使用体验

国产!全志T113-i 双核Cortex-A7@1.2GHz 工业开发板—ARM + DSP、RISC-V核间通信开发案例

国产!全志T113-i 双核Cortex-A7@1.2GHz 工业开发板—RISC-V案例开发手册(上)

全志T536(异构多核ARMCortex-A55+玄铁E907 RISC-V)工业核心板说明书

智能配电新纪元:基于飞凌嵌入式T536核心板的DTU解决方案

国产开发板—米尔全志T113-i如何实现ARM+RISC-V+DSP协同计算?

全志 T536工业核心板规格书

SOM-TLT113工业核心板规格书

深度解析 | 基于HPM6450的RISC-V核心板究竟有哪些过人之处?

FET113i-S核心板已支持RISC-V,打造国产化降本的更优解

FET113i-S核心板已支持RISC-V,打造国产化降本的更优解

评论