分频电路是一种电子电路,它的主要功能是接收一个输入信号并产生一个或多个具有特定频率的输出信号,这些输出信号的频率是输入信号频率的整数倍或分数。分频电路广泛应用于时钟信号的产生、无线通信、数字信号处理等领域。

分频电路的基本原理

分频电路的核心原理是周期性地对输入信号进行采样,并根据采样时刻的不同产生不同频率的输出信号。根据输出频率与输入频率的关系,分频电路可以分为整数分频和分数分频两种。

- 整数分频 :输出频率是输入频率的整数分之一,例如2分频、4分频等。

- 分数分频 :输出频率是输入频率的非整数分数,例如3/4分频、5/9分频等。

分频电路的分类

分频电路按照实现方式可以分为模拟分频电路和数字分频电路两大类。

- 模拟分频电路 :通过使用电阻、电容、电感等模拟元件来实现频率的分频。模拟分频电路通常用于低频信号的处理。

- 数字分频电路 :利用数字逻辑电路(如计数器、触发器等)来实现频率的分频。数字分频电路适用于高频信号的处理,且易于实现复杂的分频比。

分频电路的实现方法

- RC分频电路 :使用电阻和电容构成的滤波器来实现分频。RC分频电路简单,但分频精度受元件参数影响较大。

- LC分频电路 :利用电感和电容构成的谐振回路来实现分频。LC分频电路的分频精度较高,但电路复杂,且受元件品质影响。

- 数字计数器分频电路 :使用数字计数器(如二进制计数器、约翰逊计数器等)来实现分频。数字计数器分频电路可以实现任意分频比,且分频精度高,是目前最常用的分频电路。

- 锁相环(PLL)分频电路 :利用锁相环的频率合成功能来实现分频。PLL分频电路具有高稳定性和高精度,但电路复杂,成本较高。

- 开关电容分频电路 :使用开关电容滤波器来实现分频。开关电容分频电路具有模拟分频电路的简单性和数字分频电路的高精度,但需要精确的时钟控制。

分频电路的设计考虑

在设计分频电路时,需要考虑以下几个关键因素:

- 分频比 :根据应用需求确定所需的分频比。

- 输入信号频率 :分频电路需要适应的输入信号频率范围。

- 输出信号频率 :期望得到的输出信号频率。

- 频率稳定性 :分频电路输出信号的频率稳定性。

- 相位噪声 :分频电路引入的相位噪声对系统性能的影响。

- 电源电压 :分频电路工作的电源电压范围。

- 功耗 :分频电路的功耗,尤其是在便携式设备中尤为重要。

- 集成度 :分频电路的集成度,是否需要与其他电路集成在同一芯片上。

结论

分频电路是电子系统中不可或缺的组成部分,它通过周期性地对输入信号进行采样来实现频率的分频。分频电路可以分为模拟分频电路和数字分频电路,其中数字计数器分频电路和PLL分频电路是目前最常用的实现方式。在设计分频电路时,需要综合考虑分频比、输入输出频率、频率稳定性、相位噪声、电源电压、功耗和集成度等因素,以满足特定应用的需求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

锁相环

+关注

关注

36文章

633浏览量

90811 -

分频电路

+关注

关注

7文章

45浏览量

36338 -

时钟信号

+关注

关注

4文章

495浏览量

29695

发布评论请先 登录

相关推荐

热点推荐

音响中软件分频和硬件分频区别解析以及对音质和成本的影响

要理解蓝牙音响中 软件分频 与 硬件分频 的区别,需先明确 “分频” 的核心目的:将音频信号(20Hz-20kHz)拆分为不同频段(如低频、中频、高频),分别驱动对应频段的喇叭单元

CDC5801A低抖动时钟倍频/分频器技术文档总结

CDC5801A器件提供从单端参考时钟 (REFCLK) 到差分输出对 (CLKOUT/CLKOUTB) 的时钟乘法和分频。乘法和分频端子 (MULT/DIV0:1) 提供倍频比和分频比选择,生成

集成整数 N 分频 PLL 和 VCO 的 350-5000 MHz 宽带接收混频器 skyworksinc

电子发烧友网为你提供()集成整数 N 分频 PLL 和 VCO 的 350-5000 MHz 宽带接收混频器相关产品参数、数据手册,更有集成整数 N 分频 PLL 和 VCO 的 350-5000

发表于 05-22 18:31

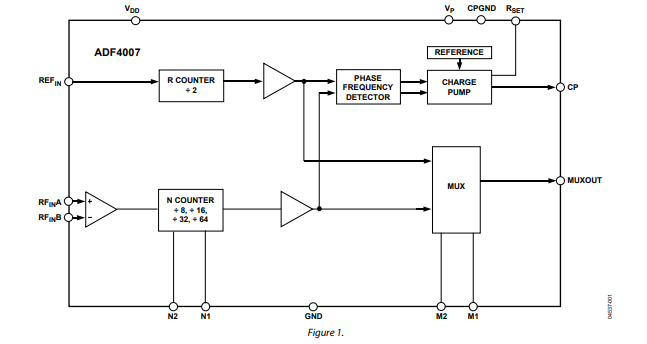

ADF4007高频分频器/PLL频率合成器技术手册

ADF4007是一款高频分频器/PLL频率合成器,可用于各种通信应用。RF端工作频率可达7.5 GHz,PFD端工作频率可达120 MHz。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵和分频

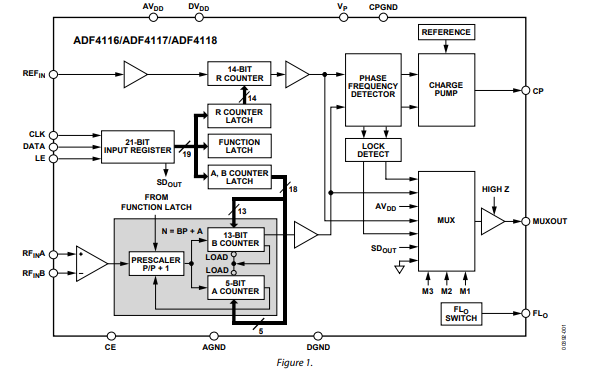

ADF4116/ADF4117/ADF4118单通道、整数N分频550MHz PLL技术手册

ADF4116/ADF4117/ADF4118均为频率合成器,可以用来在无线接收机和发射机的上变频和下变频部分实现本振。上述器件由低噪声数字鉴频鉴相器(PFD)、精密电荷泵、可编程参考分频器、可编程

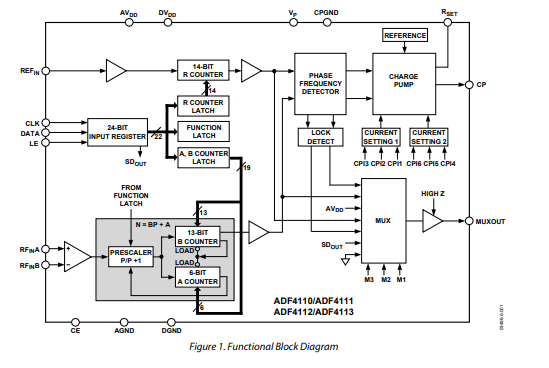

ADF4110/ADF4111/ADF4112/ADF4113单通道、整数N分频、550 MHz PLL,内置可编程预分频器和电荷泵技术手册

ADF4110系列频率合成器在无线接收机和发射机的上变频和下变频部分中,可用来实现本振。上述器件由低噪声数字鉴频鉴相器(PFD)、精密电荷泵、可编程基准分频器、可编程A和B计数器以及双模预分频器(P

ADF4206/ADF4208双通道、整数N分频1.1GHz/2.0 GHz PLL技术手册

ADF4206/ADF4208均为双通道频率合成器,可以用来在无线接收机和发射机的上变频和下变频部分实现本振。上述器件由低噪声数字鉴频鉴相器(PFD)、精密电荷泵、可编程参考分频器、可编程A和B

ADF4156 6.2GHz小数N分频频率合成器技术手册

小数插值器,能够实现可编程小数N分频。INT、FRAC和MOD寄存器可构成一个总N分频器(N = (INT + (FRAC/MOD)))。RF输出相位可通过编程设置,适合要求输出与基准之间存在特定相位关系的应用。ADF4156还具有周跳减少

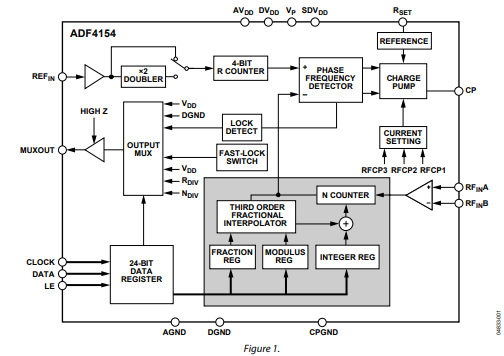

ADF4154小数N分频频率合成器技术手册

ADF4154是一款小数N分频频率合成器,用来在无线接收机和发射机的上变频和下变频部分实现本振。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵和可编程基准分频器组成。该器件内置一个Σ-Δ型小数插值器

ADF4151小数N/整数N分频PLL频率合成器技术手册

ADF4151结合外部电压控制振荡器(VCO)、环路滤波器和外部基准频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。

它能够与外部VCO器件配合使用,且与ADF4350尺寸

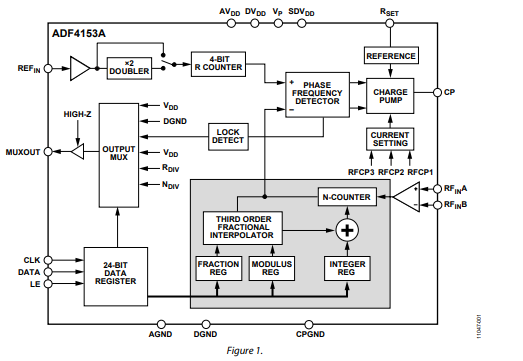

ADF4153A小数N分频频率合成器技术手册

ADF4153A是一款小数N分频频率合成器,用来在无线接收机和发射机的上变频和下变频部分实现本振。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵和可编程参考分频器组成。该器件内置一个Σ-Δ型小数插值

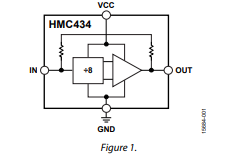

HMC434使用InGaP HBT技术,8分频,采用SMT封装技术手册

HMC434是一款低噪声、静态、8分频预分频器单芯片微波集成电路(MMIC),利用磷化铟镓/砷化镓(InGaP/GaAs)异质结双极性晶体管(HBT)技术,采用超小型6引脚SOT-23表贴封装。

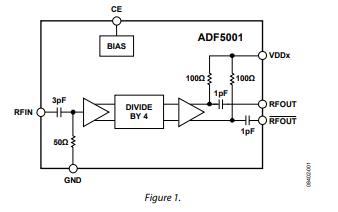

ADF5001 4GHz 至18GHz 4分频预分频器技术手册

ADF5001预分频器是一款低噪声、低功耗、固定RF分频器模块 ,可用来将高达18GHz的频率分频至适合输入到[ADF4156]或 [ADF4106]等PLL IC的较低频率。ADF5001提供4

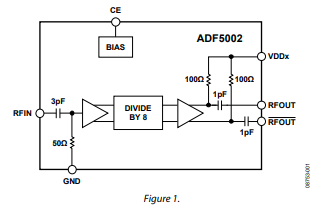

ADF5002 4GHz至18GHz 8分频预分频器技术手册

ADF5002预分频器是一款低噪声、低功耗、固定RF分频器模块,可用来将高达18GHz的频率分频至适合输入到 [ADF4156]或[ADF4106]等PLL IC的较低频率。ADF5002提供8

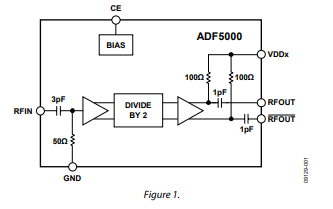

ADF5000 4GHz 至18GHz 2分频预分频器技术手册

ADF5000预分频器是一款低噪声、低功耗、固定RF分频器模块,可用来将高达18 GHz的频率分频至适合输入到[ADF4156]等PLL IC的较低频率。ADF5000提供2分频功能,

什么是分频电路?如何分频呢?

什么是分频电路?如何分频呢?

评论