玻纤效应,作为一种神秘和隐晦的存在,一直都是做高速信号设计的工程师们无法放心的一环。作为一种虽然不一定会发生,但是一发生起来又很影响信号质量的存在,设计工程师和板厂可谓想尽了一切办法去尽量规避。由于Chris自认为自己讲的玻纤效应的原因和解决方法都没有之前高速先生写过的这篇文章《DesignCon文章解读之玻纤效应限制了我们对高速的想象?》讲得好,因此特意翻箱倒柜把这篇文章找出来,让大家对玻纤效应和常规我们正在使用的解决方法有一定的认知!

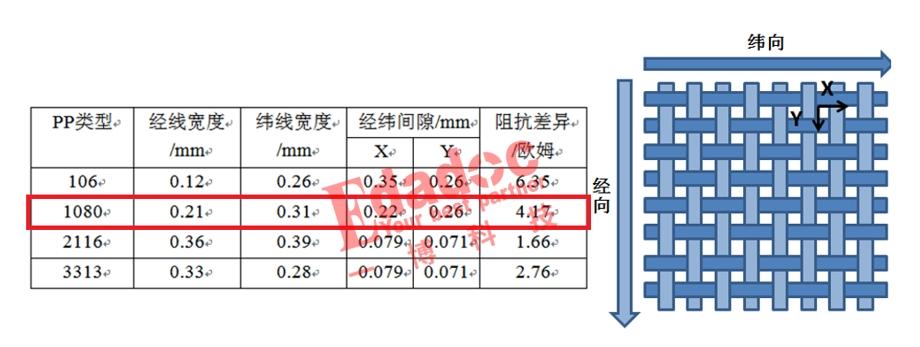

是的,目前用得比较多的几个方法就是要么选用扁平玻纤布的PP和Core,例如1078、1035等,要么就需要设计工程师比较辛苦的把高速信号线做成一定角度的走线,要么就多浪费点板料,让板厂做一定角度的panel旋转。当然上面也说了,玻纤效应其实在某种意义来说是一定会存在的,只是程度轻重的问题。在扁平玻纤布的选用这一块,1078或1035这些好的PP和Core的选择的确能大概率弱化它的影响,但也不是一定,非常非常偶尔的情况下也能看到一个扁平玻纤布存在非常大玻纤效应的case,就好像这篇文章《明明设计的是高带宽,你差点给我加工成开路?》说的一样,也不是做到百分百保险。

Chris最近突然想再进一步研究下玻纤效应,于是也翻阅了行业内相关的文档,看看有没有提到什么更好的解决方案。无意中看到了某大公司提出的尘封已久的设计思路,就是下面这个图的方法!

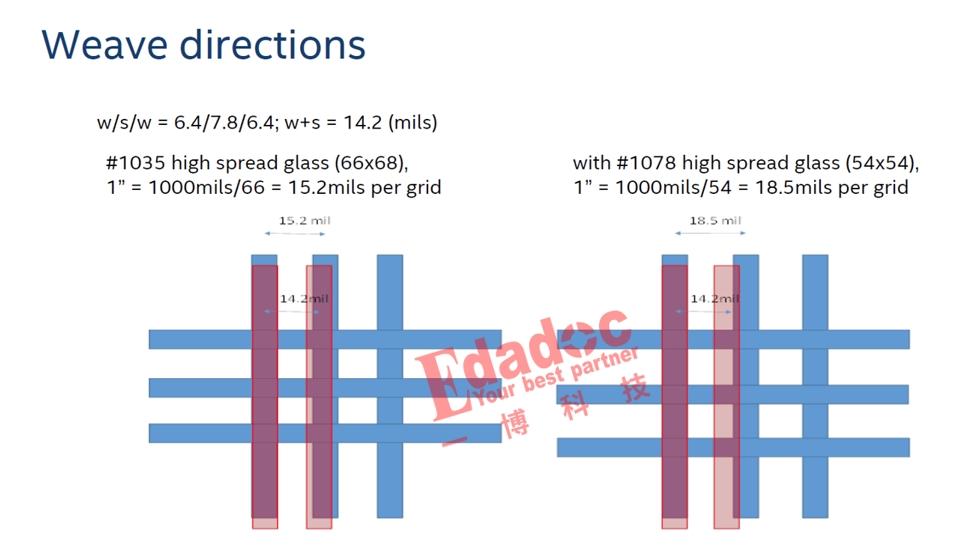

这个思路到底是怎么样的呢?这个方法以1035和1078为例来介绍,我们知道,从理论上来说以某种名字命名的PP和Core,就代表着玻璃布编织的方式是固定的,说白了,它们认为横向和纵向玻纤布的间距是固定的。1035大概是15.2mil的横向间距,1078大概是18.5mil的横向间距。于是提出了这种新的设计思路就是如果差分线的线宽和间距等刚好做到和玻纤布的间距一样的话,那不就是无论走线在玻纤上的哪个位置,差分线间的两根线感受到的变化是完全一样的,这样理论上就没有模态转换的发生,从这个意义上来说也就是不存在玻纤效应了!!!

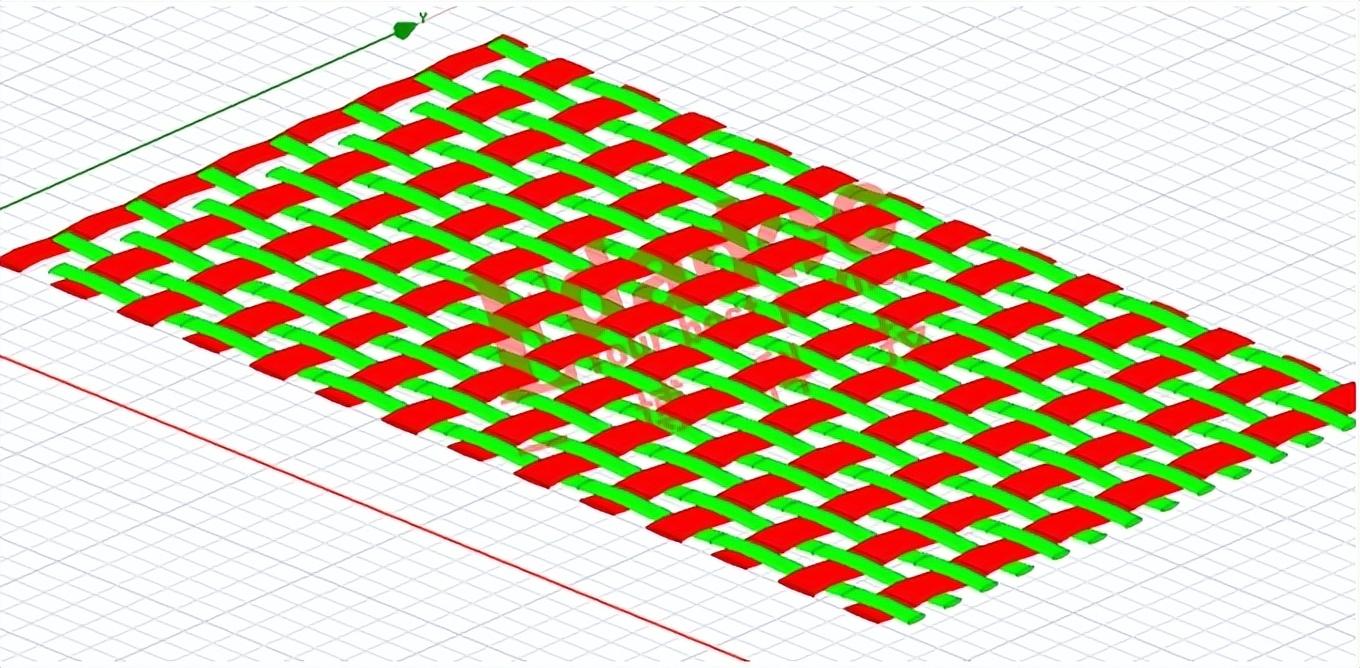

在看到这个方法的第一个moment,Chris感觉也是眼前一亮。作为一个严谨的工程师,Chris就打算试试通过仿真的方式来验证一下这个思路。要玩就拿最差的PP来玩,Chris按照1080PP的规格进行了3D建模,大概建了一个很符合实际的PP的3D模型。

可以看到,1080PP的玻纤窗口是真的大啊!然后我们根据1080的玻纤理论的间距去设计在上面要走的差分线。从拿到的数据来看,1080PP在经线方向上的玻璃布中心间距为17mil的样子。

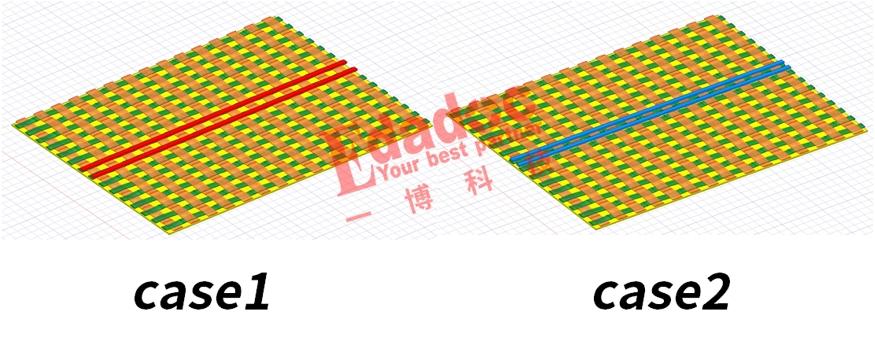

于是我们根据建模PP的厚度,在前提都满足100欧姆阻抗下,设计两组差分线结构。

Case1:线宽5mil,线间距12mil,中心间距17mil,也就是和玻纤间距刚好相同的结构;来验证这个新的设计思路的效果。

Case2:线宽4.5mil,线间距7mil,中心间距11.5mil,不和玻纤间距相同的结构,来作为一组普通的差分线结构,来和case1对比,看看它受到玻纤效应的影响程度。

最终完成的3D模型如下所示。

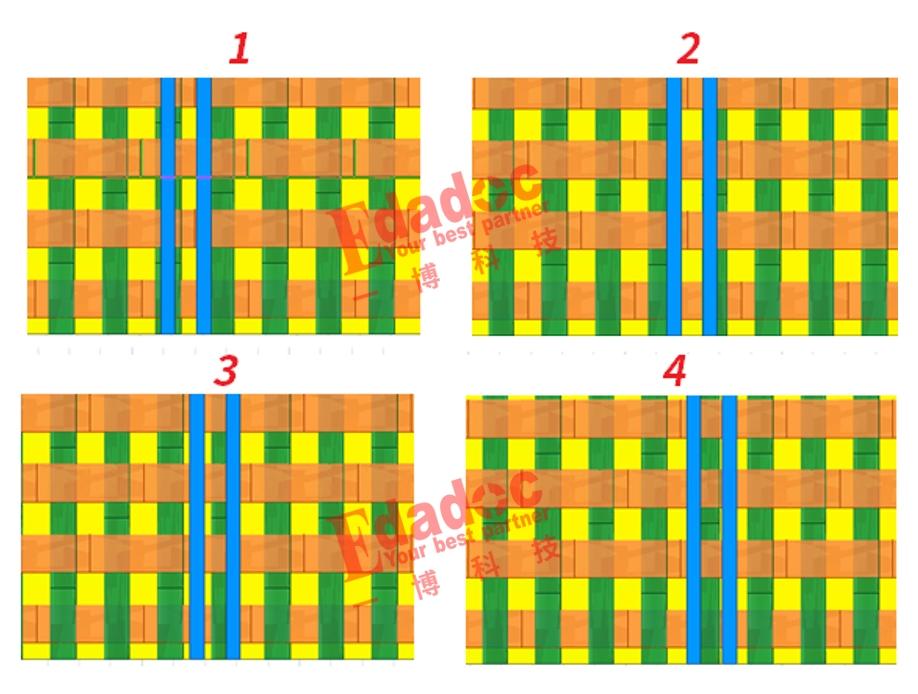

要不我们先来看看case2这种没按照玻纤间距来设计的普通走线的情况?那我们任意的横向移动这对差分线,让它分别存在于PP上的几个不同的位置,例如这样。

哦对了,还有一点忘了提醒,就是两种case的差分线建模的长度都为2inch哈!我们看看只有不长的2inch走线情况下两种case的差异!

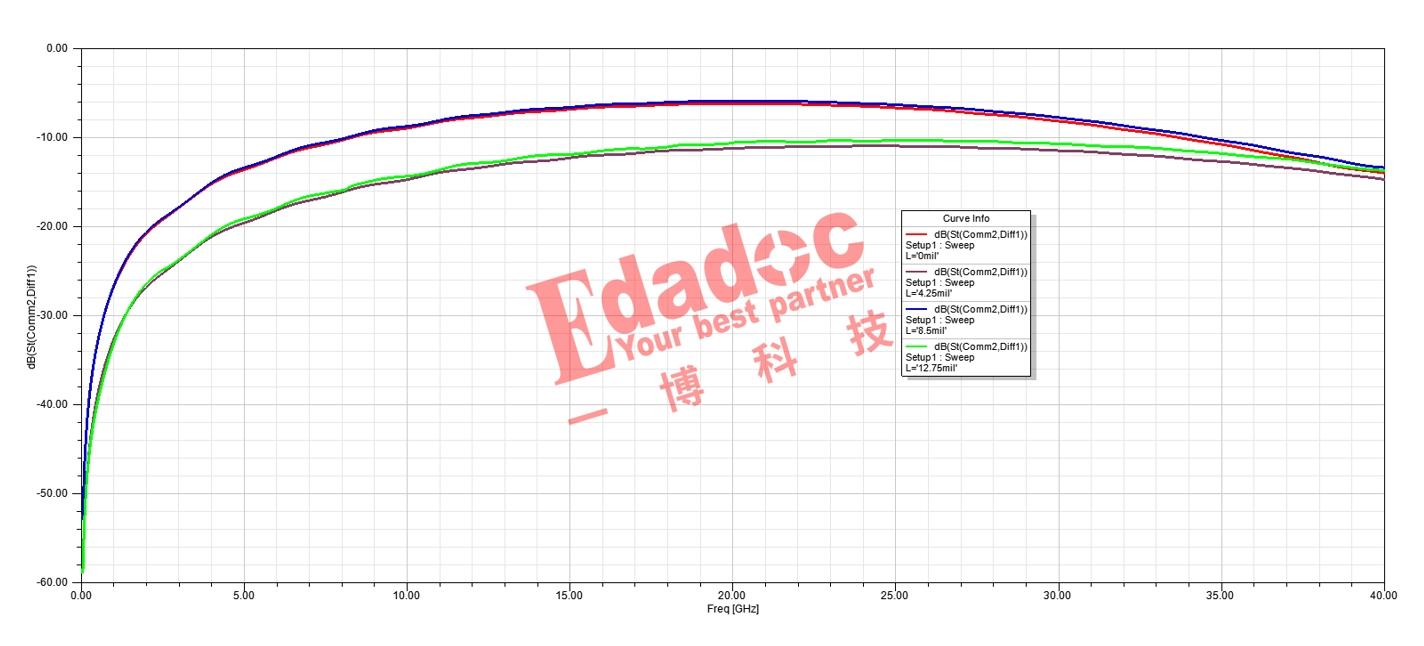

那我们就开始对case2,差分线在上面的4种位置情况下进行无源的仿真,看的指标为模态转换和影响的插入损耗两个主要指标。

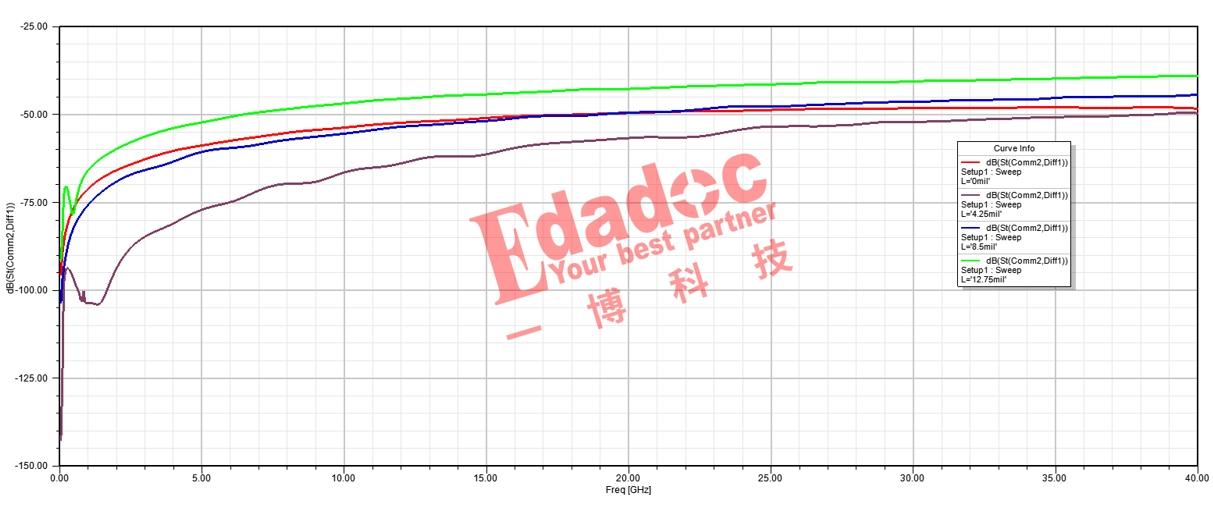

从模态转换上可以看到,4根走线的模态转换都明显受到了玻纤效应的影响,其中在1和3两个状态下的效果更是差!

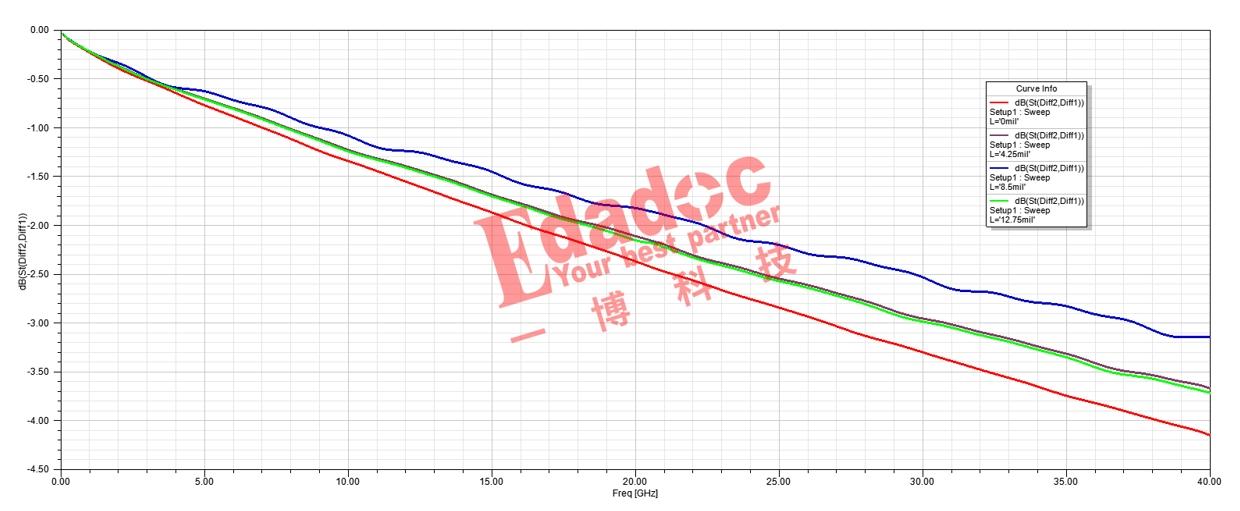

同时能看到对插损的影响也非常的明显。正常的差分走线的情况肯定就不会这个样子了。

没有对比就没有伤害,那我们转头来看看本次的这种新思路设计下的情况,也就是case1的仿真结果。

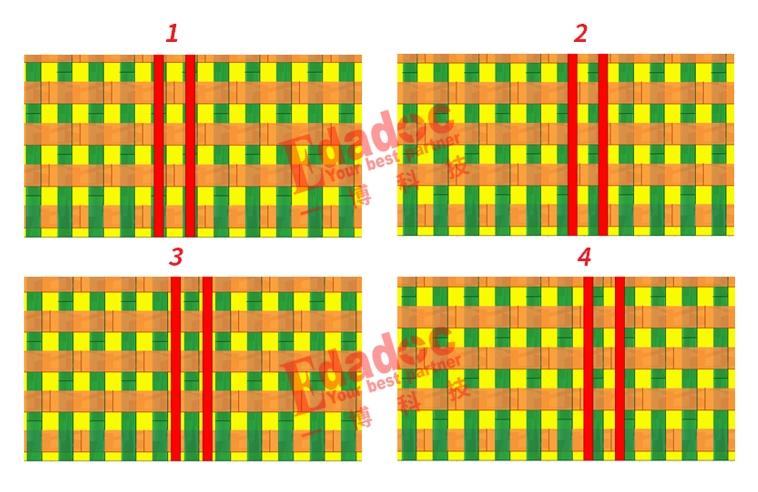

在case1中,移动差分线分布到和case2的4种状态下去分析,如下所示:

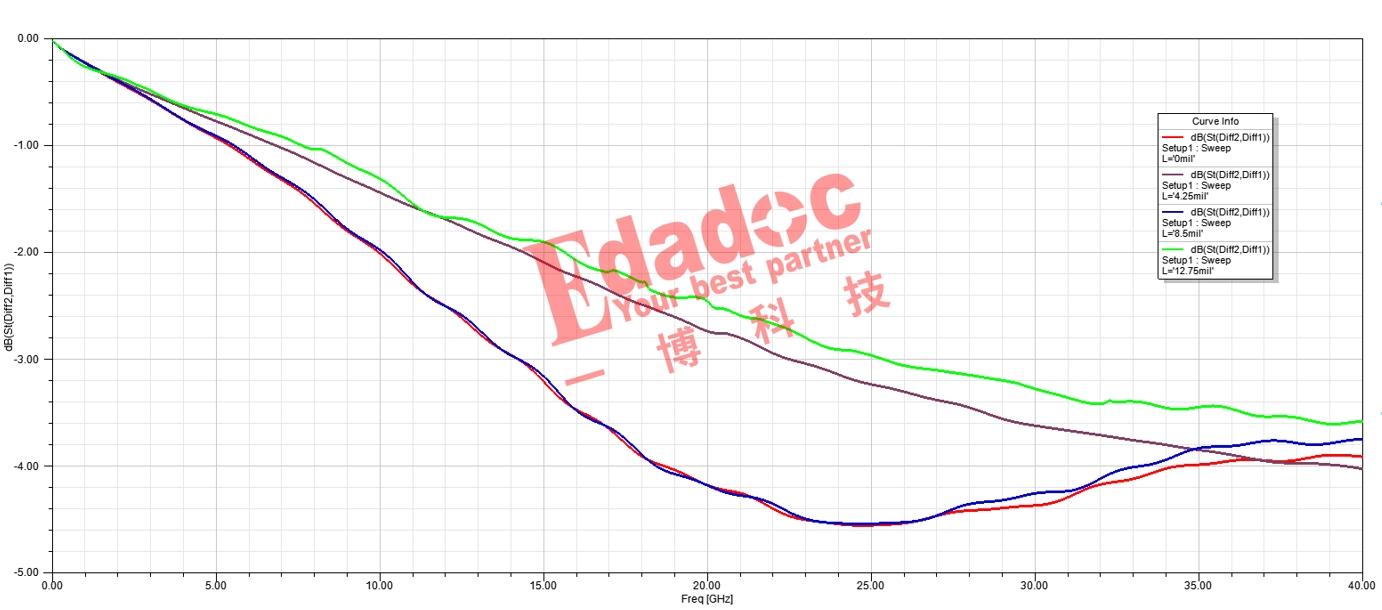

首先我们还是先看看模态转换这个最主要的指标,真的不得不相信,这种新的设计思路真的在仿真中呈现出完美的状态,在4个不同的位置上,模态转换的结果都稳如老狗!全在-40db以下,非常的理想。

这样在插损结果上也能看到我们喜欢的曲线了,一条理想差分线应该有的插损曲线!

Chris向组内分享这个文档后,大家看到了都纷纷表示很棒,都想在后面的项目里尝试下这种设计方法。Chris再细细斟酌之后,还是不由得向大家泼一点点冷水,淡淡的问了大家一句:既然这个理论的方法已经提出了那么多年了,为什么大家却几乎没有在实际的项目中看到过有人这样设计呢?

问题来了?

大家觉得这个理论上很棒的方法,如果实际加工出来会怎么样呢?问题非常开放,没有对错,希望大家踊跃回答哈!

审核编辑 黄宇

-

仿真

+关注

关注

53文章

4406浏览量

137670 -

高速PCB

+关注

关注

4文章

102浏览量

25641 -

PCB

+关注

关注

1文章

2264浏览量

13204

发布评论请先 登录

深度解读PCB设计布局准则

好吧,高速先生承认这个PCB设计方法的确有点意思,但是不多!

好吧,高速先生承认这个PCB设计方法的确有点意思,但是不多!

评论