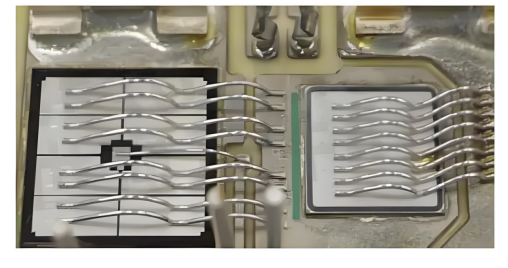

引线键合是封装过程中一道关键的工艺,键合的质量好坏直接关系到整个封装器件的性能和可靠性,半导体器件的失效约有1/4~1/3是由芯片互连引起的,故芯片互连对器件长期使用的可靠性影响很大。引线键合技术也直接影响到封装的总厚度。下面科准测控小编就来介绍一下半导体集成电路键合强度试验原理、试验程序、试验条件、设备、失效判断及说明!

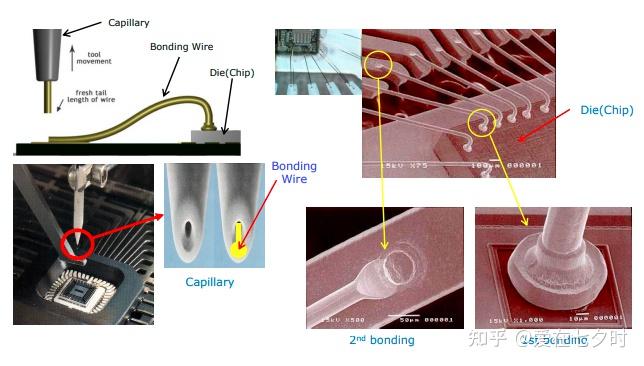

一、什么是键合(Wire Bonding)

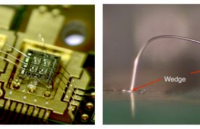

键合就是用金丝、铜丝或铝丝将半导体器件芯片表面的电极引线与底座或引线框架外引线相连接起来。键合的目的是把半导体器件芯片表面的电极与引线框架的外引线连接起来。

二、试验原理

本试验的目的是测量键合强度,评估键合强度分布或测定键合强度是否符合适用的订购文件的要求。本试验可应用于采用低温焊、热压焊、超声焊或有关技术键合的、具有内引线的微电子器件封装内部的引线-芯片键合、引线-基板键合或内引线-封装引线键合。它也可应用于器件的外部键合,如器件外引线-基板或布线板的键合,或应用于不采用内引线的器件(如梁式引线或倒装片器件)中的芯片-基板之间的内部键合。

三、试验程序

应采用与特定器件结构相符的、适用订购文件中规定的试验条件进行试验。应计算全部键合拉力,并应根据适用情况遵守抽样、接收和追加样品规定。除另有规定外,对于条件A、C和D,所需要的试验键合点应从至少四个器件中随机抽取,为键合强度试验规定的样本大小用于确定进行拉力试验的最少键合线数,而不是确定至少需要的完整器件数。按试验条件以D、F、G和H进行的键合拉力试验,虽然同时涉及到两个或多个键合点,但是对键合强度试验和计算样本大小来说,应将其看成是一个拉力试验。除另有规定外,按照试验条件F、G和H的键合拉力试验规定的样本大小用于确定被试验的芯片的数量,而不是键合数。对于混合或者多芯片器件(无论哪种条件)而言,应至少采用四个芯片,或者如果二个完整的器件上不足四个芯片,那么应采用全部芯片。在芯片下面、芯片上面或芯片周围,若存在任何导致增加表面键合强度的粘附剂、密封剂或其他材料,应在使用这些材料前进行键合强度试验。

当倒装片或梁式引线芯片是与基板键合而不是在成品器件中的键合时,则应采用下述条件∶

a) 从与成品器件中采用的芯片属于同一批的芯片中,随机抽取本试验用的芯片样本;

b) 在键合成品器件的同一期间内,使用与键合成品器件时相同的键合设备键合用于本试验的芯片

c) 在处理成品器件基板的同一期间内,对试验芯片基板进行与成品器件基板相同的加工、金属化和有关处理。

四、试验条件

1、试验条件A--键合拉脱

本试验通常用于器件封装的外部键合。在固定引线或外引线以及器件的外壳时,应在引线或外引线以及布线板或基板之间,以某一角度施加拉力。除另有规定外,该角度为90°。当出现失效时,应记录引起失效的力的大小和失效类别。

2、试验条件C-引线拉力(单个键合点)

本试验通常应用于微电子器件的芯片或基板以及引线框架上的内部键合。连接芯片或基板的引线应被切断,以使两端都能进行拉力试验。在引线较短的情况下,有必要靠近某一端切断导线,以便在另一端可以进行拉力试验。把导线固定于适当的装置,然后对引线或夹紧引线的装置施加拉力,其作用力大致垂直于芯片表面或基板。当出现失效时,记录引起失效的力的大小和失效类别。

3、试验条件D-引线拉力(双键合点)

此试验的步骤与试验条件C相同,只是现在是在引线(该引线与芯片、基板或底座或两个端点相连)下方插入一个钩子夹紧器件,大约在引线中央施加拉力。该力方向与芯片或基板表面垂直,或与两键合垫肩的直线大致垂直。当出现失效时,记录引起失效的力的大小和失效类别。表1给出最小键合强度。图1用于确定表1中未说明的引线直径的最小键合强度。对引线直径或者等效横截面大于127μm,在引线下不适于使用钩子的地方,可用一个适当的夹子取代钩子。

4、试验条件F一键合剪切力(倒装焊)

本试验通常用于半导体芯片与基板之间以面键合结构进行连接的内部键合,它也可用来试验基板和安装芯片的中间载体或子基板之间的键合。用适当的工具或劈刀正好在位于主基板之上的位置与芯片(或载体)接触,在垂直于芯片或载体的一个边界并平行于主基板的方向上施加外力,由剪切力引起键合失效。当出现失效时,记录失效时力的大小和失效类别。

5、试验条件G-推开试验(梁式引线)

本试验通常用来进行工艺控制,并采用键合到一特别准备的基板上的半导体芯片样品进行试验,因此不能用于产品或检验批的随机抽样试验。试验时应采用带有小孔的金属化基板,这个接近中心位置的小孔应足够大,从而为推压工具提供间隙,但是又不能大到影响键合区。推压工具应足够大,以使在试验期间的器件断裂减到最小,但又不能大到与固定键合区的梁式引线相碰。应按下述方式进行推开试验∶牢固固定基板并穿过小孔插入推压工具,以小于0.25mm/min的速率实现推压工具与硅器件的接触(这样不会产生明显冲击),并以恒定速率对键合器件下侧加力。当失效出现时,记录失效时力的大小和失效类别。

6、试验条件H-拉开试验(梁式引线)

本试验通常应用在以抽样方式测试陶瓷或其他合适的基板上键合的梁式引线。经过校准的拉开设备包括一个拉开杆(例如镍铬或可伐合金线的环),通过粘胶材料(例如热敏聚乙烯醋酸盐树酯胶)与梁式引线芯片的背部(顶侧)牢固连接。把基板牢固地装在拉开夹具中,而拉开杆和粘胶材料保持牢固的机械连接,在垂直方向的5°内施加应力,其值应不小于计算的应力大小(见第六条)或者直到把芯片拉倒离开基板2.54mm为止。当失效出现时,记录失效时力的大小、计算力的极限值和失效类别。

五、推拉力测试机试验设备:

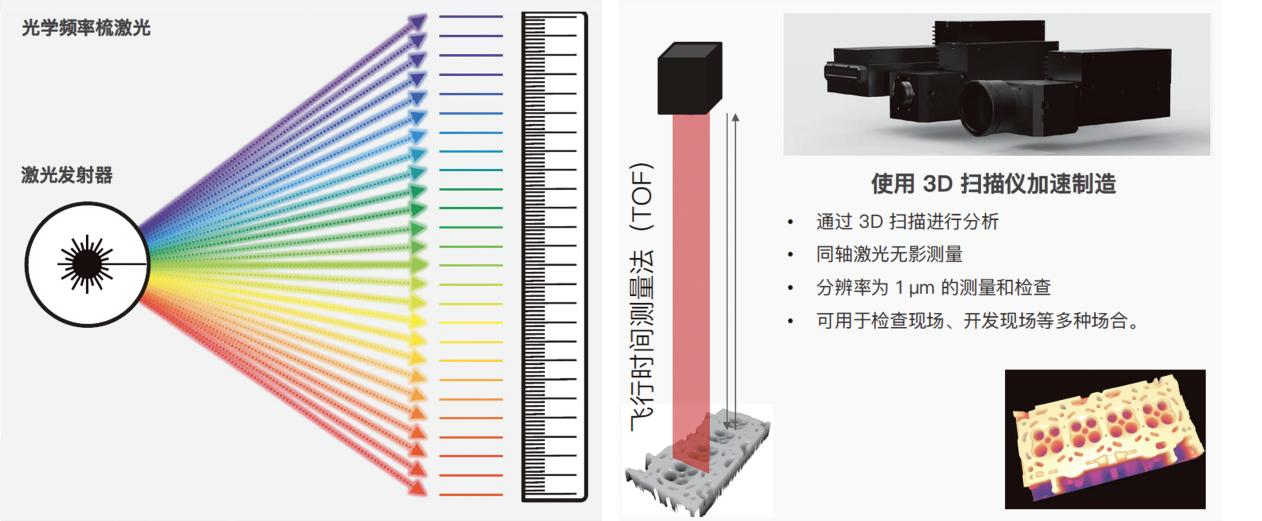

科准测控多功能推拉力机是用于为微电子引线键合后引线焊接强度测试、焊点与基板表面粘接力测试及其失效分析领域的专用动态测试仪器,常见的测试有晶片推力、金球推力、金线拉力等,采用高速力值采集系统。根据测试需要更换相对应的测试模组,系统自动识别模组量程。可以灵活得应用到不同产品的测试,每个工位独立设置安全高度位及安全限速,防止误操作对测试针头造成损坏。且具有测试动作迅速、准确、适用面广的特点。适用于半导体IC封装测试、LED 封装测试、光电子器件封装测试、PCBA电子组装测试、汽车电子、航空航天、军工等等。亦可用于各种电子分析及研究单位失效分析领域以及各类院校教学和研究。

六、失效判据

试验中,若外加应力小于表1中指定的试验条件、组成和结构所要求的最小键合强度时出现键合的分离,则为失效。

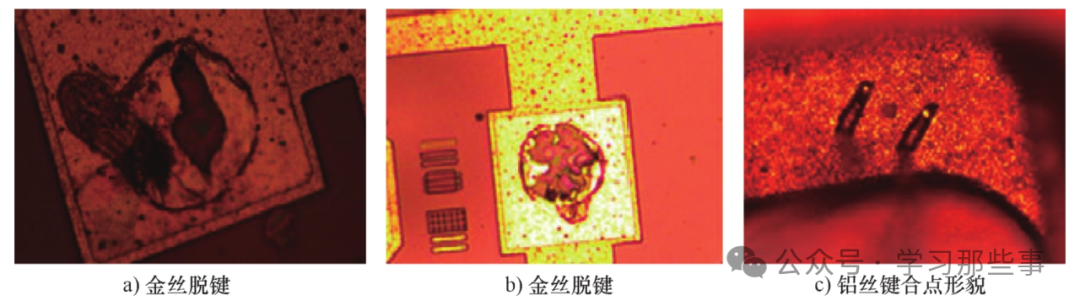

6.1、失效类别

当有规定时,应记录造成分离所需要的应力,以及分离或失效类别。失效分类如下∶

a)对于内引线键合∶

1) 在颈缩点处(即由于键合工艺而使内引线截面减小的位置)引线断开;

2) 在非颈缩点上引线断开;

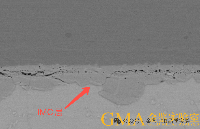

3) 芯片上的键合(在引线和金属化层之间的界面)失效;

4) 在基板、封装外引线键台区或非芯片位置上的键合(引线和金属化层之间的界面)失效;

5) 金属化层从芯片上浮起;

6) 金属化层从基板或封装外引线键合区上浮起;7) 芯片破裂8) 基板破裂。

b)对于连接器件与电路板或基板的外部键合∶

1) 在变形处(受键合影响的部位)的外引线或引出端断开;

2) 在未受键合工艺影响的外引线或引出端断开;

3) 键合界面(在进行键合的外引线或引出端和布线板或基板导体间的低温焊或熔焊交界面)

失效

- 金属化导体从布线板或基板上浮起;

- 布线板或基板内部断裂。

c) 对于倒装片结构∶

1) 键合材料或基板键合区(适用时)的失效;

2) 芯片(或载体)或基板的破裂(紧靠在键合处下面的芯片或基板失掉一部分);3) 金属化层浮起(金属化层或基板键合区与芯片、载体或基板分离)。

d) 对于梁式引线器件∶

1) 硅片破碎

2) 梁在硅片上浮起;

3) 键合处梁断裂;

4) 硅片边缘处梁断裂;

5) 梁在键合处和硅片边线之间断裂;

6) 键合点浮起

7) 金属化层从芯片上浮起(金属化层分离),键合区的分离;

8) 金属化层浮起

注∶射频微波混合电路要求键合引线平直,这可能引起不正确的引线拉力数据。可运用下述公式确定合适的

引线拉力值∶

此外对射频/微波混合电路中含有不能采用拉力钩的引线,必须复制测试试样,使拉力钩可以接入,达到拉力试验的目的。为此,应该在键合混合电路产品的同时,采用同样设备、操作者和步骤键合作为试样的引线。对试验样引线进行拉力测试,以取代混合电路上的调谐引线或难以接近的引线的测试。试样的失效被认为是产品的失效,并应按照适用规范考虑采取合适的处理措施(见图3)。

七、说明

有关的订购文件应规定以下内容∶

a) 试验条件类别的字母代号;

b) 如果不按条六规定,应规定最小键合强度或规定所需强度分布的细节(需要时);

c) 采用的样本数、接收数或对每一个器件规定拉力试验的数目和选取方法。如果被试器件不是

4个,还应规定器件数目

d) 对于试验条件A,如果施加于键合上使其脱落的应力角度不是90°,应规定其角度和键合强度

极限值(见第六条);

e) 需要时,给出分离力和失效类别报告的要求(见6.1)。

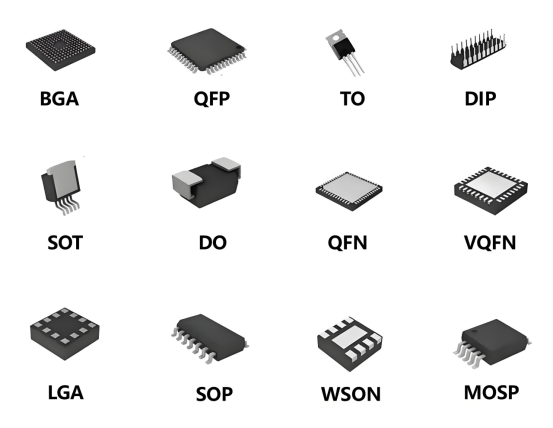

以上就是编给大家带来的半导体集成电路键合强度的测试介绍,以上包含测试原理、程序、试验条件、说明等,希望能给大家带来帮助!科准专注于推拉力测试机研发、生产、销售。广泛用于与LED封装测试、IC半导体封装测试、TO封装测试、IGBT功率模块封装测试、光电子元器件封装测试、大尺寸PCB测试、MINI面板测试、大尺寸样品测试、汽车领域、航天航空领域、军工产品测试、研究机构的测试及各类院校的测试研究等应用。如果您有遇到任何有关推拉力机、半导体集成电路等问题,欢迎给我们私信或留言,科准的技术团队也会为您免费解答!

审核编辑 黄昊宇

-

芯片

+关注

关注

462文章

53550浏览量

459272 -

半导体

+关注

关注

336文章

29999浏览量

258453

发布评论请先 登录

半导体“金(Au)丝引线键合”失效机理分析、预防及改善的详解;

超低频交流耐压试验是什么?

半导体“楔形键合(Wedge Bonding)”工艺技术的详解;

基于焊接强度测试机的IC铝带键合强度全流程检测方案

探秘键合点失效:推拉力测试机在半导体失效分析中的核心应用

IGBT 芯片平整度差,引发键合线与芯片连接部位应力集中,键合失效

现代集成电路半导体器件

银线二焊键合点剥离失效原因:镀银层结合力差VS银线键合工艺待优化!

键合线剪切试验——确保汽车电子产品的可靠连接

低气压试验箱:揭秘集成电路在高原与航空环境下的失效机制

带你一文了解什么是引线键合(WireBonding)技术?

半导体集成电路键合强度原理、试验程序、试验条件、失效判据分享!

半导体集成电路键合强度原理、试验程序、试验条件、失效判据分享!

评论