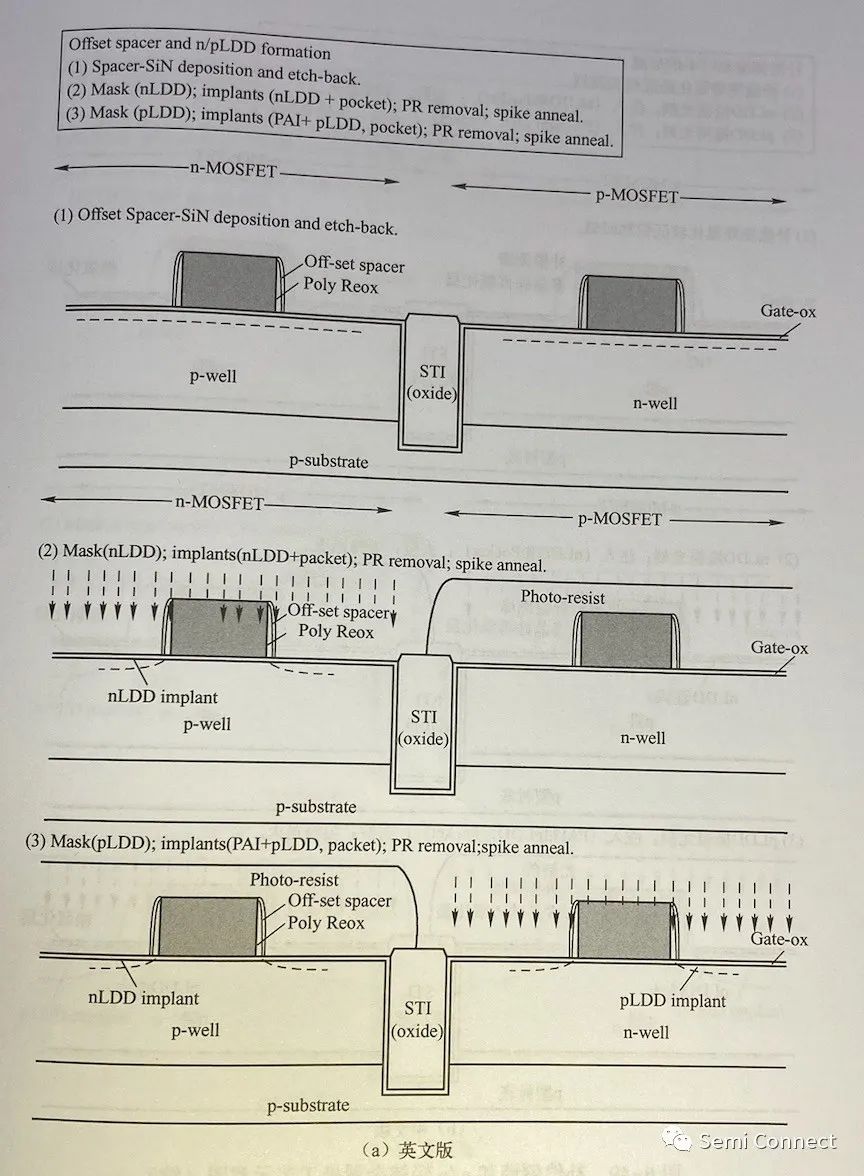

补偿侧墙 (Offset Spacer)和n/p 轻摻杂漏极 (n/ pLDD)工艺

补偿侧墙和 n/p 轻摻杂漏极工艺示意图如图所示。

首先沉积一薄层氮化硅或氮氧化硅(通常约2nm),然后进行回刻蚀(etch-Back),在栅的侧壁上形成一个薄层侧墙(Spacer)。在补偿侧墙刻蚀后,剩下的氧化层厚度约为 2nm。 在硅表面保留的这一层氧化层,在后续每步工艺中将发挥重要的保护作用。补偿侧墙用于隔开和补偿由于 LDD 离子注入(为了减弱短沟道效应)引起的横向扩散,对于 45nm/28nm 或更先进的节点,这一步是必要的。 然后分别对n-MOS和 p-MOS 进行轻掺杂漏极(LDD)离子注入。完成离子注入后,用尖峰退火(Spike Anneal)技术去除缺陷并激活 LDD 注入的杂质。nLDD 和pLDD离子注入的顺序、能量、剂量,以及尖峰退火或 RTA 的温度,对晶体管的性能都有重要的影响。

审核编辑 :李倩

-

LDD

+关注

关注

0文章

13浏览量

12960 -

氧化层

+关注

关注

0文章

4浏览量

5774

原文标题:前段集成工艺(FEOL)-4

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

集成电路制造中薄膜刻蚀的概念和工艺流程

半导体外延工艺在哪个阶段进行的

半导体分层工艺的简单介绍

概伦电子集成电路工艺与设计验证评估平台ME-Pro介绍

集成电路工艺中的金属介绍

集成电路新突破:HKMG工艺引领性能革命

前段集成工艺(FEOL)-4

前段集成工艺(FEOL)-4

评论