FPGA配置基本介绍

与CPLD不同,FPGA是基于门阵列方式为用户提供可编程资源的,其内部逻辑结构的形成是由配置数据决定的。FPGA的配置方式分为主动式和被动式。

1配置引脚

FPGA的配置引脚可分为两类:专用配置引脚和非专用配置引脚。专用配置引脚只有在配置时起作用,而非专用配置引脚在配置完成后则可以作为普通的I/O口使用。

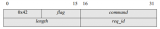

专用的配置引脚有:配置模式脚M2、M1、M0;配置时钟CCLK;配置逻辑异步复位PROG,启动控制DONE及边界扫描TDI,TDO,TMS,TCK。非专用配置引脚有Din,D0:D7,CS,WRITE,BUSY,INIT。

在不同的配置模式下,配置时钟CCLK可由FPGA内部产生,也可以由外部控制电路提供。

2配置过程

(1)初始化

系统上电后,如果FPGA满足以下条件:Bank2的I/O输出驱动电压Vcc0_2大于lv;器件内部的供电电压Vccint为2.5v,器件便会自动进行初始化。在系统上电的情况下,通过对PROG引脚置低电子,便可以对FPGA进行重新配置。初始化过程完成后,DONE信号将会变低。

(2)清空配置存储器

在完成初始化过程后,器件会将INIT信号置低电平,同时开始清空配置存储器。在清空完配置存储器后,INIT信号将会重新被置为高电平。用户可以通过将PROG或INIT信号(1NIT为双向信号)置为低电平,从而达到延长清空配置存储器的时间,以确保存储器被清空的目的。

(3)加载配置数据

配置存储器的清空完成后,器件对配置模式脚M2、N1、M0进行采样,以确定用何种方式来加载配置数据。

(4)CRC错误检查

器件在加载配置数据的同时,会根据一定的算法产生一个CRC值,这个值将会和配置文件中内置的CRC值进行比较,如果两者不一致,则说明加载发生错误,INIT引脚将会被置低电平,加载过程被中断。此时若要进行重新配置,只需将PROG置为低电平即可。

(5)START-UP

在START-UP阶段中,FPGA会进行一下操作:

①将DONE信号置高电平,若DONE信号没有置高,则说明数据加载过程失败;

②在配置过程中,器件的所有I/O引脚均为三态,此时,全局三态信号GTS置低电平,这些I/O脚将会从三态切换到用户设置的状态;

③全局复位信号GSR置低电平,所有触发器进入工作状态;

④全局写允许信号GWE置低电平,所有内部RAM有效;

整个过程共有8个时钟周期C0-C7。在默认的情况下,这些操作都和配置时钟CCLK同步,在DONE信号置高电子之前,GTS,GSR,GWE都保持高电平。

审核编辑 :李倩

-

FPGA

+关注

关注

1655文章

22283浏览量

630223 -

存储器

+关注

关注

39文章

7714浏览量

170848

原文标题:浅析FPGA的配置引脚以及配置过程

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

AMD利用可重构FPGA设备Moku实现自定义激光探测解决方案

Xilinx FPGA串行通信协议介绍

HbirdV2-SoC自带pwm配置介绍

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

一文详解xilinx 7系列FPGA配置技巧

AI狂飙, FPGA会掉队吗? (中)

易灵思 FPGA TJ375的PLL的动态配置

Altera Agilex 3 FPGA和SoC产品介绍

FPGA芯片的概念和结构

MRAM存储替代闪存,FPGA升级新技术

基于FPGA的GigE Vision相机图像采集方案设计

用FPGA配置ADS5562怎么确认寄存器是否配置正常?

基于Agilex 5 FPGA的模块系统介绍

FPGA配置基本介绍

FPGA配置基本介绍

评论