Cadence 和 Samsung Foundry 持续合作,致力于实现低功耗 IC 设计和验证

中国上海,2022 年 10 月 14 日 —— 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,Cadence Voltus-XFi Custom Power Integrity Solution 现已经过优化和认证,可用于 Samsung Foundry 的先进 5LPE 工艺技术。双方的共同客户可以放心地将 Cadence Voltus-XFi 解决方案与 Samsung Foundry 的 PDK 集成,为下一代超大规模计算、移动、汽车和人工智能应用打造卓越的集成电路。

这一最新认证是 Cadence 和 Samsung Foundry 之间持续合作的成果,确保客户能够获得所需的先进设计软件,利用半导体代工技术的最新进展打造新的集成电路。Voltus-XFi 解决方案支持 Cadence 智能系统设计(Intelligent System Design)战略,旨在实现卓越设计。

Cadence 推出 Voltus-XFi 解决方案,旨在帮助客户有效地提取、仿真、分析和调试集成电路设计。利用 Samsung Foundry 推荐的设置,整合后的 EM-IR 集控中心为客户提供了一个完整的工作流程——从 Cadence 的 Quantus Extraction Solution、Spectre X Simulator 和 Virtuoso ADE Product Suite,到 Virtuoso Layout Suite。

Voltus-XFi 解决方案配备直观的 EM-IR 结果浏览器,可以汇总 EM-IR 信息,高亮显示违规行为,以及详细的电阻值、金属层、宽度和长度信息。之后,可在 Virtuoso Layout 中直接标注 EM-IR 结果,方便工程师识别和修复问题区域。

“通过与 Cadence 的长期合作,我们可以为客户提供强大、领先的集成电路设计工具,以便在我们最先进的代工工艺上快速、高效地开发芯片,”三星电子代工设计技术团队副总裁 Sang-Yun Kim 说,“Cadence 和三星之间的合作确保客户能够借助 Voltus-XFi 解决方案,利用我们最新的 5LPE 技术加速完成设计。”

“我们将继续与 Samsung Foundry 密切合作,为客户提供先进的半导体设计、验证和制造技术,帮助他们打造出满足新兴应用需求的集成电路,”Cadence公司高级副总裁兼定制 IC 与 PCB 事业部总经理 Tom Beckley 说,“Voltus-XFi 解决方案通过了三星的认证,今后客户可以利用三星先进的 5LPE 代工技术的高性能和低能耗优势,设计出创新的新型集成电路。”

-

半导体

+关注

关注

336文章

29977浏览量

258151 -

Cadence

+关注

关注

68文章

999浏览量

146198 -

人工智能

+关注

关注

1813文章

49734浏览量

261478

原文标题:Cadence Voltus-XFi 定制化电源完整性解决方案获得 Samsung Foundry 认证,可用于5LPE工艺技术

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

热压键合工艺的技术原理和流程详解

芯源EEPROM产品的优势

芯片键合工艺技术介绍

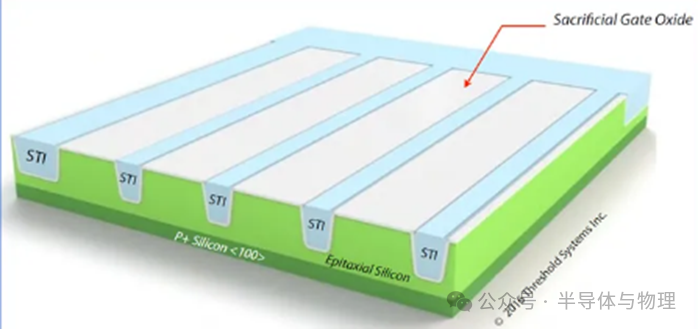

SOI工艺技术介绍

Cadence AI芯片与3D-IC设计流程支持台积公司N2和A16工艺技术

Cadence携手台积公司,推出经过其A16和N2P工艺技术认证的设计解决方案,推动 AI 和 3D-IC芯片设计发展

半导体刻蚀工艺技术-icp介绍

BiCMOS工艺技术解析

Cadence UCIe IP在Samsung Foundry的5nm汽车工艺上实现流片成功

最全最详尽的半导体制造技术资料,涵盖晶圆工艺到后端封测

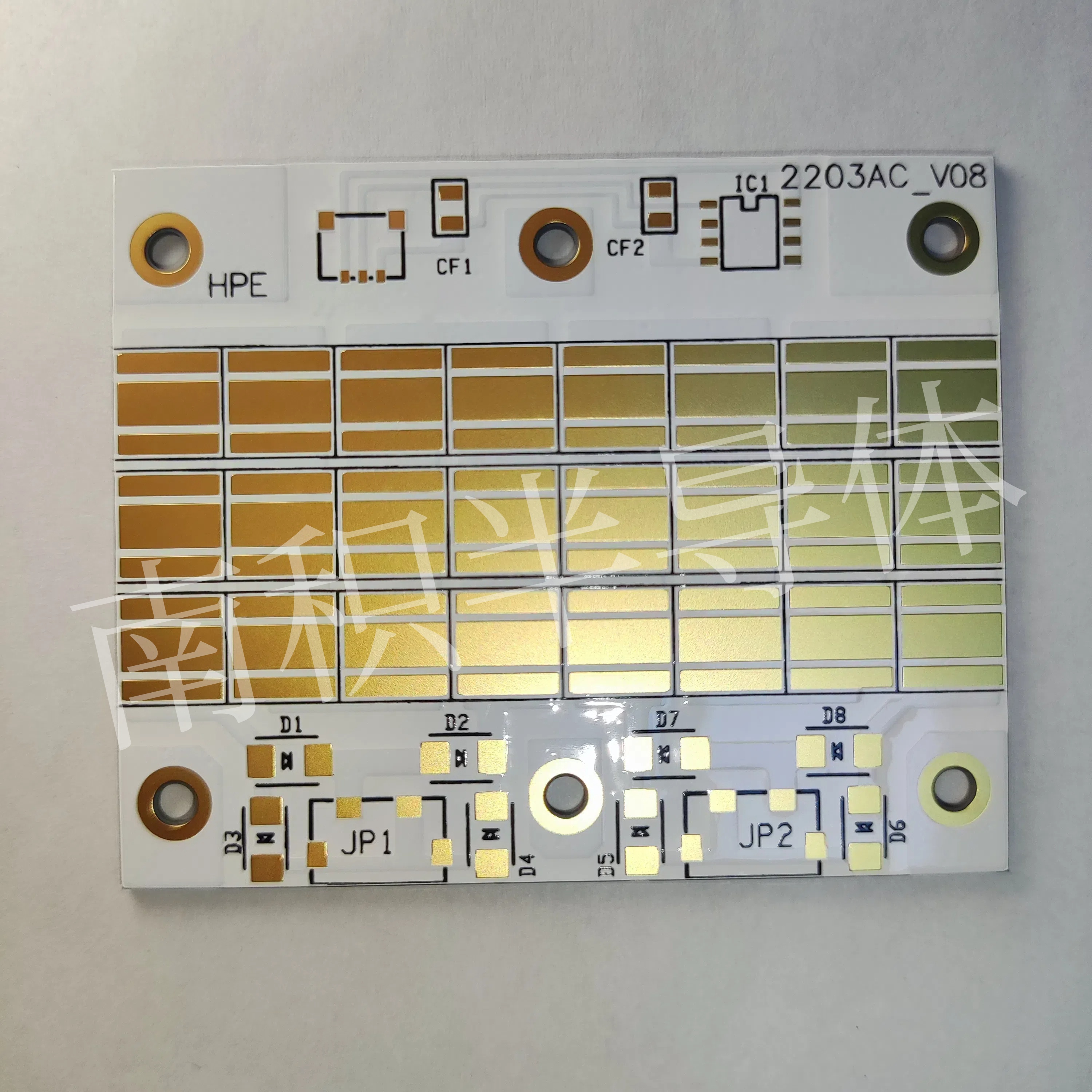

陶瓷基板五大工艺技术深度剖析:DPC、AMB、DBC、HTCC与LTCC的卓越表现

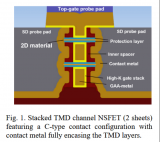

IEDM 2024先进工艺探讨(三):2D材料技术的进展及所遇挑战

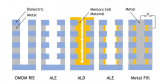

ALD和ALE核心工艺技术对比

Cadence Voltus-XFi可用于Samsung Foundry的先进 5LPE 工艺技术

Cadence Voltus-XFi可用于Samsung Foundry的先进 5LPE 工艺技术

评论