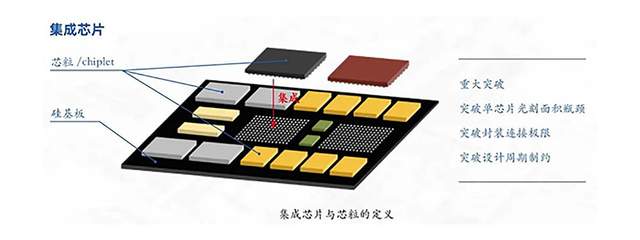

Chiplet 概述 过去几十年来,半导体行业一直按照摩尔定律的规律发展,凭借着芯片制造工艺的迭代,使得每18个月芯片性能提升一倍。但是当工艺演进到5nm,3nm节点,提升晶体管密度越来越难,同时由于集成度过高,功耗密度越来越大,供电和散热也面临着巨大的挑战。Chiplet(芯粒)技术是SoC集成发展到当今时代,摩尔定律逐渐放缓情况下,持续提高集成度和芯片算力的重要途径。工业界近期已经有多个基于Chiplet的产品面市,Intel甚至发布了集成47颗芯片的Ponte Vecchio系列,Chiplet技术已经是芯片厂商比较依赖的技术手段了。 相比传统Monolithic芯片技术,Chiplet技术背景下,可以将大型单片芯片划分为多个相同或者不同的小芯片,这些小芯片可以使用相同或者不同的工艺节点制造,再通过跨芯片互联和封装技术进行封装级别集成,降低成本的同时获得更高的集成度。通常来说,由于光刻掩膜版的尺寸限定在33mm * 26mm,单个芯片的面积一般不超过800mm^2,通过多个芯片的片间集成,可以在封装层面突破单芯片上限,进一步提高集成度。而且从工艺制造良率的Bose-Einstein模型:

其中A代表芯片面积,D0代表缺陷密度,n代表掩膜版层数相关系数。单芯片的面积越大,良率越低,对应制造成本也越高。同时,在当前主流芯片架构中,信号处理部分通常为数字逻辑,随着工艺演进相同功能情况下面积也会进一步缩小,但是各类接口部分通常为模拟电路,随着工艺演进相同功能情况下面积几乎不会缩小,因此合理地将不用功能有效划分到不同工艺节点的芯片上,可以更高效利用现有制造工艺,有效降低成本。 Chiplet技术带来上述高集成度和低成本等优势的同时,也面临着诸多技术挑战,总体来说可以概括为:物理上如何拼接多个芯片;设计上如何将大芯片划分为多个小芯片;以及如何标准化接口协议做到不同芯片产品标准化拼接。具体来说可以分为几个不同的方面:

超高速、超高密度和超低延时的封装技术,用来解决Chiplet之间远低于单芯片内部的布线密度、高速可靠的信号传输带宽和超低延时的信号交互。目前主流的封装技术包括但不限于MCM、CoWoS、EMIB等。

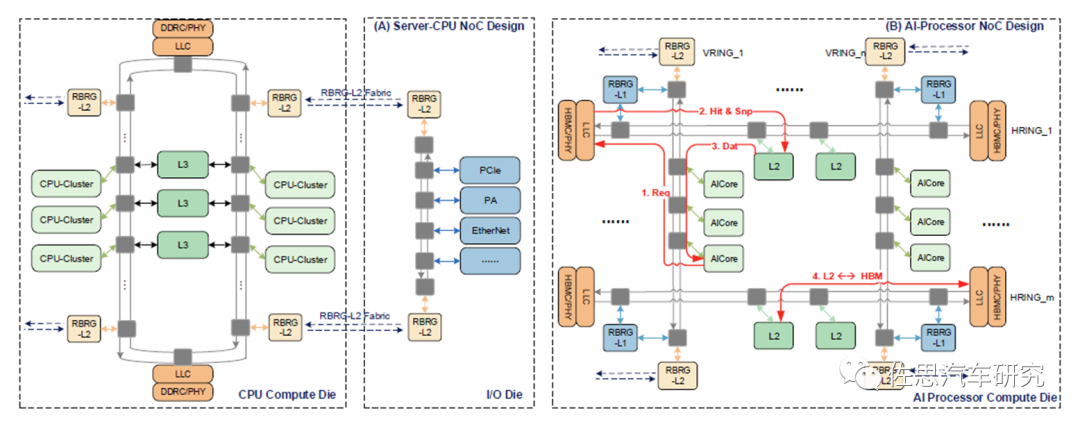

基于Chiplet的架构设计,一方面考虑不同Chiplets之间如何进行功能划分和架构定义,另一方面考虑多个Chiplets如何进行有效互联和扩展,实现高效灵活可扩展的架构,避免多Chiplets之间出现信号死锁、流量拥塞等功能和性能问题。

标准化的多Chiplets之间交互的通信互联协议,用于指导和约束不同芯片的接口设计和标准化对接。目前由Intel、AMD、ARM、ASE、Google、 Meta、Microsoft、Qualcomm、Samsung和TSMC共同开发和制定的UCIe(UniversalChiplet Interconnect Express)已经发布第一版标准。

由于篇幅限制,本文基于上述三个方面,简单介绍下当前业界主流实现方式,探讨不同解决方法的优缺点和设计考量,后续会附上各个部分的详细介绍。

支持Chiplet的底层封装技术 封装技术目前主要由TSMC、ASE、Intel等公司来主导,包含从2D MCM到2.5D CoWoS、EMIB和3D HybridBonding。本文主要介绍目前工业界主流的2D和2.5D封装技术和其优缺点。

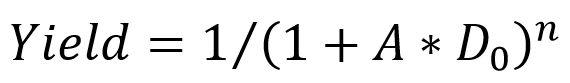

1. MCM(Multi-Chip Module)

Multi-chipModule

MCM一般是指通过Substrate(封装基板)走线将多个芯片互联的技术。通常来说走线的距离和范围可以在10mm~25mm,线距线宽大约10mm量级,单条走线带宽大约10Gbit/s量级。由于MCM可以通过基板直接连接各个芯片,通常封装的成本会相对较低,但是由于走线的线距线宽比较大,封装密度相对较低,接口速率相对较低,延时相对较大。

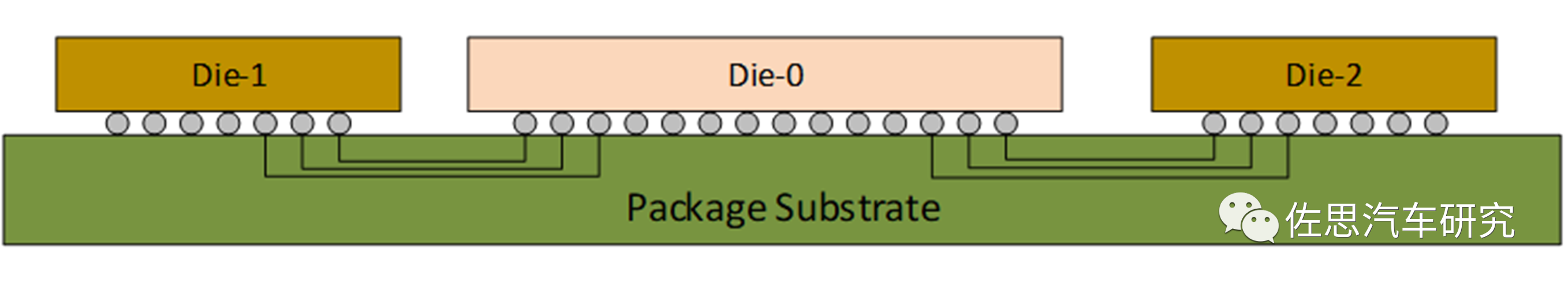

2. CoWoS(Chip-on-Wafer-on-Substrate)

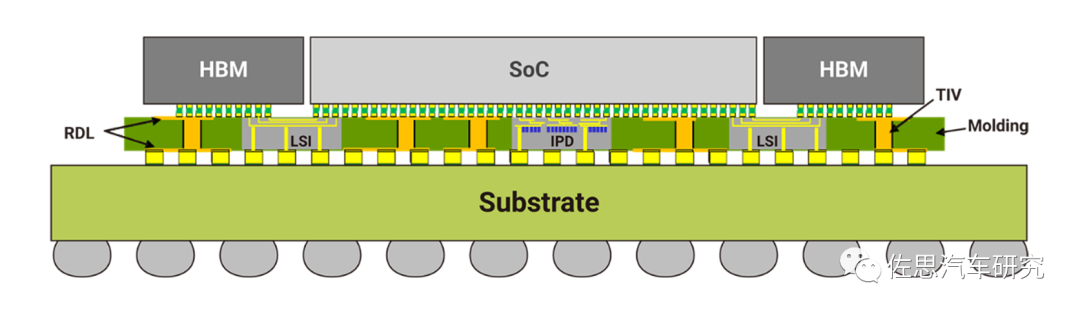

CoWoS是TSMC主导的,基于interposer(中间介质层)实现的2.5D封装技术,其中interposer采用成熟制程的芯片制造工艺,可以提供相比MCM更高密度和更大速率的接口。目前TSMC主流的CoWoS技术包括: CoWoS-S:基础CoWoS技术,可以支持超高集成密度,提供不超过两倍掩膜版尺寸的interposer层,通常用于集成HBM等高速高带宽内存芯片。

CoWoS

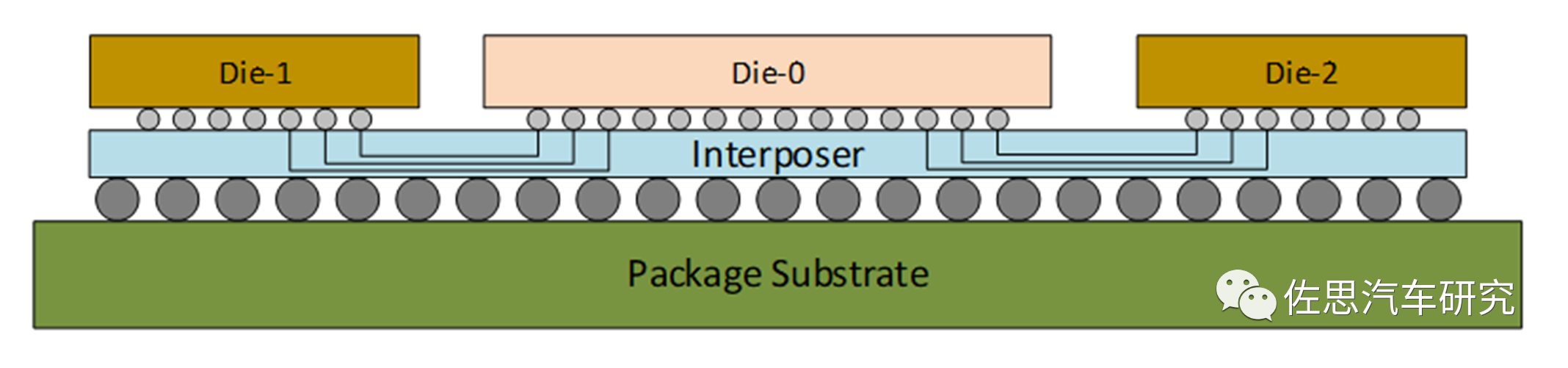

CoWoS-R:基于前述CoWoS-S技术,引入InFO技术中的RDL(RedistributionLayer),RDL 中介层由聚合物和铜迹线组成,具有相对机械柔韧性,而这种灵活性增强了封装连接的可靠性,并允许新封装可以扩大其尺寸以满足更复杂的功能需求,从而有效支持多个Chiplets之间进行高速可靠互联。

CoWoS-R

CoWoS-L:在上述CoWoS-S和InFO技术的基础上,引入LSI(LocalSilicon Interconnect)技术,LSI 芯片在每个产品中可以具有多种连接架构(例如 SoC 到 SoC、SoC 到小芯片、SoC 到 HBM 等),也可以重复用于多个产品,提供更灵活和可复用的多芯片互联架构。

CoWoS-L

相比于MCM,CoWoS技术可以提供更高的互联带宽和更低的互联延时,从而获得更高的性能。同时,受限于interposer的尺寸(通常为2倍掩膜版最大尺寸),可以提供的封装密度上限相对比较有限,并且由于interposer的引入,需要付出额外的制造成本和更高的技术复杂度,以及随之而来的整体良率的降低。

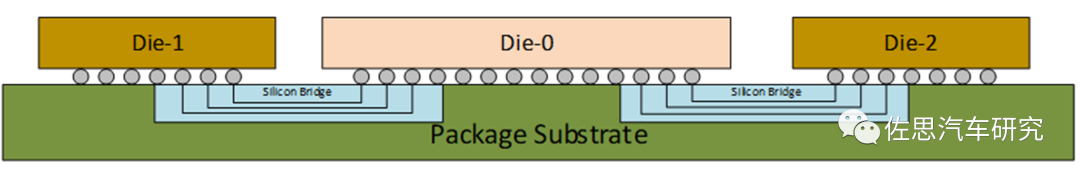

3. EMIB(Embedded Multi-die Interconnect Bridge)

EMIB

EMIB是Intel主导的2.5D封装技术,使用多个嵌入式包含多个路由层的桥接芯片,同时内嵌至封装基板,达到高效和高密度的封装。由于不再使用interposer作为中间介质,可以去掉原有连接至interposer所需要的TSVs,以及由于interposer尺寸所带来的封装尺寸的限制,可以获得更好的灵活性和更高的集成度。 总体而言,相比于前述介绍的MCM、CoWoS和InFO/LSI技术,EMIB技术要更为优雅和经济高效,获得更高的集成度和制造良率。但是EMIB需要封装工艺配合桥接芯片,技术门槛和复杂度较高。

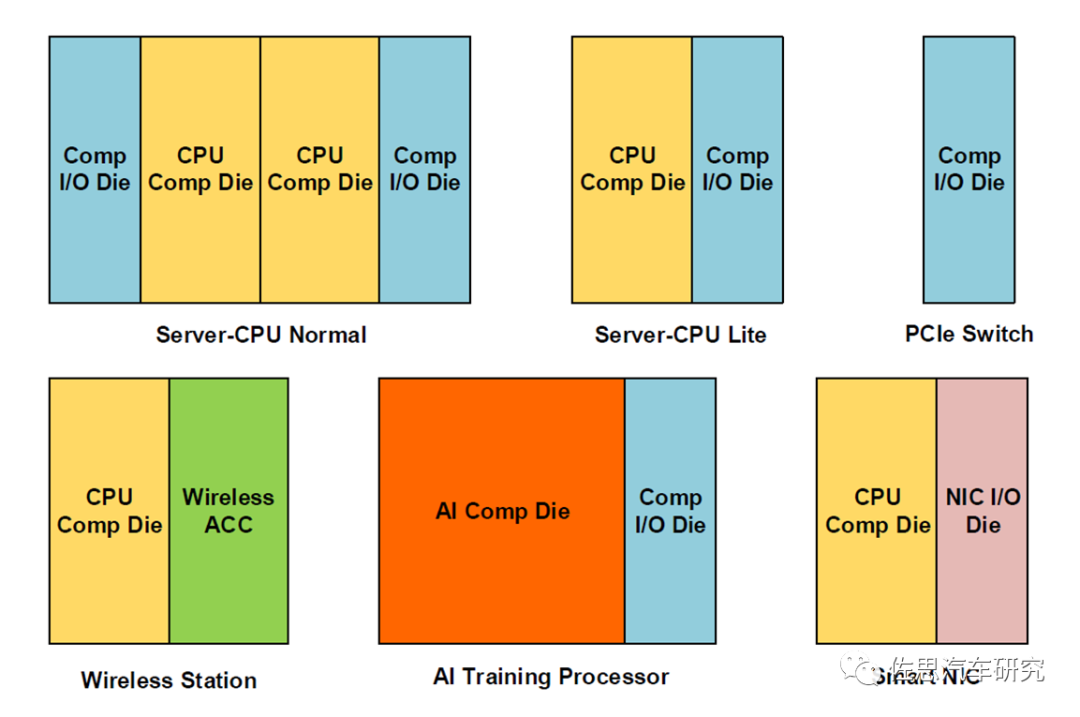

Chiplet架构挑战和洞察 基于Chiplet的架构设计,首先要考虑不同Chiplets之间如何进行功能划分和架构定义,目前主流的设计思路大致可以分为两类:

第一类

基于功能划分到多个Chiplets,单个Chiplet不包含完整功能集合,通过不同Chiplets组合封装实现不同类型的产品,典型代表为Huawei Lego架构(Kunpeng & Ascend)、AMD Zen2/3架构。

Huawei Lego架构:采用computedie(compute + memory interface)和I/O die组合的形式进行不同Chiplets功能拆解。在compute die(CPU/AI)设计时采用先进的工艺,获得顶级的算力和能效,在I/O die设计时采用成熟工艺,在面积与先进工艺差别不大的情况下获得成本收益。并且不同的Chiplets的数量和组合形式都可以灵活搭配,从而组合出多种不同规格的云端高性能处理器产品。

HuaweiLego

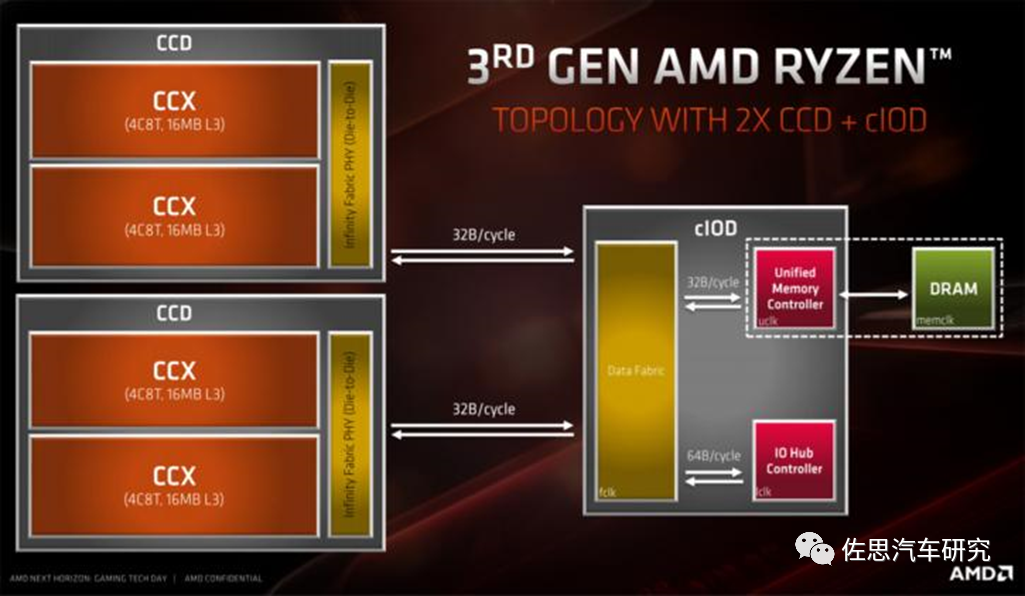

AMD Zen3架构:采用CCD(compute)和CIOD(memoryinterface + I/O)组合的形式进行不同Chiplets功能拆解。在CCD设计时采用最先进的工艺,获得顶级的算力和能效,在CIOD设计时采用成熟工艺,在面积与先进工艺差别不大的情况下获得成本收益。并且CCD本身按照两个4C8T cluster组合的形式设计,可以适应AMD从Desktop到Server的架构需求,根据场景选择CCD数量和设计对应的CIOD即可,灵活度非常高。

AMD Zen3

第二类

单个Chiplet包含较为独立完整的功能集合,通过多个Chiplets级联获得性能的线性增长,典型代表为Apple M1 Ultra、Intel Sapphire rapids系列。

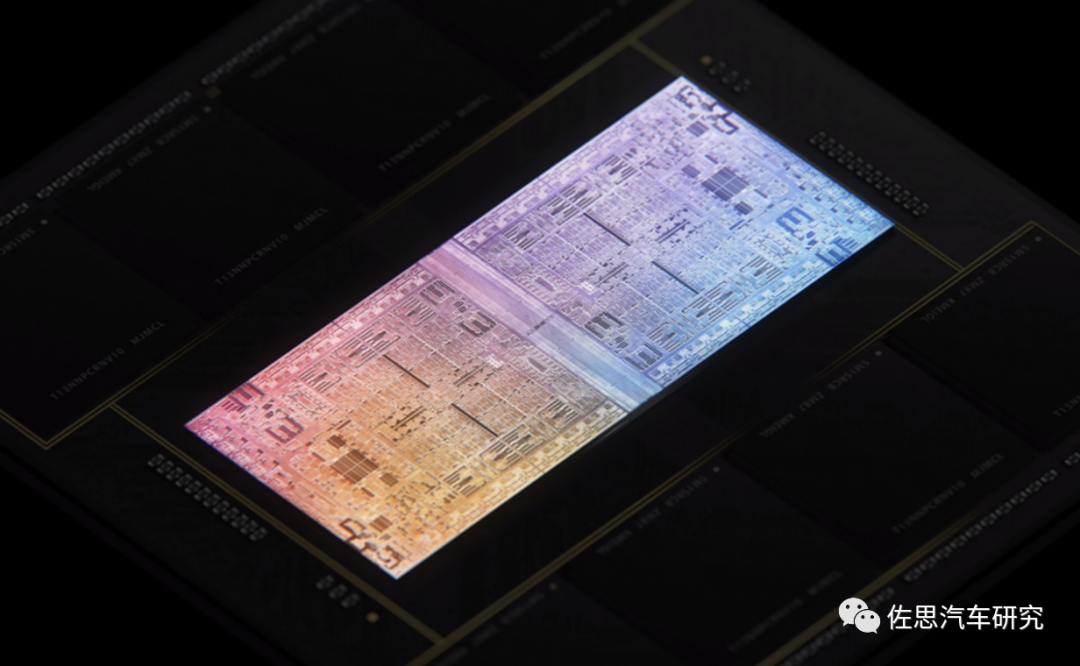

Apple M1 Ultra:通过Apple自研的封装技术UltraFusion来堆叠两颗M1 Max芯片,使得两颗芯片之间拥有超过2.5TB/s带宽且极低延时的互联能力。基于这个互联的延时带宽能力,可以使得M1 Ultra直接获得两倍M1 Max的算力,同时在软件层面依然可以将M1 Ultra当做一个完整芯片对待,而不会增加额外的软件修改和调试的负担。

AppleM1 Ultra

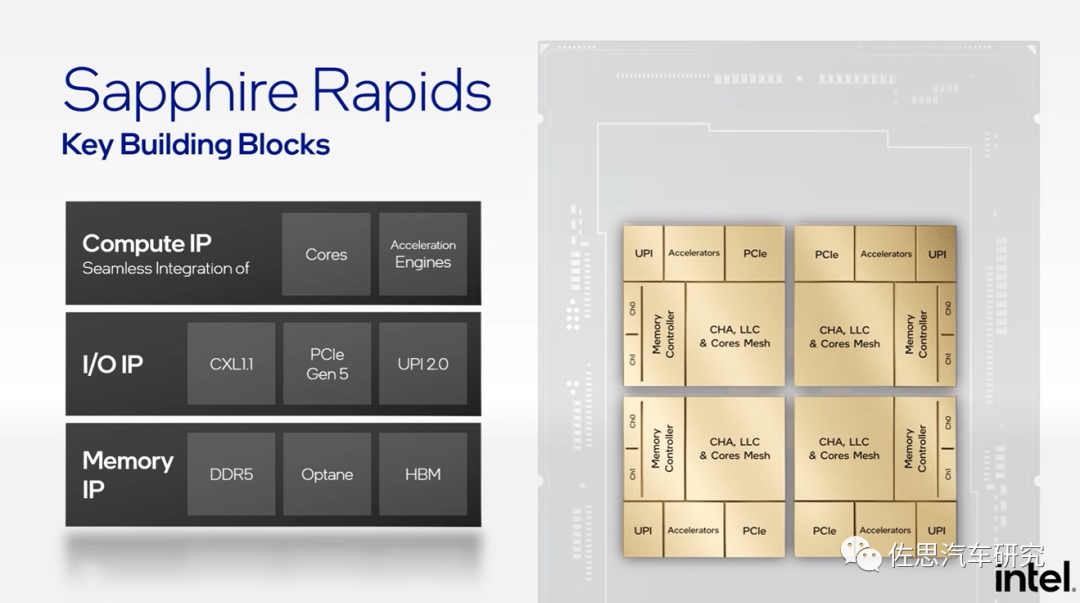

Intel Sapphire Rapids:通过两组镜像对称的相同架构的building blocks,组合4个Chiplets,获得4倍的性能和互联带宽。每个基本模块包含计算部分(CHA & LLC & Coresmesh, Accelerators)、memory interface部分(controller, Ch0/1)、I/O部分(UPI,PCIe)。通过将上述高性能组件组成基本的building block,再通过EMIB技术进行Chiplet互联,可以获得线性性能提升和成本收益。

IntelSapphire Rapids

基于Chiplet的架构设计,同时要考虑多个Chiplets如何进行有效互联和扩展,实现高效灵活可扩展的架构,避免多Chiplets之间出现信号死锁、流量拥塞等功能和性能问题。由于芯片内部互联通常为可靠连接假设下的并行数据传输,而芯片之间的互联通常为不可靠连接假设下的串行数据传输,根据芯片片上和片间互联架构的组合和流量收敛情况,目前主流的设计思路和应用场景大致分为两大类:

第一类

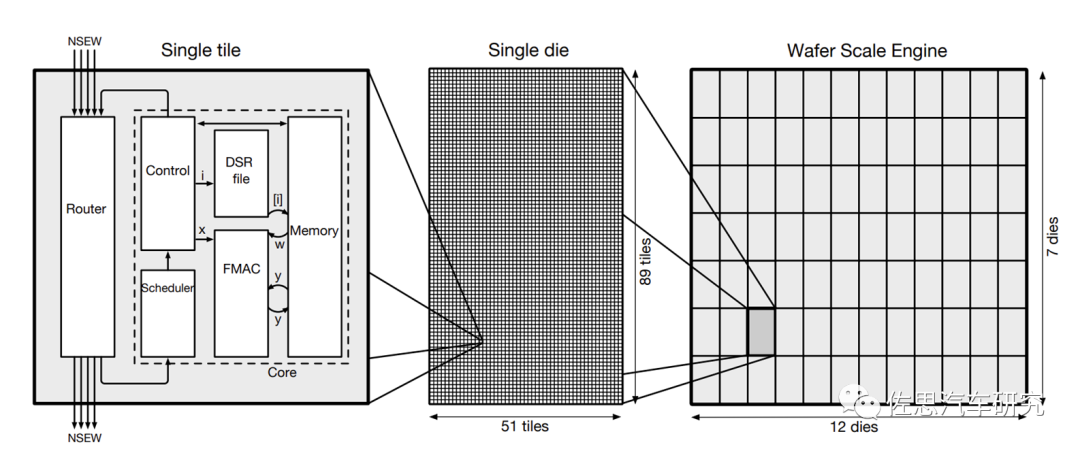

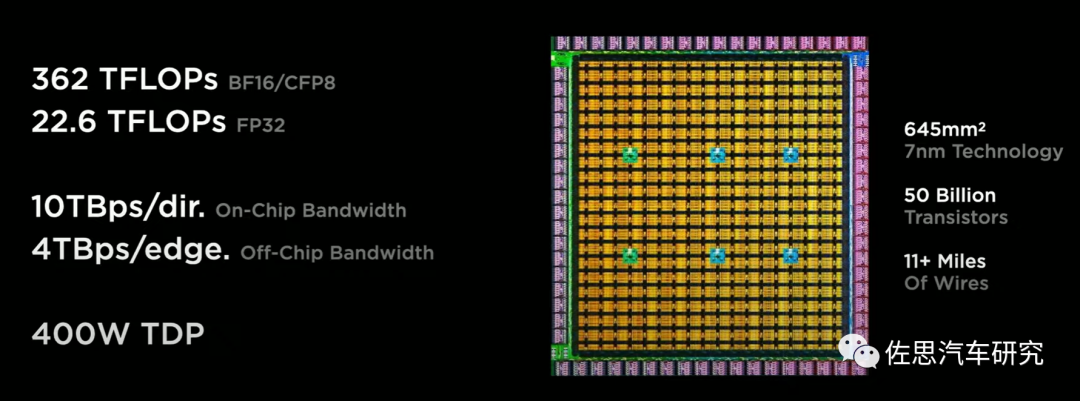

片上片间相同架构,流量全打平或基本打平。典型代表如Cerebras,采用从tile到singledie到wafer scale engine完全相同的互联架构。另一个典型代表是Tesla DoJo,采用InFO-SoW的封装和芯片四边全部放置I/O接口的方式实现片内每个方向10TBps带宽,跨片每边4TBps,SoW集成后单边带宽9TBps。

CS-1Wafer Scale Engine

DoJoD1 Chip

第二类

片上片间架构相似,片间流量按照一定比例收敛。典型代表一个是前述的Huawei Bufferless Multi-Ring架构,片上流量会收敛到分布式的各个跨片接口;另一个典型代表是前述的Apple M1 Ultra,片上流量收敛到UltraFusion集中交换部分。

BufferlessMulti-Ring

从计算负载的角度,当单个计算任务计算密度较高,超出单芯片算力范围的时候,需要多个芯片协同来完成,此时跨片数据交互也需要提供和片上数量级相当的带宽和延时,才能更有效利用算力,提高计算效率。典型的任务类型是AI的训练任务,前述Cerebras和DoJo的互联架构对这类场景有较强优势。当计算任务数量庞大,单个任务负载较小,跨片流量通常是要远小于片上流量的,此时采用流量收敛策略更为合适。 从互联架构的实现方式和实现策略角度,通常根据网络的拓扑、路由策略、防死锁机制等又可进一步细分,本文由于篇幅限制不再详细介绍。

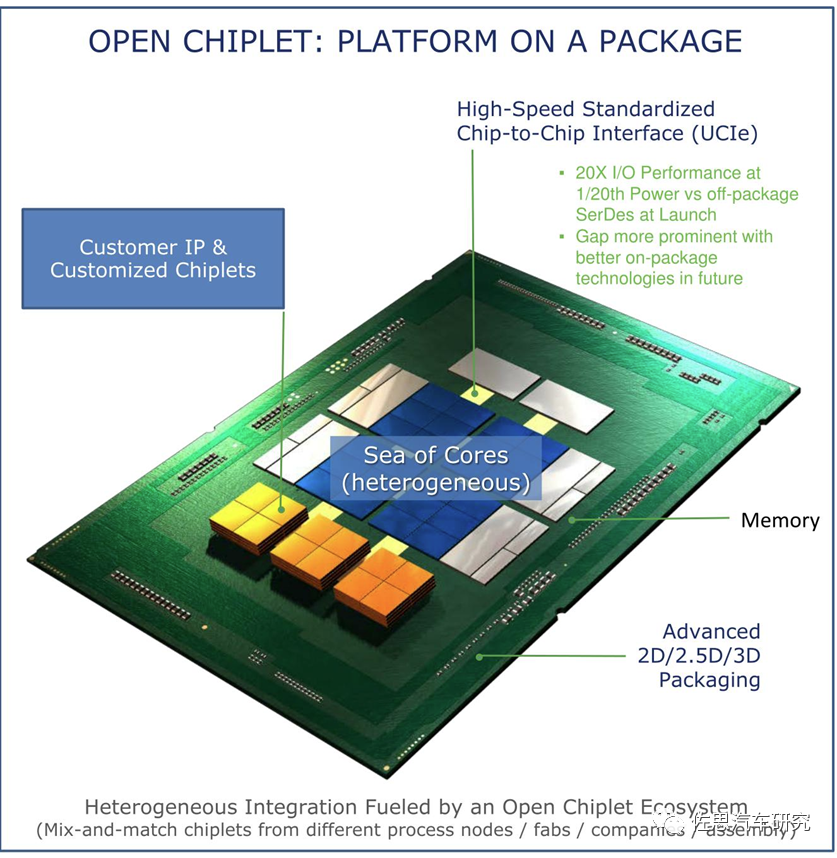

Chiplet协议介绍 工业界大约从2016年开始就在逐步尝试基于Chiplet的芯片设计,经过长时间的摸索,已经在封装工艺、架构设计上有了深厚的积累和长足的进步,在这样的背景和契机之下,由Intel、AMD、ARM、ASE、Google、 Meta、Microsoft、Qualcomm、Samsung和TSMC共同开发和制定的UCIe 1.0在2022年3月正式推出。 UCIe标准的初衷和目标,是建立一套Chiplet技术相关的设计和制造等各个环节的参考标准,从而使得不同设计和制造厂商的芯片可以无缝集成,从而打造封装层级的完整灵活的芯片开发生态系统。基于Chiplet技术和UCIe标准,可以实现超过单个掩膜版尺寸的芯片面积,获得更大尺寸、更高集成度的高性能芯片。同时基于标准的UCIe,可以使能各类不同工艺和不同大小的芯片和IP在封装层面进行集成,有效降低开发成本,同时减少开发周期。

Figure.Initial motivation of UCIe

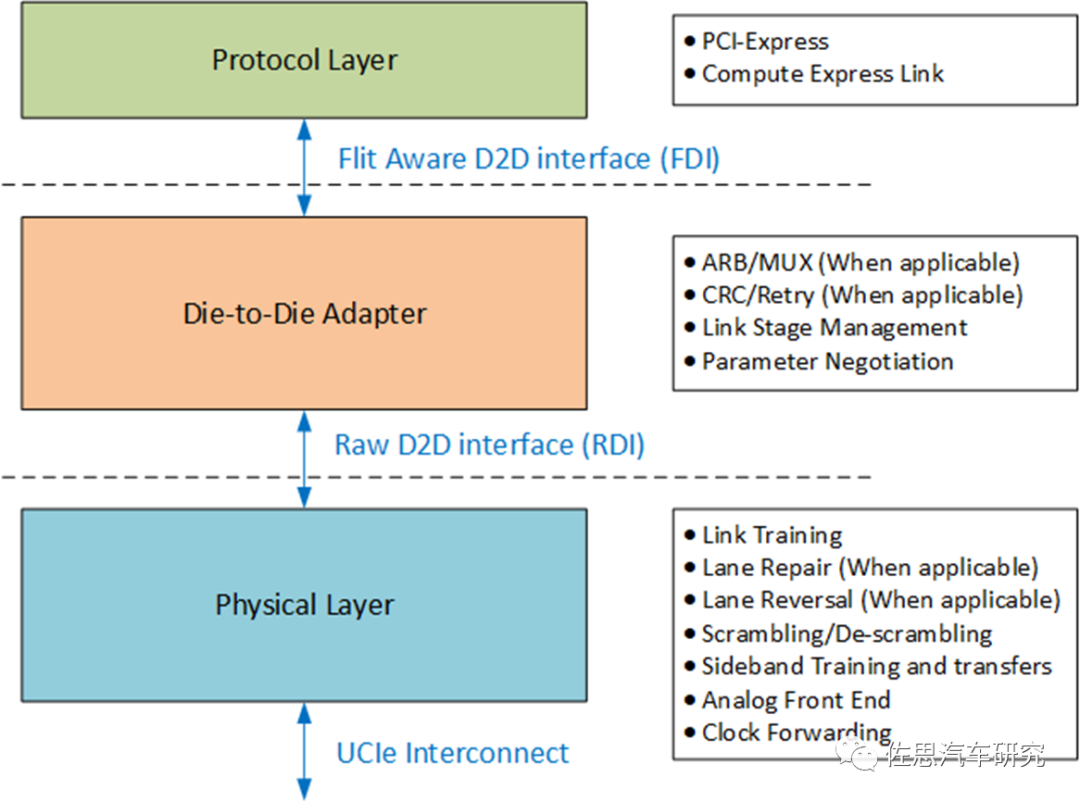

UCIe主要规定的规格和标准包含以下几个层面(具体内容本文不再赘述):

协议层:定义了高层级通信协议标准,初始版本采用成熟的PCIe加CXL协议。

中间层:定义了Chiplets之间的适配标准,包括Link状态管理,参数对齐,信号的选择校验,以及可能的重传机制。

物理层:定义了电气信号连接的标准、物理链路设计标准,包括电气信号定义,时钟定义,Link和Sideband训练。

Figure.Layering with UCIe

总结 综上所述,经过数年的发展,Chiplet技术已经逐渐走向成熟和商用,成为芯片厂商比较依赖的技术手段,也被认为是未来芯片行业发展的重要方向。目前在底层封装层面,已经有TSMC、Intel等厂商提供CoWOS、EMIB等先进封装,可以提供超高速、超高密度和超低延时的Chiplet互联;在标准协议层面,也有众多大厂领衔发布的UCIe 1.0版本,提供了跨片接口设计的指导和约束。而在架构设计层面,如何基于Chiplet设计高性能、高效率、灵活可扩展的互联架构,如何基于实现和商业视角进行芯片间的功能划分仍然是Chiplet技术中最大的挑战。

Reference:

https://3dfabric.tsmc.com/english/dedicatedFoundry/technology/3DFabric.htm

https://ase.aseglobal.com/public/en/technology/focos.html

https://www.intel.com/content/www/us/en/silicon-innovations/6-pillars/emib.html

S. Naffziger, K. Lepak, M. Paraschou, and M. Subramony, “2.2 amd chiplet architecture for high-performance server and desktop products,” in 2020 IEEE International Solid-State Circuits Conference-(ISSCC). IEEE, 2020, pp. 44–45

A. Biswas, “Sapphire rapids,” in 2021 IEEE Hot Chips 33 Symposium (HCS). IEEE Computer Society, 2021, pp. 1–22.

T. Wang, F. Feng, S. Xiang, Q. Li and J. Xia, "Application Defined On-chip Networks for Heterogeneous Chiplets: An Implementation Perspective," 2022 IEEE International Symposium on High-Performance Computer Architecture (HPCA), 2022, pp. 1198-1210, doi: 10.1109/HPCA53966.2022.00091.

https://www.apple.com/tn/newsroom/2022/03/apple-unveils-m1-ultra-the-worlds-most-powerful-chip-for-a-personal-computer/

Rocki, Kamil, et al. "Fast stencil-code computation on a wafer-scale processor." SC20: International Conference for High Performance Computing, Networking, Storage and Analysis. IEEE, 2020.

https://www.youtube.com/watch?v=j0z4FweCy4M

Parasar, Mayank, et al. "Swap: Synchronized weaving of adjacent packets for network deadlock resolution." Proceedings of the 52nd Annual IEEE/ACM International Symposium on Microarchitecture. 2019.

Yin, Jieming, et al. "Modular routing design for chiplet-based systems." 2018 ACM/IEEE 45th Annual International Symposium on Computer Architecture (ISCA). IEEE, 2018.

https://www.uciexpress.org/specification

Xia, Jing, et al. "Kunpeng 920: The first 7-nm chiplet-based 64-Core ARM SoC for cloud services." IEEE Micro 41.5 (2021): 67-75.

https://www.anandtech.com/Gallery/Album/8123#3

审核编辑 :李倩

-

半导体

+关注

关注

336文章

29977浏览量

258180 -

摩尔定律

+关注

关注

4文章

640浏览量

80611 -

封装技术

+关注

关注

12文章

595浏览量

69153 -

chiplet

+关注

关注

6文章

482浏览量

13503

原文标题:Chiplet:大算力的翅膀

文章出处:【微信号:zuosiqiche,微信公众号:佐思汽车研究】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Chiplet核心挑战破解之道:瑞沃微先进封装技术新思路

Chiplet封装设计中的信号与电源完整性挑战

解构Chiplet,区分炒作与现实

Chiplet与先进封装全生态首秀即将登场!汇聚产业链核心力量共探生态协同新路径!

Chiplet与3D封装技术:后摩尔时代的芯片革命与屹立芯创的良率保障

从技术封锁到自主创新:Chiplet封装的破局之路

Chiplet:芯片良率与可靠性的新保障!

支持Chiplet的底层封装技术

支持Chiplet的底层封装技术

评论