DDR 接口在时钟信号的上升沿和下降沿传输数据。该技术已被用作 DDR 同步动态随机存取存储器 (SDRAM)、微处理器前端总线、Ultra3 小型计算机系统接口 (SCSI) 和加速图形端口总线的通信链路。在每个周期中,数据在时钟的上升沿和下降沿进行采样,最大数据频率通常是时钟频率的两倍。

DDR 技术的趋势是朝着更高的数据速率和更低的电压水平发展。为了使系统准确运行,必须优化其信号完整性性能并满足某些最低要求。尽管 DDR2/DDR3 接口不如串行链路接口快,但信号完整性问题明显更具挑战性,DDR4 将成为更大的问题。这是由于这些接口的并行与串行性质。串扰和电源噪声等信号完整性问题在并行接口中占主导地位,并且随着数据速率的提高而逐渐恶化。

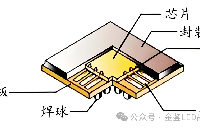

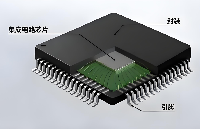

随着行业转向 DDR3 和更高的数据速率,可以可靠地对数据进行采样的数据有效窗口或单位间隔 (UI) 稳步缩小,并且对信号完整性问题的敏感性急剧增加。在这些高数据速率下,封装成为一个重要的考虑因素,尤其是在芯片互连方法方面。当前的 IDT DDR3 封装配置为引线键合芯片。以下讨论将重点介绍将 DDR3 裸片更改为倒装芯片类型的好处,并展示由此产生的性能优势。

DDR 接口挑战

第一代 DDR 接口旨在以 400 Mtps 的最大数据速率发送和接收数据,相应的位周期或 UI 为 2.5 ns。这些接口通常使用 2.5 V 电源。当前的 DDR3 接口运行速度为 1,600 Mtps,而基于 DDR4 的系统预计运行速度为 3,200 Mtps。在该数据速率下,每个 UI 仅约 312.5 ps,电源电压降至 1.2 V。

DDR 技术的这种演变为物理互连设计带来了几个挑战:

缩短位周期:更短的位周期导致更短的建立和保持时间帧,使得时钟和数据信号之间的时序难以满足。

快速信号边沿:为了适应不断缩小的位周期,信号边沿越来越尖锐,加剧了串扰和电源噪声性能问题。

较低的电压电平:对于 2.5 V 电源,5% 的噪声容限导致芯片电源和接地节点的最大可接受噪声电平为 125 mV。对于 1.2 V 电源,同样 5% 的噪声容限在相同的电源和接地节点上转换为仅 60 mV 的可接受噪声。互连设计和选择成为满足这些严格噪声容限的关键组件。

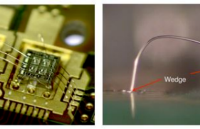

封装是整个系统互连的关键组成部分,不理想的封装互连选择会显着降低器件性能。当前的 IDT DDR3 器件使用引线键合将芯片连接到封装基板。引线键合的 3D 特性使得控制由攻击信号发出的电磁场极其难以管理。一般来说,引线键合本质上是电感性的,两条相邻导线之间的互感是信号间串扰的主要贡献者。感应焊线还会导致电源阻抗增加,从而导致芯片上的电源噪声增加。

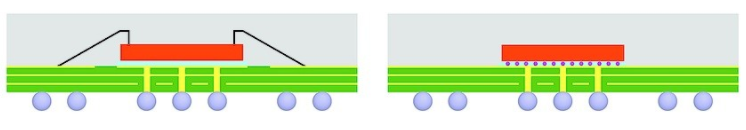

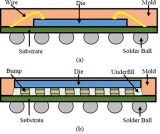

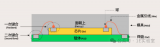

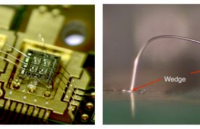

移除这些引线键合并将芯片到封装互连转换为倒装芯片将消除信号完整性问题的一个关键来源,而不会影响整体封装形状因数。图 1 显示了两种芯片到封装互连类型的横截面,所有其他特性都相同。

图 1:两种类型的芯片到封装互连包括引线键合(左)和倒装芯片(右)。

了解串扰

串扰是由于电磁信号能量通过互电容(电场耦合)和互感(磁场耦合)从一个导体泄漏到另一个导体而引起的。

电容串扰

在受害者-入侵者情况下,电容串扰将电流从入侵者线路注入到受害者线路上,串扰幅度与电压变化率和两条线路之间的互电容量成正比。注入的能量将分裂并流向受害线路的两端——两端是近端(靠近驱动器侧)和远端(靠近接收器侧)。

感应串扰

由于互感耦合引起的串扰会在受扰线上感应出电压,该电压与驱动线上的电流变化率和两个导体之间的互感大小成正比。由感应电压引起的电流从远端流向近端(根据楞次定律),与驱动线的方向相反。

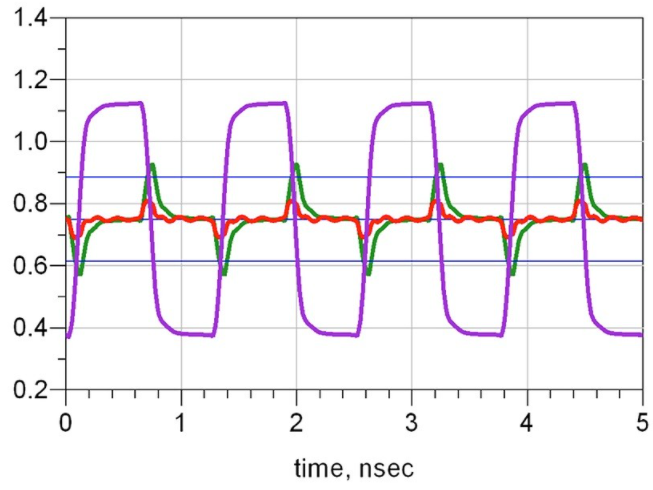

在基于基板的封装中,串扰可分为封装互连的传输线部分的串扰和封装互连的 3D 结构中的串扰,例如通孔、引线键合和焊球。在封装结构的传输线部分,串扰主要是电磁的,而在 3D 部分则主要是感应的。对于大多数封装应用,远端串扰几乎总是负面的,将来自封装 3D 部分的感应串扰确定为主要的串扰机制。由于消除了引线键合(互感降低),封装的倒装芯片版本显示的远端串扰比引线键合版本少得多,如图 2 所示。

图 2:倒装芯片封装(红线)在干扰线切换时在受扰线上产生的串扰比引线键合封装(绿线)要小。

对模态延迟的串扰效应

信号通过导体的飞行时间取决于相邻耦合导体的切换方式。随着导体之间的串扰增加,这种飞行时间的差异会加剧。在多导体系统中,有三种可能的开关模式:静音模式、奇数模式和偶数模式:

静默模式:如果受扰信号的上升和下降时间与相邻耦合的干扰信号不一致,或者受扰信号保持静默,这种切换模式称为静默模式。

奇模式:如果相邻耦合干扰源的上升和下降时间与受扰信号一致,并且如果干扰源与切换信号异相 180° 切换,则这种切换模式称为奇模式。

偶数模式:当相邻入侵者的开关与受害信号同相且同时,这种切换模式称为偶数模式。

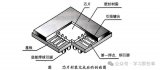

在耦合系统中,经历奇模式切换的信号总是最早到达接收器,其次是处于安静模式的信号,最后是经历偶模式的信号。随着串扰的增加,I/O 组中的切换信号之间的信号飞行时间扩展也会增加。在使用公共时钟对多个并行信号位进行采样的 DDR 类型系统中,这种由串扰引起的偏移的扩展会对可用于正确时钟的建立和保持时间窗口产生不利影响。并且随着数据速率随着 UI 中的相关缩小而增加,减少串扰以改善建立/保持时间窗口将变得至关重要。

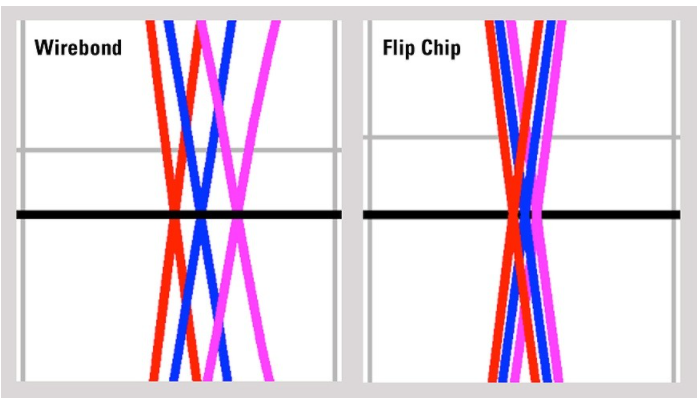

图 3 比较了两种封装类型的模态延迟扩展。引线键合延迟更加分散,总模态延迟扩展为 41 ps,而倒装芯片变化仅为 15 ps。由于 DDR4 应用程序的 UI 预计将是 DDR3 的一半,引线键合封装的封装偏差增加将使时序难以满足,因此倒装芯片将成为首选的互连选项。

图 3:在模态延迟扩展的比较中,引线键合封装比倒装芯片封装显示出更大的延迟扩展,红色为奇数模式,蓝色为安静模式,粉红色为偶数模式。

向芯片供电

有效地向芯片供电需要降低从芯片电源和接地节点向外看的供电网络的输入阻抗。封装类型和芯片到封装基板互连技术是整个系统供电网络的关键组成部分。封装阻抗很大程度上取决于由电源和接地互连形成的环路面积以及所使用的芯片到封装互连方法的类型。从该环路中消除引线键合可降低环路电感,从而将阻抗降低 50% 以上,从而降低芯片上的电源噪声。降噪幅度将是最佳 DDR4 接口性能的要求。

由于采用 DDR4 将需要更严格的噪声和时序预算,倒装芯片将成为芯片到封装互连的首选技术。在这些高数据速率下,固有的电感性引线键合会影响串扰、时序和电源噪声性能。通过提供优于引线键合互连的关键优势,倒装芯片显着提高了 DDR 接口的重要性能指标。

审核编辑:郭婷

-

电源

+关注

关注

185文章

18709浏览量

261386 -

芯片

+关注

关注

462文章

53534浏览量

459085 -

DDR

+关注

关注

11文章

747浏览量

68528

发布评论请先 登录

实现“贴身”测温!日本立山科学TWT系列引线键合NTC技术详解

铜线键合IMC生长分析

引线键合检测的基础知识

倒装芯片的优势_倒装芯片的封装形式

通过从引线键合切换到倒装芯片来提高DDR性能

通过从引线键合切换到倒装芯片来提高DDR性能

评论