业界正在接受嵌入式现场可编程门阵列 (eFPGA),因为该技术已在多个流行工艺节点的硅片中可用并得到验证。eFPGA 正在以多种方式集成到芯片中,包括作为可重新配置的 I/O 处理器或加速器,在数据路径或控制路径中。这种方法的好处是它通过不将加速器绑定到固定功能来提供灵活性。

为此,芯片设计人员可以创建从 eFPGA 到 ARM 架构的高级外围总线 (APB)、AMBA 高性能总线 (AHB) 和 AMBA 高级可扩展接口 (AXI) 总线的连接,从最简单的接口到APB 从机到最复杂的 AXI 主机。

随着网络、深度学习和人工智能 (AI) 以及航空航天和国防等应用对硬件加速的需求不断增长,对片上系统 (SoC) 和微控制器 (MCU) 设计的需求也在不断发展。如今,常见的 SoC 具有集成数字信号处理 (DSP) 和 FPGA IP 块,专用于特定 I/O 或处理工作负载,而主 CPU 内核处理通用任务。这些架构支持更高效、更灵活的整体处理解决方案。

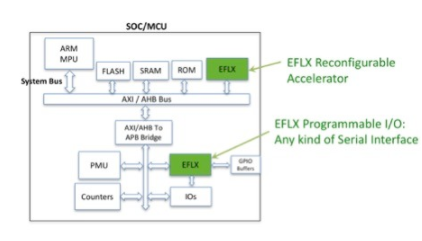

尤其是 eFPGA,由于上述原因,最近越来越受欢迎。与传统的 DSP 和 FPGA 不同,eFPGA 可以作为可重新配置的 IP 块设计到芯片中,可以重新编程以处理不同的工作负载加速任务或在芯片组的整个生命周期内管理不同的 I/O(图 1)。

图 1. Flex Logix 的 EFLX eFPGA IP 可以在 MCU 和 SoC 设计中实现为可重新配置的硬件加速块或可重新编程的 I/O 块。]

例如,对于使用 ARM 架构的芯片设计人员,eFPGA 可以连接到 APB、AHB 或 AXI 处理器总线以利用这些优势。但是,考虑到多种组合(主/从 x AXI/AHB/APB x 外部接口逻辑或使用 eFPGA 实现),应仔细考虑这些设计。

eFPGA I/O 资源

为了更好地了解如何使用标准接口将 eFPGA 设计成基于 ARM 的 MCU 或 SoC,我们将以 Flex Logix EFLX-2.5K 嵌入式 FPGA IP 内核为例。

EFLX-2.5K eFPGA 是一个 1x1 阵列,由 2,520 个具有 632 个输入和 632 个输出的六输入查找表 (LUT) 组成。它在 16 nm 工艺中的工作频率约为 1 GHz,在 28 nm 工艺中优于 500 MHz。因此,即使是最小的 eFPGA 也具有足以连接到最宽、最快的 ARM 总线的 I/O 资源和速度。

(注意:最大 7x7 的更大数组是可能的,每个增加的数组大小的 I/O 数量计算为 NxM 数组中的 N*632 输入和 N*632 输出。增加数组大小的 LUT 数量类似计算为 N*M*2520。)

eFPGA 作为 APB 从机

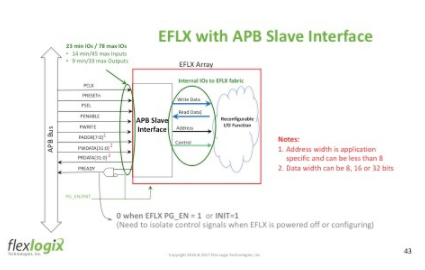

配置为 APB 从机的 eFPGA 通常会实现为可重新配置的 I/O 功能。例如,多种串行接口中的一种可以包括 UART、I2C 和 SPI。

在这种配置中,多个模块连接到 APB 总线,该总线一次在一个模块上运行(图 2)。每个块都有内存映射的地址空间(例如 128 个寄存器的 8 位),而总线上的数据可以是 8、16 或 32 位。8 位地址空间和 32 位数据需要 45 个输入和 33 个输出,而 16 位总线使用更少的 16 个输入和 16 个输出。

图 2.配置为 APB 从机的 eFPGA 通常实现为包含多个存储器映射块的可配置 I/O 功能。APB 总线在每一个上同步运行。

APB 从接口快速、简单,可以在外部实现,也可以在 eFPGA 的逻辑中实现。例如,在此配置中,EFLX eFPGA 需要少于 10 个 LUT。如图 3 所示,APB 从接口 Verilog 代码和状态图也很简短。

图 3.当 eFPGA 配置为 APB 从接口时,Verilog 代码和状态图很简单。

eFPGA 作为 AXI 主机

AXI 总线由三个版本组成:AXI4、AXI4 Stream 和 AXI4 Lite。

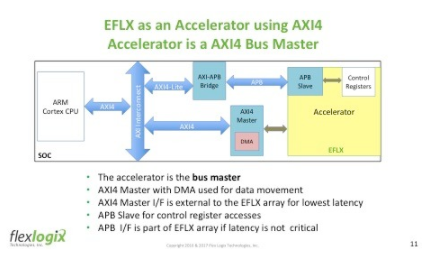

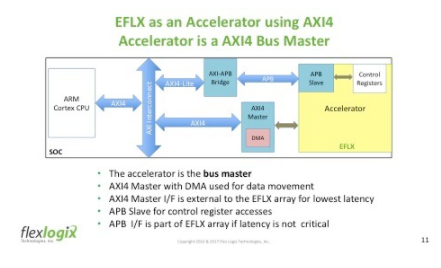

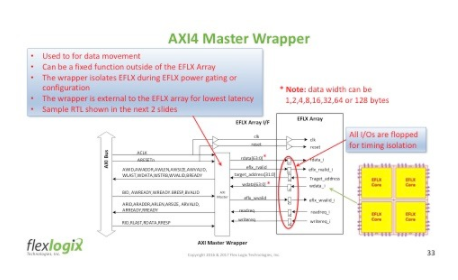

图 4 显示了具有在 eFPGA 外部实现的包装器的 AXI4 主设备。AXI 主包装器的功能是处理所有总线协议,管理数据流控制,并在配置期间将 EFLX FPGA 与 AXI 总线隔离。

在这里,EFLX Reconfigurable Accelerator 充当总线主控器,因此 CPU 不需要向内存传输数据和从内存传输数据。这可以将 CPU 卸载到可以与 EFLX 加速器并行运行的其他任务上。

图 4.配置为 AXI 主设备的 EFLX 可重配置加速器可以减轻 CPU 的总线管理任务负担。

EFLX eFPGA 能够支持窄或非常宽(128 字节)的 AXI 数据宽度,具体取决于加速器功能所需的带宽。EFLX 阵列中的控制寄存器和 APB 从属逻辑在 EFLX 阵列中实现并通过 APB 总线进行控制。图 2 所示的 APB 从接口示例可以实现控制寄存器接口。

图 5 显示了 AXI 总线架构的高级图,说明了主从连接。在将 eFPGA 实现为 AXI 主设备时,应始终翻转 eFPGA 以简化关闭、定时、输入和输出到/输出。数据总线宽度可以是 1、2 或 4 字节等,最多 128 字节。

图 5.为了简化 AXI 总线中的主从连接,建议对 eFPGA 进行翻转。

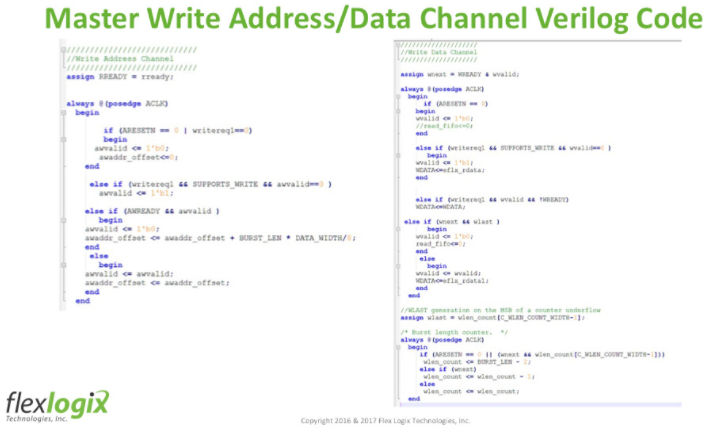

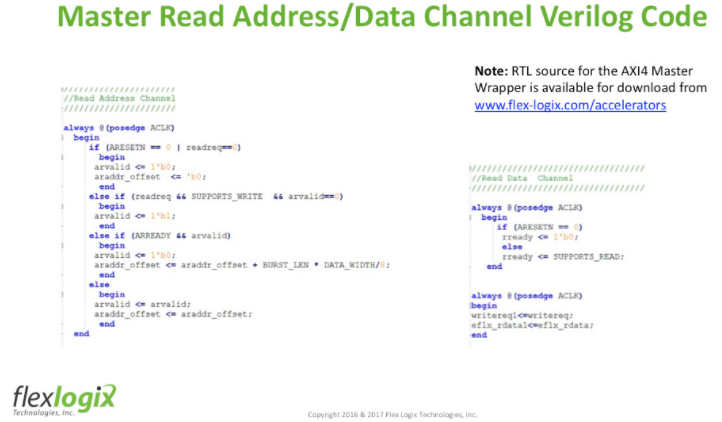

即使对于复杂的总线主控,Verilog 代码也相对简单(图 6)。

图 6.使用 eFPGA 作为 AXI 总线主控器时,Verliog 代码仍然相对简单。

eFPGA 通过单独的从接口

除了作为加速器或 I/O 处理器的阵列操作的总线连接之外,EFLX 等 eFPGA 还提供了一个单独的从接口,用于加载配置位以根据需要进行重新配置。外部 AXI 从包装器也可用于与配置端口连接。

例如,使用 EFLX,配置位通常存储在与 ARM 处理器代码相同的闪存中。处理器启动后,它使用直接存储器访问 (DMA) 通过配置从接口将配置位访问到 eFPGA。

结论

随着现代处理解决方案对灵活性和性能的需求日益增长,eFPGA 可以使用少量高速逻辑轻松连接到任何类型和宽度的 ARM 总线。经过多年的复杂性和成本挑战,基于 eFPGA 技术的可重构加速器和 I/O 处理器已成为任何基于 ARM 的 SoC 或 ASIC 架构师的易于使用的资源。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

20150浏览量

247270 -

asic

+关注

关注

34文章

1269浏览量

124064 -

寄存器

+关注

关注

31文章

5590浏览量

129089

发布评论请先 登录

什么是嵌入式操作系统?

ARM嵌入式这样学

嵌入式与FPGA的区别

嵌入式需要掌握哪些核心技能?

嵌入式软件测试与专业测试工具的必要性深度解析

入行嵌入式应该怎么准备?

中科亿海微SoM模组——嵌入式工业现场总线通信控制板

AMD EPYC嵌入式9005系列处理器的功能特性

嵌入式FPGA与ARM总线连接支持整体处理解决方案

嵌入式FPGA与ARM总线连接支持整体处理解决方案

评论