1

指令集

建设一栋大楼的基本元素有:水泥、砖头、钢材等原材料,但不同的构造过程则会呈现不同的建筑形式,其中建造图纸起到了很大的指导作用。

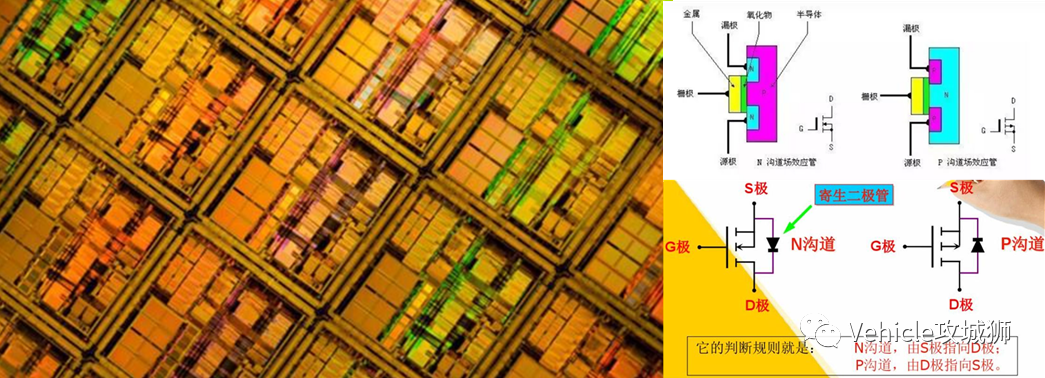

同样, CPU从表象上看虽然形式很多,但基本电路都由晶体管构成,例如常见的MOS管。

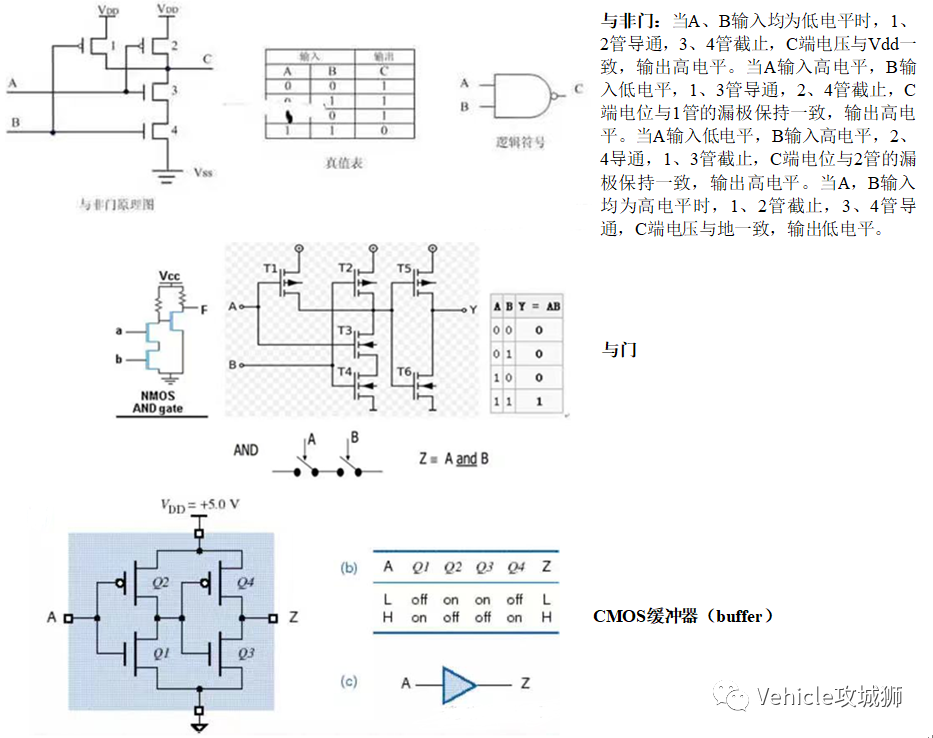

通过晶体管等基本电子元器件的组合可构成基本的逻辑电路:如与门、非门、与非门等。

这些基本逻辑电路通过不同的逻辑组合可分别完成不同的功能,就好比“把大象放进冰箱的段子”,首先打开冰箱门-->然后把大象放进去-->最后关上冰箱门。通过这些逻辑组合使动作具有了意义,而这些实现特定功能的逻辑组合集合就是指令集,如基本的加减运算。 指令集是一个标准,其会随着需求变化不断添加新的指令或优化。同样,指令集发生变更后,工程师在设计CPU时也需要在硬件电路上增加对应的电路模块来支持变更的指令,配套的编译器也会随之升级。我们在玩51、STM32等单片机时需要相应的编译器来实现相应程序开发就是这个道理。而在任何一款遵循同一指令集架构实现的处理器上,开发的应用无须做任何修改便可以运行。

2

指令集与机器码的桥梁-编译器

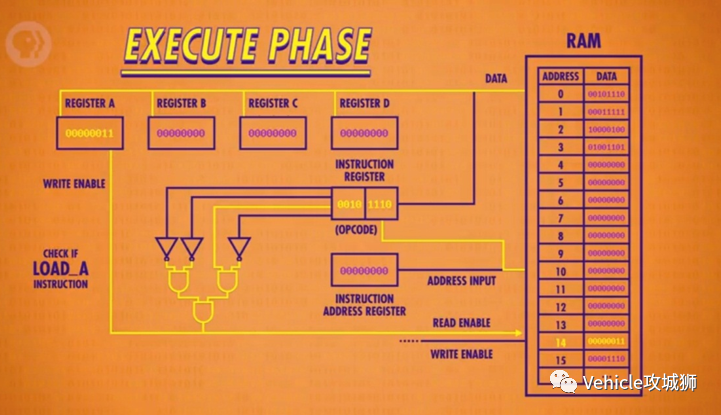

无论处于上层的应用程序多么酷炫吊炸天,其在处理器上执行就必须被翻译成“机器语言”,然后通过0或1的排列组合去操作硬件实现功能。翻译官这个角色就是编译器的活,它将软件与硬件世界连接了起来。编译器在这个过程中,要经过编译、汇编、链接等几个步骤, 最后生成"可执行文件",可执行文件中保存的是二进制机器码,这串机器码可以直接被CPU读取和执行。

上图表示在指令寄存器中正在执行的一段为00101110机器码,左四位0010为指令集LOAD_A(汇编代码,将数据放到寄存器A),右四位1110(RAM地址,就是要去取这个地址上的8bit 机器码数据放到寄存器A)。注意到0010这4bit数据先被放入一个门电路中,输出结果就是1bit(拉高电压),去控制内存读取这一条wire。这个图只突出显示了开启内存读取一条wire的原理,没有显示在这一步指令中所有门电路原理图。

3

为啥根据指令集设计CPU而不是

先设计CPU再指令集

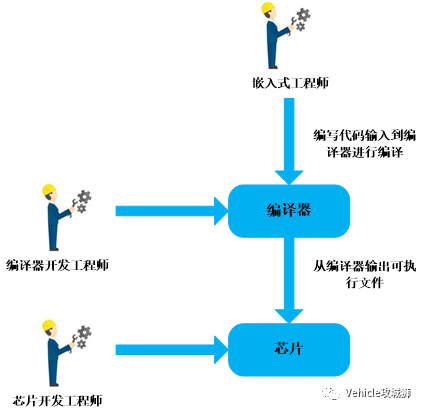

设计一款CPU的过程就好比建房子,我们建房子肯定先要以一定的建设标准和规范为前提,依据一定的工程标准不仅使建设过程有序进行更重要的是最终能被验收和被大家所接受。这也类似于我们软件开发流程,必须先有需求再有开发,否则开发的软件都没有应用的场景。因此凭空设计一款CPU,首先会不会被厂商用另说,很多相应的配套也难以支持更何谈让软件开发人员进行开发和推广了。所以指令集作为一种标准规范,用于规范芯片设计工程师及编译器开发工程师。

因为芯片与集成开发环境-IDE都遵循相同的指令集标准,所以高级语言编写的程序经指定编译器编译后能直接运行在对应的CPU上,反之则不能运行。 所以,CPU在设计之前,就需要先设计一套指令集或者说使用现成的指令集(如ARM、X86指令集)并在硬件电路上实现这些指令。CPU设计好后,还需要配套的编译器,编译器也需要参考这个指令集标准,将我们编写的C程序、C++等程序编译成CPU硬件电路支持的加减乘除、与或非等指令,我们的程序才能在CPU上运行。

4

指令集与微架构

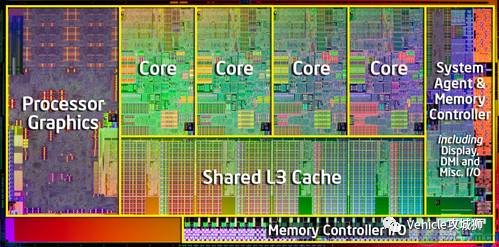

微架构是将指定指令集在处理器中如何执行实现的方法,同现实生活中解决相同问题有很多途径的原理一样:同一指令集可以有不同的微架构,因同一指令可以通过不同的电路单元或组合来实现。例如英特尔基于x86指令集的微架构就很多代:

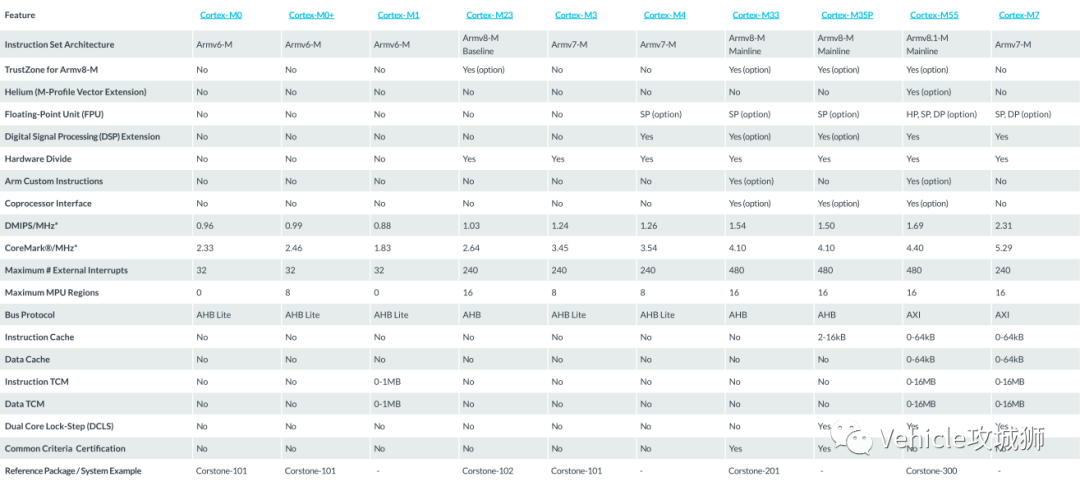

再比如ARM M系列处理器基于Armv6-M指令集所构建的M0/M1等微架构:

我们曾接触的STM32F4系列单片机就是基于Armv7-M指令集的ARM Cortex-M4内核:

不同的微架构有着不同的用途和性能,总体来说一大堆的运算单元、逻辑单元、寄存器等在各种总线和控制线的连接下组成了CPU的微架构。因此处理器架构是微架构和指令集架构的结合,指令集是处理器的语言,而微架构是具体的实现。

5

指令集分类

目前市面上存在两种指令集类型:

Reduced Instruction Set Computing (RISC) 精简指令集:比如ARM、MIPS和大火的RISC-V等。

Complex Instruction Set Computing (CISC) 复杂指令集:比如Intel、AMD的X86等。

其中x86架构主要占据传统PC市场,善于处理大数据;ARM占据移动市场,善于处理快数据;而RISC-V则依靠自己精简的优势在数据传输领域占据优势。除此之外,其他指令集架构也占据部分市场如MIPS、Power等。

无论是CISC还是RISC,除了努力巩固自己的性能优势,加强产品的性能外,还需要汲取双方产品的特色,取长补短,期望有所突破,例如英特尔逐渐开始拥抱RISC-V。不过无论如何,未来的CPU肯定在朝着高性能、低功耗的方向发展。谁能在低功耗下提供高性能,谁就有希望获得成功。

审核编辑 :李倩

-

指令集

+关注

关注

0文章

228浏览量

24237 -

微架构

+关注

关注

0文章

22浏览量

7304

原文标题:一文了解指令集和微架构

文章出处:【微信号:SAEINTL,微信公众号:SAE International】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

了解指令集和微架构

了解指令集和微架构

评论