集成电路的制造过程中,掺杂是很重要的一步。

掺杂就在芯片工艺段里面

掺杂是什么意思,硅片本身载流子浓度很低,需要导电的话,就需要有空穴或者电子,因此引入其他三五族元素,诱导出更多的空穴和电子,形成P型或者N型半导体。

掺杂定义:就是用人为的方法,将所需的杂质(如磷、硼等),以一定的方式掺入到半导体基片规定的区域内,并达到规定的数量和符合要求的分布,以达到改变材料电学性质、制作PN结、集成电路的电阻器、互联线的目的。

掺杂的主要形式:注入和扩散

提到掺杂就要有退火,热处理、其他地方也有叫淬火。

Ø退火:也叫热处理,集成电路工艺中所有的在氮气等不

活泼气氛中进行的热处理过程都可以称为退火。

Ø目的:激活杂质

消除损伤

结构释放后消除残余应力

Ø退火方式:

炉退火

快速退火

Ø扩散的定义:在一定温度下杂质原子具有一定能量,能够克服阻力进入半导体并在其中做缓慢的迁移运动。Ø形式:替代式扩散和间隙式扩散

恒定表面浓度扩散和再分布扩散

Ø替位式扩散:杂质离子占据硅原子的位:ØⅢ、Ⅴ族元素Ø一般要在很高的温度(950~1280℃)下进行Ø磷、硼、砷等在二氧化硅层中的扩散系数均远小于在硅中的扩散系数,可以利用氧化层作为杂质扩散的掩蔽层Ø间隙式扩散:杂质离子位于晶格间隙:ØNa、K、Fe、Cu、Au 等元素Ø扩散系数要比替位式扩散大6~7个数量级

扩散工艺主要参数

Ø结深:当用与衬底导电类型相反的杂质进行扩散时,在硅片内扩散杂质浓度与衬底原有杂质浓度相等的地方就形成了pn结,结距扩散表面的距离叫结深。Ø薄层电阻Rs(方块电阻)Ø表面浓度:扩散层表面的杂质浓度。

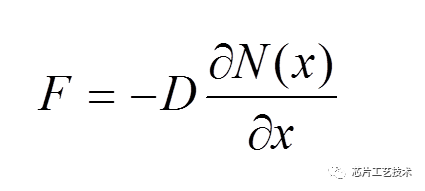

扩散的适用数学模型是Fick定律

式中:

F 为掺入量

D 为扩散率

N 每单位基底体积中掺入浓度

扩散方式

Ø液态源扩散:利用保护气体携带杂质蒸汽进入反应室,在高温下分解并与硅表面发生反应,产生杂质原子,杂质原子向硅内部扩散。Ø固态源扩散:固态源在高温下汽化、活化后与硅表面反应,杂质分子进入硅表面并向内部扩散。

液态源扩散

硼B

Ø扩散源:硼酸三甲酯,硼酸三丙酯等Ø扩散原理:硼酸三甲酯500°C分解后与硅反应,在硅片表面形成硼硅玻璃,硼原子继续向内部扩散,形成扩散层。

Ø扩散系统:N2气源、纯化、扩散源、扩散炉Ø扩散工艺:预沉积,去BSG,再分布Ø工艺条件对扩散结果的影响Ø气体流量、杂质源、温度

磷P

Ø扩散源:POCl3,PCl3,PBr3等Ø扩散原理:三氯氧磷600°C分解后与硅反应,在硅片表面形成磷硅玻璃,磷原子继续向内部扩散,形成扩散层。Ø扩散系统:O2和N2气源、纯化、扩散源、源冷却系统、扩散炉Ø扩散工艺:预沉积,去PSG,再分布

固态源扩散

Ø箱法B扩散

B2O3或BN源,石英密封箱

Ø片状BN扩散

氧气活化,氮气保护,石英管和石英

舟,预沉积和再分布

Ø片状P扩散

扩散源为偏磷酸铝和焦磷酸硅

Ø固-固扩散(乳胶源扩散)

扩散炉

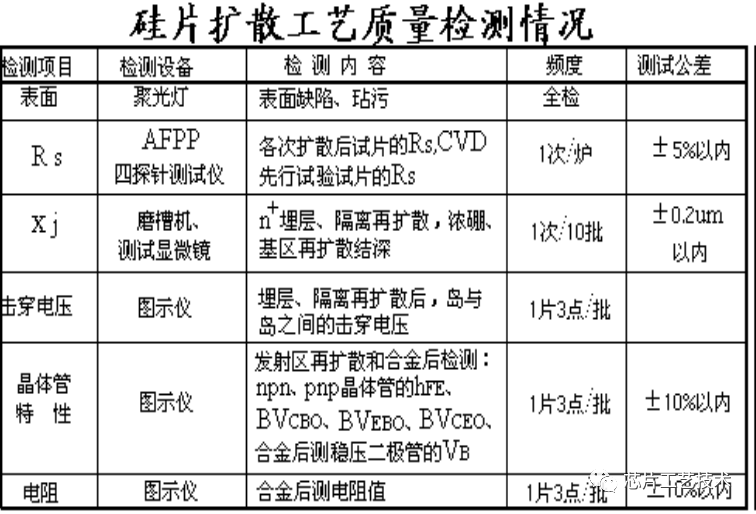

质量分析

Ø1.硅片表面不良:表面合金点;表面黑点或白雾;表面凸起物;表面氧化层颜色不一致;硅片表面滑移线或硅片弯曲;硅片表面划伤,边缘缺损,或硅片开裂等Ø2.漏电电流大:表面沾污引起的表面漏电;氧化层的缺陷破坏了氧化层在杂质扩散时的掩蔽作用和氧化层在电路中的绝缘作用而导电;硅片的缺陷引起杂质扩散时产生管道击穿。Ø3.薄层电阻偏差Ø4.器件特性异常:击穿电压异常;hFE异常;稳压二极管稳压值异常。

工艺控制

Ø污染控制:颗粒、有机物、薄膜、金属离子Ø污染来源:操作者,清洗过程,高温处理,工具Ø• 参量控制:温度,时间,气体流量(影响最大?)Ø1.温度控制:源温、硅片温度、升温降温、测温Ø2.时间:进舟出舟自动化, 试片Ø3.气体流量:流量稳定,可重复性,假片

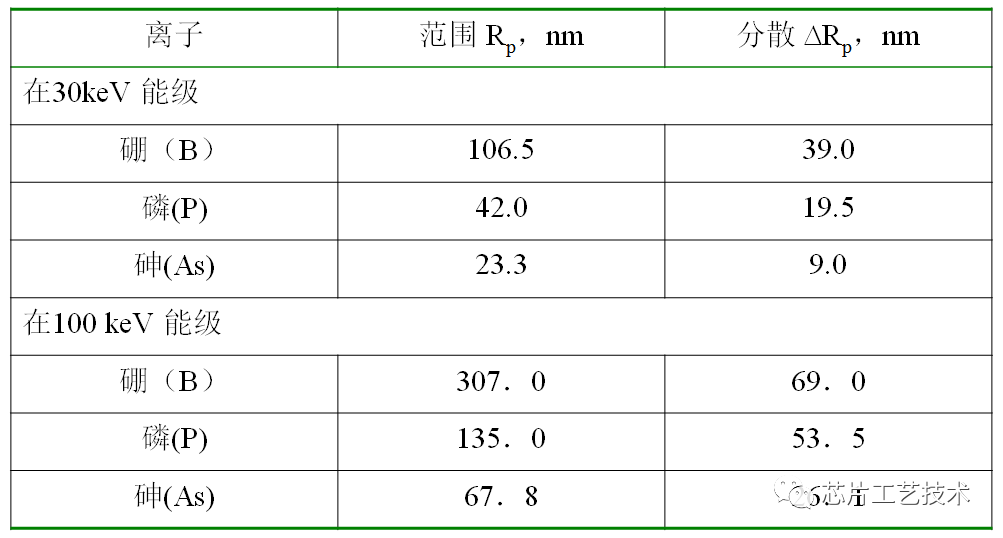

离子注入

•定义:将掺杂剂通过离子注入机的离化、加速和质量分析,成为一束由所需杂质离子组成的高能离子流而投射入晶片(俗称靶)内部,并通过逐点扫描完成整块晶片的注入•掺杂深度由注入杂质离子的能量和质量决定•掺杂浓度由注入杂质离子的数目(剂量)决定 。

离子注入的优点:

Ø掺杂的均匀性好Ø温度低:小于600℃Ø可以精确控制杂质分布Ø可以注入各种各样的元素Ø横向扩展比扩散要小得多Ø可以对化合物半导体进行掺杂。

Ø特点:横向效应小,但结深浅;杂质量可控;晶格缺陷多Ø基本原理:杂质原子经高能粒子轰击离子化后经电场加速轰击硅片表面,形成注入层Ø装置:离子源、聚焦、分析器、加速管、扫描、偏转、靶室、真空系统

硅中常用掺杂剂的离子注入

离子注入以往的文章里面介绍过,这儿就不多复习了。明天深圳光博会开始了,欢迎大家来深圳参加。明天走起遛遛

责任编辑:haq

-

芯片

+关注

关注

462文章

53534浏览量

459018 -

集成电路

+关注

关注

5446文章

12465浏览量

372674 -

工艺

+关注

关注

4文章

708浏览量

30110

原文标题:集成电路掺杂工艺

文章出处:【微信号:dingg6602,微信公众号:芯片工艺技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PDK在集成电路领域的定义、组成和作用

CMOS集成电路的基本制造工艺

泊苏定制化半导体防震基座在集成电路制造中的重要性

集成电路制造中良率损失来源及分类

集成电路的制造过程工艺

集成电路的制造过程工艺

评论