典型参数:

F工作储t=45MHz

Pd=10mW/每触发器

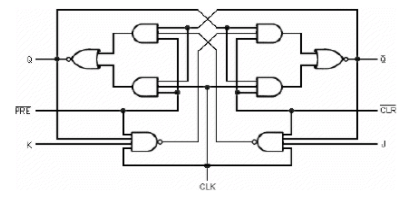

引脚图:

功能表:

H-高电平 L-低电平 x -不定 ↓=从商电平迁波到低电平

Qo=建立稳态输人条件之前的Q电平

Qo=建立稳志输入宗作之前的Q电平

这种情况是不稳定的,即当预置和清除输入回到高电平时,状态梅不能保持。

文章来源:838dz

编辑:ymf

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

引脚图

+关注

关注

31文章

112浏览量

36290 -

74LS76

+关注

关注

5文章

3浏览量

14168 -

引脚功能表

+关注

关注

0文章

5浏览量

2331

发布评论请先 登录

相关推荐

热点推荐

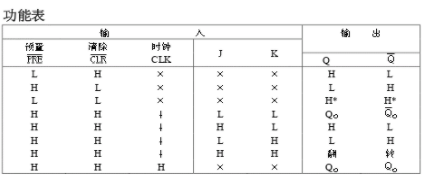

【Nordic随笔】nRF5340引脚分配问题

【Nordic随笔】nRF5340引脚问题 本文章主要说明一下nRF5340引脚问题,因为nRF5340是双核架构,所以有部分引脚是被分配到网络核的,以及有部分特殊引脚的分配 为什么发

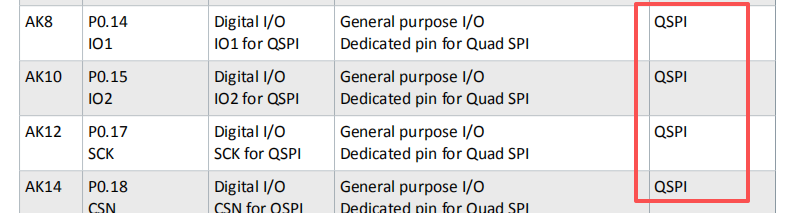

PIC16F18026/46:功能丰富的14/20引脚微控制器深度解析

Microchip Technology PIC16F18026/46 14/20引脚微控制器具有数字和模拟外设,用于成本敏感的传感器和实时控制应用。这些微控制器采用8至44引脚封装,内存范围为

新品 | CoolSiC™ MOSFET 1200V分立器件TO247-4引脚IMZA封装

新品CoolSiCMOSFET1200V分立器件TO247-4引脚IMZA封装第二代CoolSiCMOSFETG21200V/53mΩ,TO247-4引脚IMZA封装,确保安装兼容性并可轻松替换现有

请问为什么M0519引脚的某些部分在配置为GPIO功能后无法将输出控制到高电平或低电平状态?

为什么M0519引脚的某些部分在配置为GPIO功能后无法将输出控制到高电平或低电平状态?

发表于 08-27 15:00

光耦817引脚图及参数详解:电子设计中的“隔离神器”

,当LED发光时,光电晶体管会感应到光信号并导通,从而实现信号的传递。

光耦817广泛应用于电源、通信、工业控制等领域,是电子设计中不可或缺的元器件之一。

二、光耦817引脚图

光耦817通常采用4引脚

发表于 06-06 08:50

DLP4710evm lc TRIG_OUT2引脚不输出脉冲信号怎么解决?

用TRIG_OUT2引脚触发相机拍照,前几天还能根据投影同步产生触发信号,这几天再实验的时候TRIG_OUT2引脚就不受控制了,一直输出高电平。TRIG_OUT1引脚正常,能同步产生触发信号。怀疑是控制TRIG_OUT2

发表于 02-25 08:07

使用两个DLP4500,根据用户手册将第一个DLP的J14引脚的2,6分别接到第二个DLP的J11引脚的2,6引脚,为什么不起作用?

您好,我需要使用两个DLP4500,想用第一个DLP的Trigger out 触发第二个DLP的 trigger in, 根据用户手册将第一个DLP 的J14引脚的2,6分别接到第二个DLP的J11引脚的2,6引脚,但是却不起

发表于 02-24 07:59

ADS1013中的DIN和AIN0~3引脚是什么功能,ADS1286S中的IN0~7怎么用?

ADS1013中的DIN和AIN0~3引脚是什么功能,ADS1286S中的IN0~7怎么用

发表于 02-08 08:21

EE-79:采用100引脚218x处理器的主机模式EPROM引导

电子发烧友网站提供《EE-79:采用100引脚218x处理器的主机模式EPROM引导.pdf》资料免费下载

发表于 01-14 15:53

•0次下载

EE-78:配置为IDMA使用的100引脚ADSP-218x DSP上的BDMA使用

电子发烧友网站提供《EE-78:配置为IDMA使用的100引脚ADSP-218x DSP上的BDMA使用.pdf》资料免费下载

发表于 01-14 15:17

•0次下载

添加AFE031时,为什么自动生成外形就6个引脚?但是AFE031明明是48引脚的啊?

添加AFE031时,为什么自动生成外形就6个引脚?但是AFE031明明是48引脚的啊?

发表于 01-10 14:04

ADS8588S datasheet上26引脚标注为AGND,它的周围引脚全部为数字信号引脚,这里是否有误?

如图,datasheet上26引脚标注为AGND,但它的周围引脚全部为数字信号引脚,而且这个芯片上没有DGND引脚, 这里是否有误?如果无误,那这个芯片的数字地和模拟地是否需要分开

发表于 12-26 07:33

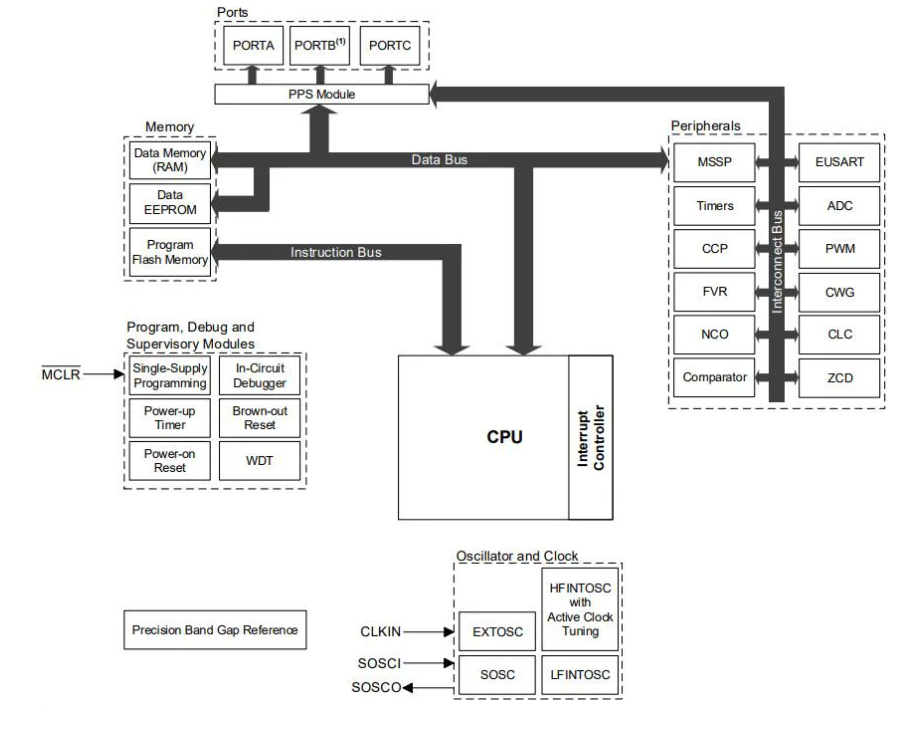

74ls76引脚图及功能表

74ls76引脚图及功能表

评论