最近使用ZYNQ做一个高速数据采集,需要访问一个ADI的高速模数采样芯片,该芯片是利用三线制实现读以及写的功能。三线制实现写通信或许大家都经常会这样用,三线制实现读/写或许有的朋友就未曾这样用过。今天就分享一下利用现成IP不写任何代码怎么实现三线制SPI。

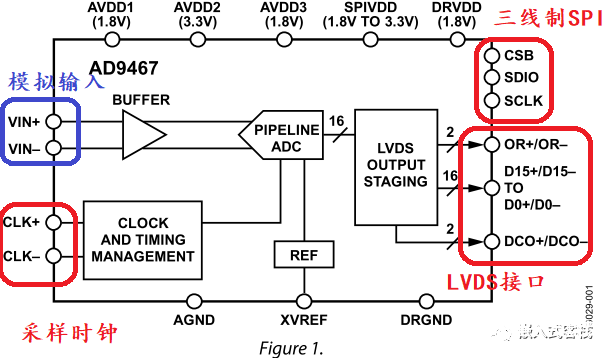

背景ADI很多芯片都采用三线制SPI进行控制,以AD9467为例,AD9467是一款 pipeline架构16位高速ADC芯片,采样率高达250MSPS。在一些复杂系统中其应用领域比较广泛:

多载波,多模式蜂窝接收机

天线阵列定位

功率放大器线性化

无线宽带通信系统

雷达系统

红外成像系统

通讯仪表系统等

从芯片框图,大致可以看出,该芯片主要由以下部分组成:

三线制SPI通信接口,实现芯片的寄存器读写控制。主要用于芯片模式配置。

LVDS接口:则负责数据的对外传输,遵循ANSI-644 标准。

CLK+/CLK-:为输入时钟,时钟之于数字芯片相当于心脏之于人,一切的动作都是由时钟驱动的。

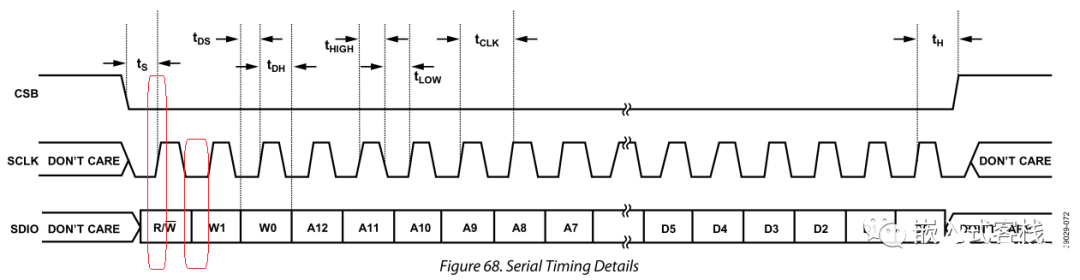

对于芯片的其他部分,不是本文介绍的重点,这里来看看其SPI的通信时序图:

结合SPI模式时序图:

在上升沿采样

下一位数据在CLK低期间变换

故,CPOL=0,CPHA=0.

另外,第一个bit用于标识本次报文你发起的是读还是写操作,这种设计是不是有点类似I2C标准中的读写位?

柳暗花明那么问题来了,我们需要做的SPI通信需要实现三线制SPI进行读以及写:

如果用单片机编程IO口去翻比较容易,但是要实现高速AD数据传输,常规的单片机就捉襟见肘了。LVDS接口的数据吞吐率很难做到。

如果使用ZYNQ内置的SPI外设也很容易,该外设很容易配成三线制模式。很不幸,外设引脚基本用掉了。不过可以考虑用EMIO把相应的脚从PL端拉出去。

如果利用ZYNQ PS端的GPIO也可以做到,也很不幸,做的板子PS端GPIO所剩无几。

利用赛灵思的AXI Quad SPI IP在PL端去实现。折腾一段时间,发现这个IP貌似不支持三线制SPI。

自己用verilog HDL写个IP挂在AXI总线上,实现Linux设备驱动,这个方案可以。可惜,比较懒,不想重新造轮子!

。。.。。.。

经过一番折腾,在ADI官方发现了一个宝藏:

https://wiki.analog.com/resources/fpga/peripherals/spi_engine

官方实现了SPI engine IP 框架:

执行模块 Execution Module:主模块,用于处理SPI引擎命令流并实现SPI总线接口逻辑

AXI接口模块:内存映射软件可访问SPI引擎命令流和/或卸载核心的接口

Offload模块:存储SPI引擎命令流,由外部事件触发执行

互连Interconnect 模块:将多个SPI Engine命令流连接到SPI Engine执行模块

其verilog HDL代码库位于:

https://github.com/analogdevicesinc/hdl.git

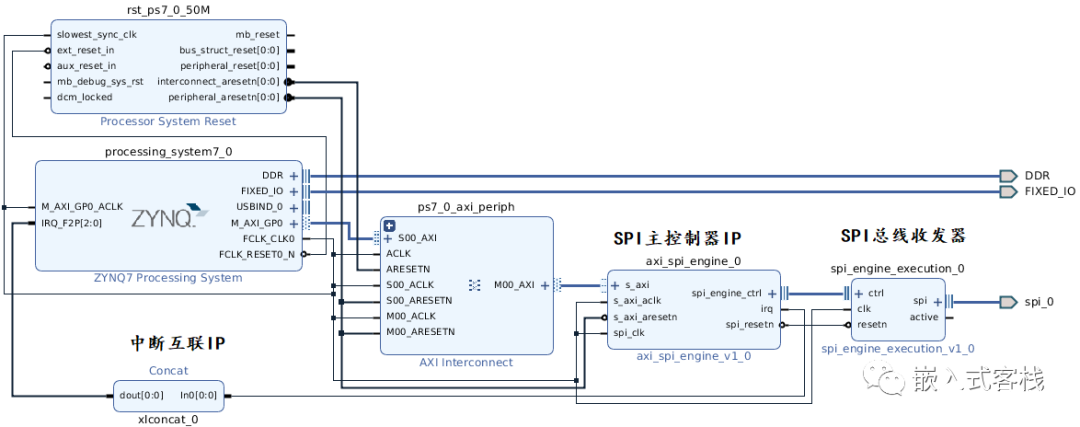

PS/PL设计下好hdl库,按照向导将库make,执行对应的tcl脚本,生成了hdl库相应所需文件。然后按照需要设计以下block设计:

将PS端的DDR以及PL所需的时钟FCLK_CLK0配置好,这里输出100MHz

从ip库里拉出来axi_spi_engine_v1_0以及spi_engine_execution_v1_0,按照上面图连好线

连好AXI接口,以及相应的复位、时钟信号等

设置需要几个片选信号,可根据需要几个从芯片可以设置多个片选信号,比如我设置2个,这样在linux设备树上就对应挂载两个设备。

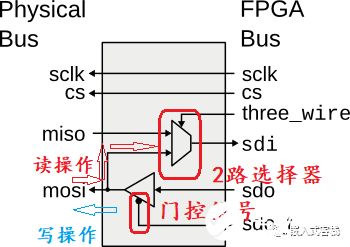

然后在顶层设计文件进行例化,这里问题来了,spi_1还是4个脚,如果就这样拉出到PL端的引脚上,还是四线制,那么该怎么改呢?

看看wiki中图以及描述,发现需要还需要在转一下:

如果是三线模式时,three_wire会变成1,这个通过AXI总线命令传过来。

sdo_t则可以控制sdo内部信号是否输出,如果门控关断则mosi脚变成高阻,可以采样外部信号,从而传入可以通过2路选择器传入sdi转而为读信号。

从而添加如下代码在顶层文件:

assign phy_sclk = spi_sclk;assign phy_cs = spi_cs;assign phy_mosi = spi_sdo_t ? 1‘bz : spi_sdo;assign spi_sdi = spi_three_wire ? phy_mosi : phy_miso;

比如,我是这样写的:

`timescale 1ns / 100ps//顶层设计文件module system_top (//DDR信号inout [14:0] ddr_addr,inout [ 2:0] ddr_ba,inout ddr_cas_n,inout ddr_ck_n,inout ddr_ck_p,inout ddr_cke,inout ddr_cs_n,inout [ 3:0] ddr_dm,inout [31:0] ddr_dq,inout [ 3:0] ddr_dqs_n,inout [ 3:0] ddr_dqs_p,inout ddr_odt,inout ddr_ras_n,inout ddr_reset_n,inout ddr_we_n,//必须的一些PS信号inout fixed_io_ddr_vrn,inout fixed_io_ddr_vrp,//54个PS MIO引脚inout [53:0] fixed_io_mio,//PS时钟引脚inout fixed_io_ps_clk,//PS上电复位信号inout fixed_io_ps_porb,//PS SRSTB信号inout fixed_io_ps_srstb,output [1:0] spi_0_cs,output spi_0_sclk,input spi_0_sdi,output spi_0_sdo,); wire ip_spi_0_cs;wire ip_spi_0_sclk;wire ip_spi_0_sdi;wire ip_spi_0_sdo;wire ip_spi_0_three_wire; wire ip_spi_0_sdo_t;assign spi_0_cs = ip_spi_0_cs;assign spi_0_sclk = ip_spi_0_sclk;//如此处理,这样引出的SPI可以兼容3线制以及4线制SPIassign spi_0_sdo = ip_spi_0_sdo_t ? 1’bz : ip_spi_0_sdo;assign ip_spi_0_sdi = ip_spi_0_three_wire ? spi_0_sdo : spi_0_sdi;//例化block设计ip_block_wrapper i_system_wrapper ( //DDR以及常规MIO、时钟、复位等信号 .DDR_addr(ddr_addr), .DDR_ba(ddr_ba), .DDR_cas_n(ddr_cas_n), .DDR_ck_n(ddr_ck_n), .DDR_ck_p(ddr_ck_p), .DDR_cke(ddr_cke), .DDR_cs_n(ddr_cs_n), .DDR_dm(ddr_dm), .DDR_dq(ddr_dq), .DDR_dqs_n(ddr_dqs_n), .DDR_dqs_p(ddr_dqs_p), .DDR_odt(ddr_odt), .DDR_ras_n(ddr_ras_n), .DDR_reset_n(ddr_reset_n), .DDR_we_n(ddr_we_n), .FIXED_IO_ddr_vrn(fixed_io_ddr_vrn), .FIXED_IO_ddr_vrp(fixed_io_ddr_vrp), .FIXED_IO_mio(fixed_io_mio), .FIXED_IO_ps_clk(fixed_io_ps_clk), .FIXED_IO_ps_porb(fixed_io_ps_porb), .FIXED_IO_ps_srstb(fixed_io_ps_srstb), //连至顶层 .spi_0_cs(ip_spi_0_cs), .spi_0_sclk(ip_spi_0_sclk), .spi_0_sdi(ip_spi_0_sdi), .spi_0_sdo(ip_spi_0_sdo), .spi_0_sdo_t(ip_spi_0_sdo_t), .spi_0_three_wire(ip_spi_0_three_wire) ); endmodule

Linux端配置首先需要配置设备树:

&axi_spi_engine_0 { status = “okay”; //配置SPI控制器匹配字段,这样会自动编译ADI 提供的SPI 控制器驱动 compatible = “adi,axi-spi-engine-1.00.a”; spi-rx-bus-width = 《1》; spi-tx-bus-width = 《1》; bits-per-word = 《8》; interrupt-parent = 《&intc》; interrupts = 《0 30 4》; num-cs = 《4》; #address-cells = 《0x1》; #size-cells = 《0x0》; ad9467_0: ad9467@0 { compatible = “adi,ad9467”; reg = 《0》; spi-max-frequency = 《500000》; #address-cells = 《1》; #size-cells = 《1》; spi-rx-bus-width = 《1》; spi-tx-bus-width = 《1》; bits-per-word = 《8》; spi-3wire; }; ad9467_1: ad9467@1 { compatible = “spidev”; reg = 《1》; spi-max-frequency = 《500000》; #address-cells = 《1》; #size-cells = 《1》; spi-rx-bus-width = 《1》; spi-tx-bus-width = 《1》; bits-per-word = 《8》; //这个字段需要使能,表示该设备是三线制 spi-3wire; }; };

配置相应的SPI控制器驱动,然后编译部署。由于该demo涉及些项目其他的技术细节,这里就不描述了,来看看疗效:

看这个波形或许会有朋友问:为啥数据发送结束,SDO/SDI复用脚波形有一个上升的渐变暂态过程,这是由于此时从端芯片从输出态转为高阻态,而主端芯片此时也是高阻态,由于线路电容效应故而会有这样一个变化过程。

总结一下利用ADI提高的IP库,不用敲一行代码可以很容易就实现了三线制SPI,香吧?该方案可以同时兼容三线制/四线制SPI,是一个成熟稳定的方案。为什么ZYNQ芯片这样一款SOC芯片以及Linux会被人喜欢,由此可见一斑。因为有大量成熟的轮子可供使用,而不必自己去造轮子。从而加速产品的研发进度,使用户可以专注于自己需要解决的应用问题。

责任编辑:haq

-

芯片

+关注

关注

446文章

47701浏览量

408841 -

驱动

+关注

关注

11文章

1716浏览量

84330 -

SPI

+关注

关注

17文章

1610浏览量

89538

发布评论请先 登录

相关推荐

FPGA设计中,对SPI进行参数化结构设计

ade7758用在三相三线制的时候,需要对寄存器COMPMODE怎么设置?

AD421是只能作为两线制输出吗?三线制可以吗?怎么接线?

AD7915的三线模式能用stm32 SPI库函数读取吗?

AD7685用示波器抓取DEMO板的SDO,CONV,SLK三线的电平情况,发现CONV并没有一段转换时间的原因?

AD5412非标的三线制SPI如何与标准的四线制SPI通信?

ad4001的三线turbo模式怎么理解?

如何利用现成IP不写代码实现三线制SPI?

如何利用现成IP不写代码实现三线制SPI?

评论